# Am25LS14A

8-Bit Serial/Parallel Two's Complement Multiplier

### DISTINCTIVE CHARACTERISTICS

- Two's complement multiplication without correction

- Magnitude only multiplication

- Cascadable for any number of bits

- 8-bit parallel multiplicand data input

- 50MHz minimum clock frequency

- Second sourced by T.I. as the SN54LS/74LS384

IMOX<sup>TM</sup> process with ECL internal

### GENERAL DESCRIPTION

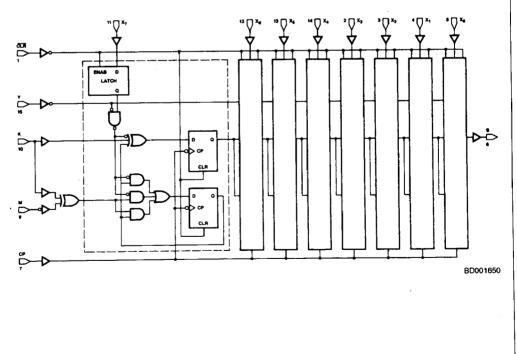

The Am25LS14A is an 8-bit by 1-bit sequential logic element that performs digital multiplication of two numbers represented in two's complement form to produce a two's complement product without correction. The device accepts an 8-bit multiplicand (X input) and stores this data in eight internal latches. The X latches are controlled via the clear input, When the clear input is LOW, all internal flipflops are cleared and the X latches are opened to accept new multiplicand data. When the clear input is HIGH, the latches are closed and are insensitive to X input changes.

The multiplier word data is passed by the Y input in a serial bit stream - least significant bit first. The product is clocked out the S output least significant bit first.

The multiplication of an m-bit multiplicand by an n-bit multiplier results in an m + n bit product. The Am25LS14A must be clocked for m + n clock cycles to produce this two's complement product. Likewise, the n-bit multiplier (Yinput) sign bit data must be extended for the remaining mbits to complete the multiplication cycle.

The device also contains a K input so that devices can be cascaded for longer length X words. The sum (S) output of one device is connected to the K input of the succeeding device when cascading. Likewise, a mode input (M) is used to indicate which device contains the most significant bit. The mode input is wired HIGH or LOW depending on the position of the 8-bit slice in the total X word length.

# **BLOCK DIAGRAM**

IMOX is a trademark of Advanced Micro Devices.

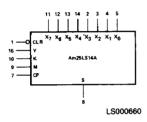

# CONNECTION DIAGRAM Top View

Note: Pin 1 is marked for orientation

#### LOGIC SYMBOL

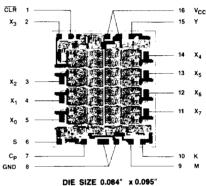

# METALLIZATION AND PAD LAYOUT

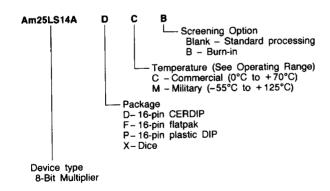

#### ORDERING INFORMATION

AMD products are available in several packages and operating ranges. The order number is formed by a combination of the following: Device number, speed option (if applicable), package type, operating range and screening option (if desired).

| Valid Co  | mbinations                   |

|-----------|------------------------------|

| Am25LS14A | PC<br>DC, DM<br>FM<br>XC, XM |

#### **Valid Combinations**

Consult the AMD sales office in your area to determine if a device is currently available in the combination you wish.

#### PIN DESCRIPTION

| Pin No. | Name                                                                                                                                           | 1/0 | Description                                                                                                                                                                                                                               |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|         | X <sub>0</sub> , X <sub>1</sub> ,<br>X <sub>2</sub> , X <sub>3</sub> ,<br>X <sub>4</sub> , X <sub>5</sub> ,<br>X <sub>6</sub> , X <sub>7</sub> |     | The eight data inputs for the multiplicand (X) data.                                                                                                                                                                                      |  |  |  |  |

| 15      | Υ                                                                                                                                              | T   | The serial input for the multiplier (Y) data-least significant bit first.                                                                                                                                                                 |  |  |  |  |

| 6       | s o                                                                                                                                            |     | The serial output for the product of X ● Y—least significant bit first.                                                                                                                                                                   |  |  |  |  |

| 7       | CP I Clo                                                                                                                                       |     | Clock. The buffered common clock input for the serial/parallel multiplier. All functions occur on the LOW-to-HIGH transition of the clock.                                                                                                |  |  |  |  |

| 1       | CLR                                                                                                                                            | ī   | Clear. The buffered common clear for all flip-flops within the device. When the clear is LOW all flip-flops are cleared. Also the buffered X-input latch enable. When the clear input is LOW, the X latches will accept new X-input data. |  |  |  |  |

| 10      | К                                                                                                                                              | 1   | The sum expansion input to the serial/parallel multiplier. Allows for cascading devices.                                                                                                                                                  |  |  |  |  |

| 9       | м                                                                                                                                              | 1   | The mode control input for the most significant bit of the multiplier. It is used in conjunction with cascading to determine the most significant bit.                                                                                    |  |  |  |  |

#### **FUNCTION TABLE**

|     |    | INP            | JTS |    |   | INTERNAL | OUTPUT |                                                                  |  |  |

|-----|----|----------------|-----|----|---|----------|--------|------------------------------------------------------------------|--|--|

| CLR | СР | K              | М   | Χı | Y | Y-1      | S      | FUNCTION                                                         |  |  |

| _   | _  | L              | L   | _  | - | _        | -      | Most Significant Multiplier Device                               |  |  |

| _   | -  | cs             | Н   | _  | - | -        | -      | Devices Cascaded in Multiplier String                            |  |  |

| L   | _  | -              | _   | ОР | - | L        | L      | Load New Multiplicand and Clear Internal Sum and Ca<br>Registers |  |  |

| Н   | _  | _              | _   | -  | _ | -        | _      | Device Enabled                                                   |  |  |

| Н   | 1  | -              | -   | _  | L | L        | AR     | Shift Sum Register                                               |  |  |

| Н   | Ť  | _              | -   | -  | L | Н        | AŘ     | Add Multiplicand to Sum Register and Shift                       |  |  |

| Н   | †  | <del>  -</del> | _   | -  | Н | L        | AR     | Subtract Multiplicand from Sum Register and Shift                |  |  |

| н   | 1  |                |     |    | Н | Н        | AR     | Shift Sum Register                                               |  |  |

- H = HIGH

- L = LOW

- = LOW-to-HIGH transition

- CS = Connected to S output of higher order device

- $OP = X_i$  latches open for new data (i = 0, 7)

- AR = Output as required

### **DEFINITION OF STANDARD TERMS**

- H HIGH, applying to a HIGH voltage level.

- L LOW, applying to a LOW voltage level.

- I Input.

- O Output.

- Negative Current Current flowing out of the device.

- Positive Current Current flowing into the device.

- IIL LOW-level input current with a specified LOW-level voltage applied.

- I<sub>IH</sub> HIGH-level input current with a specified HIGH-level voltage applied.

- IOL LOW-level output current.

- IOH HIGH-level output current.

- Isc Output short-circuit source current.

- ICC The supply current drawn by the device from the

- V<sub>CC</sub> power supply.

- VIL Logic LOW input voltage.

- VIH Logic HIGH input voltage.

- VOL LOW-level output voltage with IOL applied.

- VOH HIGH-level output voltage with IOH applied.

#### **APPLICATIONS**

See also Digital Signal Processing Applications Section for more information.

AF001120

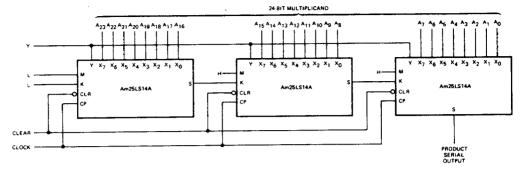

Basic 24-Bit Serial/Parallel Connection

AF001130

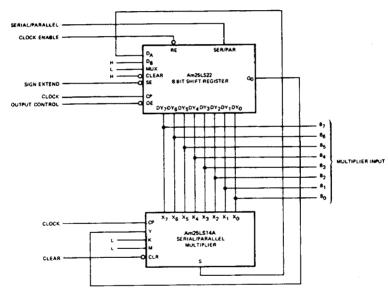

8-Bit by 8-Bit Multiplier, Bus Organized, with 8-Bit Truncated Product

## ABSOLUTE MAXIMUM RATINGS

| Storage Temperature65°C to +150°C              |  |

|------------------------------------------------|--|

| (Ambient) Temperature Under Bias55°C to +125°C |  |

| Supply Voltage to Ground Potential             |  |

| Continuous0.5V to +7.0V                        |  |

| DC Voltage Applied to Outputs For              |  |

| High Output State0.5V to +V <sub>CC</sub> max  |  |

| DC Input Voltage0.5V to +5.5V                  |  |

| DC Output Current, Into Outputs                |  |

| DC Input Current30mA to +5.0mA                 |  |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

## **OPERATING RANGES**

: 1 (O) D-: do---

| Commercial (C) Devices                  |                          |

|-----------------------------------------|--------------------------|

| Temperature                             | 0°C to +70°C             |

| Supply Voltage                          | + 4.75V to + 5.25V       |

| Military (M) Devices                    |                          |

| Temperature                             | – 55°C to + 125°C        |

| Supply Voltage                          | + 4.5V to + 5.5V         |

| Operating ranges define those limits of | over which the function- |

| ality of the device is guaranteed.      |                          |

# DC CHARACTERISTICS over operating range unless otherwise specified

| Parameters      | Description                              | Test Conditions                                     | Min                     | Typ<br>(Note 1) | Max      | Units                                   |       |

|-----------------|------------------------------------------|-----------------------------------------------------|-------------------------|-----------------|----------|-----------------------------------------|-------|

|                 |                                          | V <sub>CC</sub> = MIN., I <sub>OH</sub> = -1.0mA    | MIL                     | 2.5             | 3.4      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | Voits |

| Voн             | Output HiGH Voltage                      | VIN = VIH or VIL                                    | COM'L                   | 2.7             | 3.4      |                                         | Vons  |

|                 |                                          | V <sub>CC</sub> = MIN.                              | I <sub>OL</sub> = 8.0mA |                 |          | 0.4                                     | Volts |

| V <sub>OL</sub> | Output LOW Voltage                       | VIN = VIH or VIL                                    | I <sub>OL</sub> = 12mA  |                 |          | 0.45                                    | VOR   |

| ViH             | Input HIGH Level                         | Guaranteed input logical HIC voltage for all inputs | 2.0                     |                 |          | Volt                                    |       |

| VIL             | Input LOW Level                          | Guaranteed input logical LO voltage for all inputs  | W                       |                 | -        | 0.8                                     | Volt  |

| Vi              | Input Clamp Voltage                      | V <sub>CC</sub> = MIN., I <sub>IN</sub> = -18mA     |                         |                 |          | -1.2                                    | Volt  |

| <u> </u>        | Input LOW Current                        | V <sub>CC</sub> = MAX., V <sub>IN</sub> = 0.4V      | X, M                    |                 |          | -0.48                                   | mA    |

|                 |                                          |                                                     | K, CLR                  |                 |          | -1.2                                    |       |

| կլ              |                                          |                                                     | CP                      |                 |          | - 1.6                                   |       |

|                 |                                          |                                                     | Υ                       |                 |          | -3.2                                    |       |

|                 | Input HIGH Current                       | V <sub>CC</sub> = MAX., V <sub>IN</sub> = 2.7V      | X, M                    |                 |          | 20                                      | μΑ    |

|                 |                                          |                                                     | K, CLR                  |                 | <u> </u> | 30                                      |       |

| III             |                                          |                                                     | СР                      |                 |          | 40                                      |       |

|                 |                                          |                                                     | Y                       |                 |          | 80                                      |       |

| lı              | Input HIGH Current                       | V <sub>CC</sub> = MAX., V <sub>IN</sub> = 5.5V      |                         |                 |          | 1.0                                     | m/    |

| Isc             | Output Short Circuit Current<br>(Note 3) | V <sub>CC</sub> = MAX.                              |                         | -15             |          | -85                                     | m/    |

|                 | Power Supply Current                     | V <sub>CC</sub> = MAX.                              |                         | 45              | 65       | m/                                      |       |

## SWITCHING CHARACTERISTICS (T<sub>A</sub> = +25°C, V<sub>CC</sub> = 5.0V)

| Parameters                | Description                          | Test Conditions                 | Min  | Тур | Max | Units |

|---------------------------|--------------------------------------|---------------------------------|------|-----|-----|-------|

| tpLH                      |                                      |                                 |      | 8   | 14  | ns    |

|                           | Clock to Output                      |                                 |      | 10  | 18  |       |

| tphL                      | Clear to Output                      |                                 |      | 9   | 17  | ns    |

| tPHL                      | Clear to Cutput                      |                                 | 15   |     |     | ns    |

| t <sub>s</sub>            | Y to Clock                           |                                 | 0    |     |     |       |

| th                        |                                      | $C_L = 15pF$ $R_L = 2.0k\Omega$ | 15   |     |     | ns    |

| t <sub>s</sub>            | K to Clock                           |                                 | 0    |     |     |       |

| t <sub>s</sub>            |                                      |                                 | 13   |     |     | ns    |

|                           | X <sub>i</sub> to Clear              |                                 | 0    |     |     |       |

| th                        | Clock (HIGH)                         |                                 | 10   |     |     | ns    |

| t <sub>pw</sub>           | Clock (LOW)                          |                                 | 10   |     |     | 110   |

| t <sub>pw</sub>           | Clear Pulse Width                    | !                               | 10   |     |     | ns    |

| t <sub>s</sub>            | Clear Recovery Time (Inactive State) |                                 | 5    |     |     | ns    |

| f <sub>max</sub> (Note 1) | Maximum Clock Frequency              |                                 | (50) | 60  |     | MHz   |

Note 1: Per industry convention, f<sub>max</sub> is the worst case value of the maximum device operating frequency with no constraints on t<sub>f</sub>, t<sub>f</sub>, pulse width or duty cycle.

# SWITCHING CHARACTERISTICS over operating range unless otherwise specified\*

| Parameters                |                                         | Test Conditions                                 | Am25LS COMMERCIAL |     | Am25LS MILITARY |      |       |  |

|---------------------------|-----------------------------------------|-------------------------------------------------|-------------------|-----|-----------------|------|-------|--|

|                           | Description                             |                                                 | Min               | Max | Min             | Max  | Units |  |

| t <sub>PLH</sub>          |                                         |                                                 |                   | 18  |                 | 20   |       |  |

| PHL                       | Clock to Output                         | 1                                               |                   | 22  |                 | 25   | ns    |  |

| tPHL                      | Clear to Output                         | <b>⊣ !</b>                                      |                   | 22  |                 | 25 . | ns    |  |

| ls                        |                                         | C <sub>L</sub> = 50pF<br>R <sub>L</sub> = 2.0kΩ | 22                |     | 25              |      | ns    |  |

| th                        | Y to Clock                              |                                                 | 0                 |     | 0               |      |       |  |

|                           |                                         |                                                 | 20                |     | 22              |      | ns    |  |

| ts<br>tn                  | K to Clock                              |                                                 | 0                 |     | 0               |      |       |  |

|                           |                                         |                                                 | 20                |     | 22              |      |       |  |

| ls                        | X <sub>i</sub> to Clear                 |                                                 | 0                 |     | 0               |      | ns    |  |

| חי                        | Clock (HIGH)                            |                                                 | 10                |     | 10              |      |       |  |

| t <sub>pw</sub>           | Clock (LOW)                             |                                                 | 10                |     | 10              |      | ns    |  |

| t <sub>pw</sub>           | Clear Pulse Width                       |                                                 | 10                |     | 10              |      | ns    |  |

| t <sub>s</sub>            | Clear Recovery Time<br>(Inactive State) | 1                                               | .5                |     | .5              |      | ns    |  |

| f <sub>max</sub> (Note 1) | Maximum Clock Frequency                 | 7                                               | 50                |     | 50              | /    | MHz   |  |

<sup>\*</sup>AC performance over the operating temperature range is guaranteed by testing defined in Group A, Subgroup 9

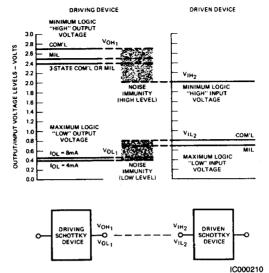

# LOW CURRENT SCHOTTKY INPUT/OUTPUT CURRENT INTERFACE CONDITIONS

Note: Refer to Electrical Characteristics for measure currents.

## INPUT/OUTPUT INTERFACE CONDITIONS

Note: Actual current flow direction shown.