- ±1% Reference Over Full Operating Temperature Range

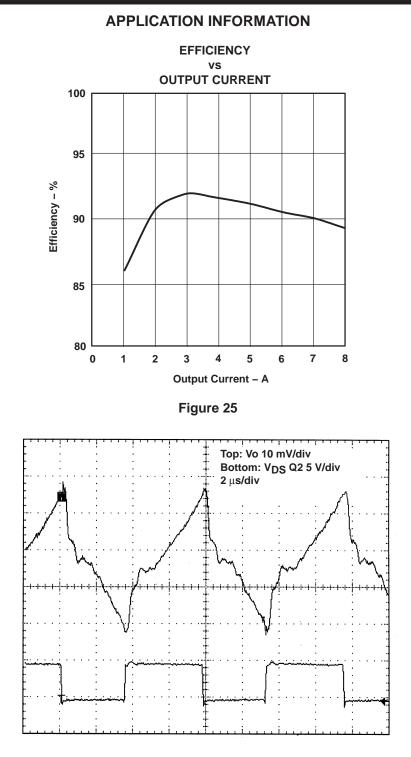

- Synchronous Rectifier Driver for >90% Efficiency

- Fixed Output Voltage Options of 1.5 V, 1.8 V, 2.5 V, and 3.3 V

- User-Selectable Hysteretic-Type Control

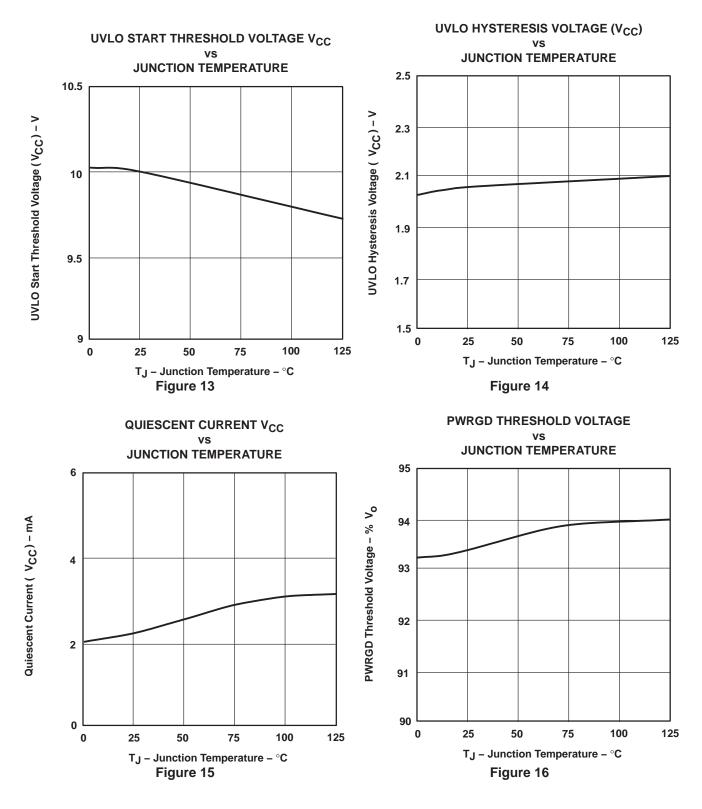

- Low Supply Current ... 3 mA Typ

- 11.4-V to 13-V Input Voltage Range, V<sub>CC</sub>

- Power Good Output

- Programmable Soft-Start

- Overvoltage/Overcurrent Protection

- Active Deadtime Control

#### (TOP VIEW) 10 28 D PWRGD 2 27 AGND2 🎞 26 OCP IT 3 25 VHYST I 4 VREFB 5 24 D NC VSENSE 6 23 22 ANAGND 7 INHIBIT 21 SLOWST IOUTLO 8 BIAS 🗖 20 LOSENSE 9 LODRV 19 HISENSE 10 18 D BOOTLO 11 DRVGND 12 17 LOWDR 13 16 🔲 ВООТ DRV 🗖 14 15

PWP PACKAGE

SLVS177B - SEPTEMBER 1998 - REVISED JULY 2000

#### description

NC – No internal connection

The TPS5615 family of synchronous-buck regulator controllers provides an accurate supply voltage to DSPs. The output voltage is internally set by a resistive divider with an accuracy of 1% over the full operating temperature range. A hysteretic controller with user-selectable hysteresis is used to dramatically reduce overshoot and undershoot caused by load transients. Propagation delay from the comparator inputs to the output drivers is less than 250 ns. Overcurrent shutdown and crossover protection for the output drivers combine to eliminate destructive faults in the output FETs. PWRGD monitors the output voltage and pulls the open-collector output low when the output drops below 93% of the nominal output voltage. An overvoltage circuit disables the output drivers if the output voltage rises 15% above the nominal value. The inhibit pin can be used to control power sequencing. Inhibit and undervoltage lockout assures that the 12-V supply voltage and system supply voltage (5 V or 3.3 V) are within proper operating limits before the controller starts. The output driver circuits include 2-A drivers with internal 8-V gate-voltage regulators that can easily provide sufficient power for today's high-powered DSPs. The high-side driver can be configured either as a ground-referenced driver or as a floating bootstrap driver. The TPS5615 family is available in a 28-pin TSSOP PowerPad<sup>™</sup> package. It operates over a junction temperature range of 0°C to 125°C.

|              |                | PACKAGE                     |

|--------------|----------------|-----------------------------|

| ТJ           | OUTPUT VOLTAGE | TSSOP <sup>†</sup><br>(PWP) |

| 0°C to 125°C | 1.5 V          | TPS5615PWP                  |

|              | 1.8 V          | TPS5618PWP                  |

|              | 2.5 V          | TPS5625PWP                  |

|              | 3.3 V          | TPS5633PWP                  |

#### AVAILABLE OPTIONS

<sup>†</sup>The PWP package is availble taped and reeled. Add R suffix to device type (e.g., TPS5615PWPR).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

SLVS177B - SEPTEMBER 1998 - REVISED JULY 2000

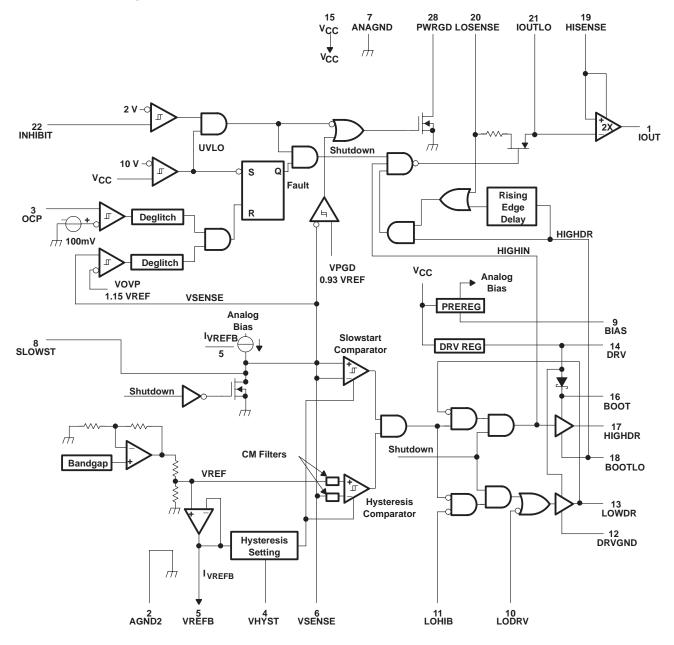

### functional block diagram

SLVS177B - SEPTEMBER 1998 - REVISED JULY 2000

### **Terminal Functions**

| TERMIN  | IAL   |     |                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|-------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | NO.   | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                            |

| AGND2   | 2     |     | Analog ground (must be connected).                                                                                                                                                                                                                                                                                                                                                     |

| ANAGND  | 7     |     | Analog ground                                                                                                                                                                                                                                                                                                                                                                          |

| BIAS    | 9     |     | Analog bias pin. A 1-μF capacitor should be connected from BIAS to ANAGND.                                                                                                                                                                                                                                                                                                             |

| BOOT    | 16    |     | Bootstrap. A 1-μF capacitor should be connected from BOOT to BOOTLO.                                                                                                                                                                                                                                                                                                                   |

| BOOTLO  | 18    |     | Bootstrap low. Connect to the junction of the high-side and low-side FETs for floating drive configuration. Connect to PGND for ground-reference drive configuration.                                                                                                                                                                                                                  |

| DRV     | 14    |     | Drive regulator for the FET drivers. A 1- $\mu$ F capacitor should be connected from DRV to DRVGND.                                                                                                                                                                                                                                                                                    |

| DRVGND  | 12    |     | Drive ground. Ground for FET drivers. Connect to FET PWRGND.                                                                                                                                                                                                                                                                                                                           |

| HIGHDR  | 17    |     | High drive. Output drive to high-side power switching FETs.                                                                                                                                                                                                                                                                                                                            |

| HISENSE | 19    |     | High current sense. For current sensing across high-side FETs, connect to the drain of the high-side FETs; for optional current sensing scheme, connect to power supply side of current-sense resistor placed in series with high-side FET drain.                                                                                                                                      |

| INHIBIT | 22    |     | Disables the drive signals to the MOSFET drivers. Also serves as UVLO for system logic supply (3.3 V or 5 V). An external pullup resistor should be connected to system-logic supply.                                                                                                                                                                                                  |

| IOUT    | 1     |     | Current out. Output voltage on this terminal is proportional to the load current as measured across the $R_{ds(on)}$ of the high side FET. The voltage on this terminal equals $2 \times R_{DS(ON)} \times IOUT$ . In applications where very accurate current-sensing is required, a sense resistor should be connected between the input supply and the drain of the high-side FETs. |

| IOUTLO  | 21    |     | Current sense low output. This is the voltage on the LOSENSE terminal when the high-side FETs are on. A ceramic capacitor (between 0.033 $\mu$ F and 0.1 $\mu$ F) should be connected from IOUTLO to HISENSE to hold the sensed voltage.                                                                                                                                               |

| LODRV   | 10    |     | Low drive enable. Normally tied to 5 V. To configure the low-side FET as a crowbar, pull LODRV low.                                                                                                                                                                                                                                                                                    |

| LOHIB   | 11    |     | Low side inhibit. Connect to the junction of the high- and low-side FETs to control the anti-cross-<br>conduction and eliminate shoot-through current. Disabled when configured in crowbar mode.                                                                                                                                                                                       |

| LOSENSE | 20    |     | Low current sense. For current sensing across high-side FETs, connect to the source of the high-side FETs; for optional current sensing scheme, connect to high-side FET drain side of current-sense resistor placed in series with high-side FET drain.                                                                                                                               |

| LOWDR   | 13    |     | Low drive. Output drive to synchronous rectifier FETs.                                                                                                                                                                                                                                                                                                                                 |

| NC      | 23–27 |     | No connect                                                                                                                                                                                                                                                                                                                                                                             |

| OCP     | 3     |     | Over current protection. Current limit trip point is set with a resistor divider between IOUT and ANAGND.                                                                                                                                                                                                                                                                              |

| PWRGD   | 28    |     | Power good. PWRGD signal goes high when output voltage is within 7% of voltage setpoint. Open-drain output.                                                                                                                                                                                                                                                                            |

| SLOWST  | 8     |     | Slow Start (soft start). A capacitor form SLOWST to ANAGND sets the slowstart time.<br>Slowstart current = $I_{VREFB}/5$                                                                                                                                                                                                                                                               |

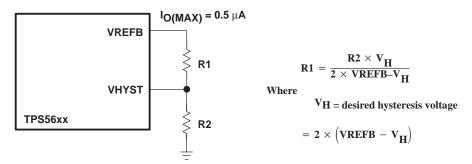

| VHYST   | 4     |     | Hysteresis set input. The hysteresis is set with a resistor divider from VREFB to ANAGND.<br>Hysteresis = $2 \times (VREFB - VHYST)$                                                                                                                                                                                                                                                   |

| VCC     | 15    |     | 12-V supply. A 1- $\mu$ F capacitor should be connected from V <sub>CC</sub> to DRVGND.                                                                                                                                                                                                                                                                                                |

| VREFB   | 5     |     | Buffered reference voltage                                                                                                                                                                                                                                                                                                                                                             |

| VSENSE  | 6     |     | Voltage sense Input. To be connected from converter output voltage bus to sense and control output voltage.<br>It is recommended that a RC low-pass filter be connected at this pin to filter noise.                                                                                                                                                                                   |

SLVS177B - SEPTEMBER 1998 - REVISED JULY 2000

### detailed description

### Vref

The reference voltage section consists of a temperature-compensated bandgap reference and a resistive divider that sets the output voltage option. The output voltage, VREF, is within 1% of the nominal setting over the full junction temperature range of 0°C to 125°C, and a  $V_{CC}$  supply voltage range of 11.4 V to 12.6 V. The output of the reference network is indirectly brought out through a buffer to the VREFB pin. The voltage on this pin will be within 2% of VREF. It is not recommended to drive loads with VREFB, other than setting the hysteresis of the hysteretic comparator, because the current drawn from VREFB sets the charging current for the slowstart capacitor. Refer to the *slowstart* section for additional information.

#### hysteretic comparator

The hysteretic comparator regulates the output voltage of the synchronous-buck converter. The hysteresis is set by 2 external resistors and is centered on VREF. The 2 external resistors form a resistor divider from VREFB to ANAGND, with the output voltage connecting to the VHYST pin. The hysteresis of the propagation delay from the comparator inputs to the driver outputs is 250 ns (maximum). The maximum hysteresis setting is 60 mV.

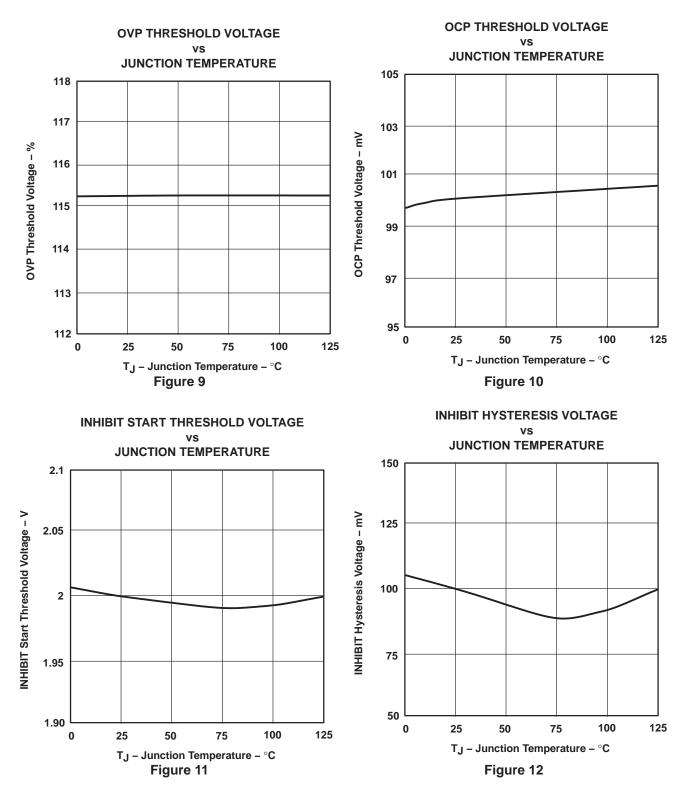

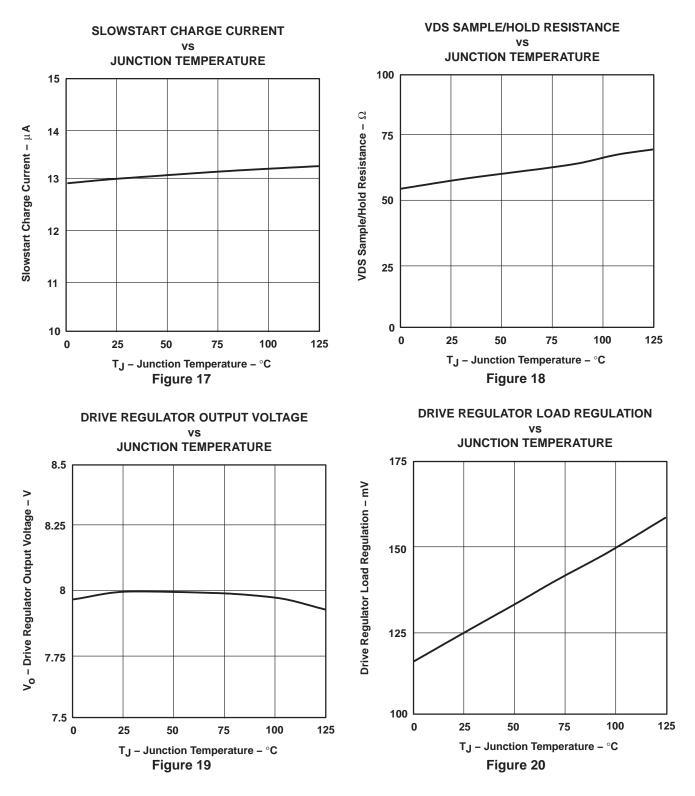

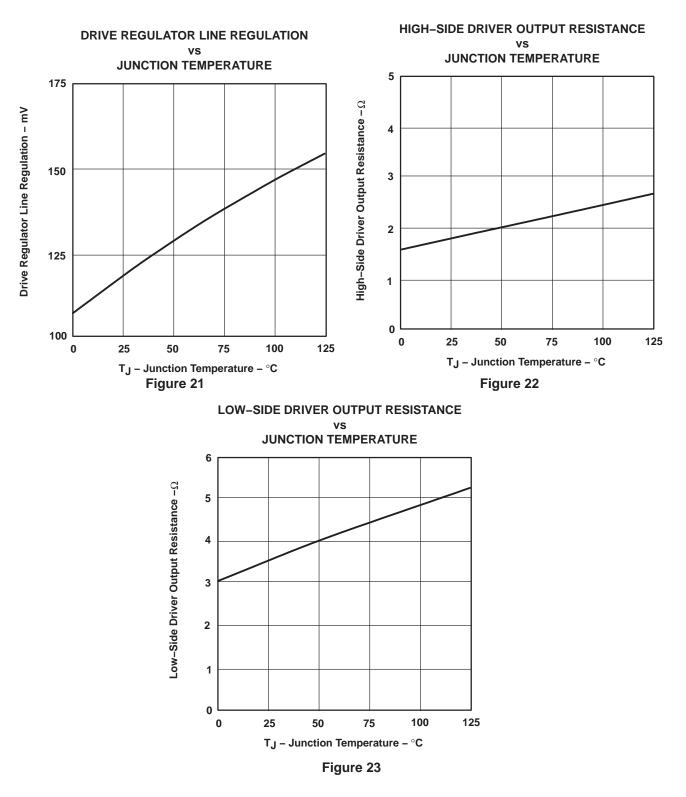

#### low-side driver

The low-side driver is designed to drive low- $R_{ds(on)}$  n-channel MOSFETs. The current rating of the driver is 2 A, source or sink. The bias to the low-side driver is internally connected to the DRV regulator.

### high-side driver

The high-side driver is designed to drive low- $R_{ds(on)}$  n-channel MOSFETs. The current rating of the driver is 2 A, source or sink. The high-side driver can be configured either as a ground-referenced driver or as a floating bootstrap driver. When configured as a floating driver, the bias voltage to the driver is developed from the DRV regulator. The internal bootstrap diode, connected between the DRV and BOOT pins, is a Schottky for improved drive efficiency. The maximum voltage that can be applied between BOOT and DRVGND is 30 V. The driver can be referenced to ground by connecting BOOTLO to DRVGND, and connecting BOOT to either DRV or V<sub>CC</sub>.

#### deadtime control

Deadtime control prevents shoot-through current from flowing through the main power FETs during switching transitions by actively controlling the turn-on times of the MOSFET drivers. The high-side driver is not allowed to turn on until the gate-drive voltage to the low-side FET is below 2 V; the low-side driver is not allowed to turn on until the voltage at the junction of the 2 FETs (Vphase) is below 2 V.

SLVS177B - SEPTEMBER 1998 - REVISED JULY 2000

٧p

IOUT

OCP

HIGHDR

2 \* VS

R1

**R2**

Ş

÷

### detailed description (continued)

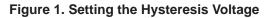

### current sensing

Current sensing is achieved by sampling and holding the voltage across the high-side power FET while the high-side FET is on. The sampling network consists of an internal 60- $\Omega$  switch and an external ceramic hold capacitor. Recommended value of the hold capacitor is between 0.033 µF and 0.1 µF. The actual value should give a time constant (60  $\Omega \times C_H$ ) greater than the FET on time. Internal logic controls the turn-on and turn-off of the sample/hold switch such that the switch does not turn on until the Vphase voltage transitions high, and the switch turns off when the input to the high-side driver goes low. Thus sampling will occur only when the high side FET is conducting current. The voltage on the IOUT pin equals 2 times the sensed high-side voltage. In applications where a higher accuracy in current-sensing is required, a sense resistor can be placed in series with the high-side FET and the voltage across the sense resistor can be sampled by the current sensing circuit. See Figures 2 and 3.

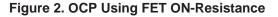

#### overcurrent protection

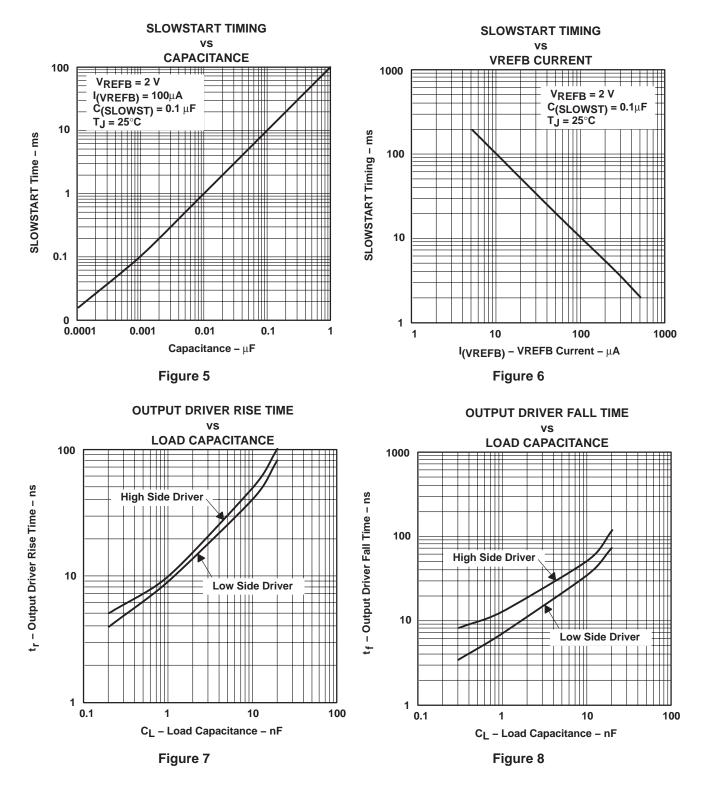

The overcurrent protection (OCP) circuit monitors the current through the high-side FET. The overcurrent threshold is adjustable with an external resistor divider between IOUT and ANAGND, with the divider voltage connected to OCP. If the voltage on OCP (VS) exceeds 100 mV, then a fault latch is set and the output drivers are turned off. The latch will remain set until V<sub>CC</sub> goes below the undervoltage lockout value. A 3-µs deglitch timer is included for noise immunity. The OCP circuit is also designed to protect the high-side power FET against a short-to-ground fault on the terminal common to both power FETs (Vphase).

Figure 3. Precision OCP Using External Resistor

### inhibit

INHIBIT is a TTL-compatible digital input used to enable the controller. When INHIBIT is low, the output drivers are low and the slowstart capacitor is discharged. When INHIBIT goes high, the short across the slowstart capacitor is released and normal converter operation begins. When the system-logic supply is connected to INHIBIT, it also controls power sequencing by locking out controller operation until the system-logic supply exceeds the input threshold voltage of the inhibit circuit. Thus the 12-V supply and the system-logic supply (either 5 V or 3.3 V) must be above UVLO thresholds before the controller is allowed to start up. The INHIBIT comparator start threshold is 2.1 V and the hysteresis is 100 mV.

SLVS177B – SEPTEMBER 1998 – REVISED JULY 2000

### detailed description (continued)

Figure 4. Input Undervoltage Lockout Circuit Using INHIBIT

### V<sub>CC</sub> undervoltage lockout (UVLO)

The undervoltage lockout circuit disables the controller while the V<sub>CC</sub> supply is below the 10-V start threshold during power up. While the controller is disabled, the output drivers will be low and the slowstart capacitor will be shorted. When V<sub>CC</sub> exceeds the start threshold, the short across the slowstart capacitor is released and normal converter operation begins. There is a 2-V hysteresis in the undervoltage lockout circuit for noise immunity.

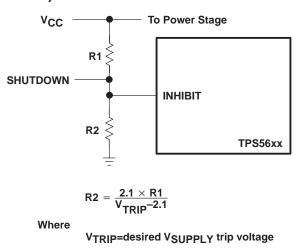

#### slowstart

The slowstart circuit controls the rate at which V<sub>O</sub> powers up. A capacitor is connected between SLOWSST and ANAGND and is charged by an internal current source. The slowstart charging current is determined by the following equation:

$$I_{\text{SLOWSTART}} = \frac{I(\text{VREFB})}{5}$$

where I(VREFB) is the current flowing out of VREFB. It is recommended that no additional loads be connected to VREFB, other than the resistor divider for setting the hysteresis voltage. The maximum current that can be sourced by the VREFB circuit is  $500 \ \mu$ A. The slowstart time is set by:

$^{t}$ SLOWSTART = 5 ×  $^{C}$ SLOWST ×  $^{R}$ VREFB

where R<sub>VREFB</sub> is the total external resistance from VREFB to ANAGND.

#### power good

The power good circuit monitors for an undervoltage condition on  $V_O$ . If  $V_O$  is 7% below  $V_{REF}$ , then PWRGD is pulled low. PWRGD is an open-drain output.

#### overvoltage protection

The overvoltage protection (OVP) circuit monitors V<sub>O</sub> for an overvoltage condition. If V<sub>O</sub> is 15% above V<sub>REF</sub>, then a fault latch is set and both output drivers are turned off. The latch will remain set until V<sub>CC</sub> goes below the undervoltage lockout value. A 3- $\mu$ s deglitch timer is included for noise immunity. Refer to the LODRV section for information on how to protect the load against overvoltages due to a shorted fault across the high-side power FET.

### detailed description (continued)

#### drive regulator

The drive regulator provides drive voltage to the output drivers. The minimum drive voltage is 7 V. The minimum short circuit current is 100 mA. Connect a  $1-\mu$ F ceramic capacitor from DRV to DRVGND.

#### LODRV

The LODRV circuit is designed to protect the load against overvoltages that occur if the high-side FETs become shorted. External components to sense an overvoltage condition are required to use this feature. When an overvoltage fault occurs, LODRV is pulled low and the low-side FET will be turned on, overriding all control signals inside the TPS56xx controller. The crowbar action will short the system-logic supply to ground through the faulted high-side FETs and the low-side FETs. A fuse, in series with V<sub>IN</sub>, should be added to disconnect the short circuit.

#### absolute maximum ratings over operating free-air temperature (unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>CC</sub> (see Note 1)                     |                              |

|------------------------------------------------------------------------|------------------------------|

| Input voltage range: BOOT to DRVGND (high-side driver ON)              | –0.3 to 30 V                 |

| BOOT to HIGHDRV                                                        | –0.3 to 15 V                 |

| BOOT to BOOTLO                                                         | –0.3 to 15 V                 |

| INHIBIT, LODRV                                                         | –0.3 to 7.3 V                |

| PWRGD, OCP                                                             | –0.3 to 7 V                  |

| LOHIB, LOSENSE, IOUTLO, HISENSE                                        | –0.3 to 14 V                 |

| VSENSE                                                                 | –0.3 to 5 V                  |

| Voltage difference between ANAGND and DRVGND                           | ±0.5 V                       |

| Output current, VREFB                                                  | 0.5 mA                       |

| Short circuit duration, DRV                                            | Continuous                   |

| Continuous total power dissipation                                     | See Dissipation Rating Table |

| Operating junction temperature range, T <sub>J</sub>                   |                              |

| Storage temperature range, T <sub>stg</sub>                            |                              |

| Lead temperature soldering 1,6 mm (1/16 inch) from case for 10 seconds |                              |

<sup>+</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: Unless otherwise specified, all voltages are with respect to ANAGND.

#### DISSIPATION RATING TABLE

| PACKAGE | T <sub>A</sub> ≤ 25°C | DERATING FACTOR             | T <sub>A</sub> = 70°C | T <sub>A</sub> = 85°C |

|---------|-----------------------|-----------------------------|-----------------------|-----------------------|

|         | POWER RATING          | ABOVE T <sub>A</sub> = 25°C | POWER RATING          | POWER RATING          |

| PWP     | 1150 mW               | 11.5 mW/°C                  | 630 mW                | 460 mW                |

SLVS177B – SEPTEMBER 1998 – REVISED JULY 2000

### recommended operating conditions

|                              |                                                                                                                                                                | MIN  | MAX  | UNIT |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|

| Supply voltage, V            | Vcc                                                                                                                                                            | 11.4 | 13   | V    |

|                              | BOOT to DRVGND                                                                                                                                                 | 0    | 28   |      |

| Input voltage INHIB<br>LOHII | BOOT to BOOTLO                                                                                                                                                 | 0    | 13   |      |

| Input voltage                | upply voltage, V <sub>CC</sub> 11.4 13<br>BOOT to DRVGND 0 28<br>BOOT to BOOTLO 0 13<br>INHIBIT, LODRV, PWRGD, OCP 0 6<br>LOHIB, LOSENSE, IOUTLO, HISENSE 0 13 | 6    | V    |      |

|                              | LOHIB, LOSENSE, IOUTLO, HISENSE                                                                                                                                | 0    | 13   |      |

|                              | VSENSE                                                                                                                                                         | 0    | 4.5  |      |

| Voltage difference           | e between ANAGND and DRVGND                                                                                                                                    | 0    | ±0.2 | V    |

| Output current, \            | /REFB <sup>†</sup>                                                                                                                                             | 0    | 0.4  | mA   |

<sup>†</sup> Not recommended to load VREFB other than to set hysteresis since IVREFB sets slowstart time.

# electrical characteristics over recommended operating virtual junction temperature range, $V_{CC}$ = 12 V, $I_{DRV}$ = 0 A (unless otherwise noted)

#### reference

|       | PARAM          | ETER                                                 | TEST CONDITIONS                      | MIN     | TYP   | MAX     | UNIT |

|-------|----------------|------------------------------------------------------|--------------------------------------|---------|-------|---------|------|

|       | TPS5615        |                                                      | 1.485                                |         | 1.515 |         |      |

| VDEE  | /RFF Reference | TPS5618                                              |                                      | 1.782   |       | 1.818   |      |

| VDLL  | TPS5625        | $V_{CC} = 11.4 \text{ V} \text{ to } 12.6 \text{ V}$ | 2.475                                |         | 2.525 | V       |      |

|       |                | TPS5633                                              |                                      | 3.267   |       | 3.333   |      |

| VREFB | Output voltage | )                                                    | I <sub>REFB</sub> = 50 μA            | VREF-2% | VREF  | VREF+2% | V    |

| VREFB | Output regulat | ion                                                  | $10 \ \mu A \le I_O \le 500 \ \mu A$ |         | 2     |         | mV   |

### power good

| PARAMETER                       | TEST CONDITIONS          | MIN | TYP | MAX  | UNIT  |

|---------------------------------|--------------------------|-----|-----|------|-------|

| Undervoltage trip threshold     |                          | 90  | 93  | 95   | %VREF |

| Low-level output voltage, PWRGD | IO = 5 mA                |     | 0.5 | 0.75 | V     |

| High-level input current, PWRGD | V <sub>PWRGD</sub> = 6 V |     | 1   |      | μA    |

| Hysteresis                      |                          |     | 10  |      | mV    |

#### overvoltage protection

| PARAMETER                  | TEST CONDITIONS | MIN | TYP | MAX | UNIT  |

|----------------------------|-----------------|-----|-----|-----|-------|

| Overvoltage trip threshold |                 | 112 | 115 | 120 | %VREF |

| Hysteresis                 | See Note 2      |     | 10  |     | mV    |

NOTE 2: Ensured by design, not tested.

#### slowstart

| PARAMETER                       | TEST CONDITIONS                               | MIN  | TYP | MAX  | UNIT |

|---------------------------------|-----------------------------------------------|------|-----|------|------|

| Charge current                  | $V_{SLOWST} = 0.5 V$ , $I_{VREFB} = 65 \mu A$ | 10.4 | 13  | 15.6 | μA   |

| Discharge current               | VSOFTST = 1 V                                 |      | 3   |      | mA   |

| Comparator input offset voltage |                                               |      |     | 10   | mV   |

| Comparator input bias current   | See Note 2                                    |      | 10  | 100  | nA   |

| Hysteresis                      |                                               | -7.5 |     | 7.5  | mV   |

NOTE 2: Ensured by design, not tested.

SLVS177B - SEPTEMBER 1998 - REVISED JULY 2000

# electrical characteristics over recommended operating virtual junction temperature range, $V_{CC} = 12 \text{ V}$ , $I_{DRV} = 0 \text{ A}$ (unless otherwise noted) (continued)

inhibit

| PARAMETER         | TEST CONDITIONS | MIN  | TYP | MAX  | UNIT |

|-------------------|-----------------|------|-----|------|------|

| Startup threshold |                 | 1.9  | 2.1 | 2.35 | V    |

| Hysteresis        |                 | 0.08 | 0.1 | 0.12 | V    |

| Stop threshold    |                 | 1.85 |     |      | V    |

### input undervoltage lockout

| PARAMETER         | TEST CONDITIONS | MIN  | TYP | MAX   | UNIT |

|-------------------|-----------------|------|-----|-------|------|

| Startup threshold |                 | 9.25 | 10  | 10.75 | V    |

| Hysteresis        |                 | 1.9  | 2   | 2.2   | V    |

| Stop threshold    |                 | 7.5  |     |       | V    |

#### hysteretic comparator

| PARAMETER                  | TEST CONDITIONS                                    | MIN  | TYP | MAX | UNIT |

|----------------------------|----------------------------------------------------|------|-----|-----|------|

| Input offset voltage       |                                                    | -2.5 |     | 2.5 | mV   |

| Input bias current         | See Note 2                                         |      |     | 500 | nA   |

| Hysteresis accuracy        | VREFB - VHYST = 15 mV, (hysteresis window = 30 mV) | -3.5 |     | 3.5 | mV   |

| Maximum hysteresis setting | VREFB - VHYST = 30 mV                              |      | 60  |     | mV   |

NOTE 2: Ensured by design, not tested.

#### overcurrent protection

| PARAMETER          | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------------|-----------------|-----|-----|-----|------|

| OCP trip threshold |                 | 90  | 100 | 110 | mV   |

| Input bias current |                 |     |     | 100 | nA   |

SLVS177B - SEPTEMBER 1998 - REVISED JULY 2000

# electrical characteristics over recommended operating virtual junction temperature range, $V_{CC} = 12 \text{ V}$ , $I_{DRV} = 0 \text{ A}$ (unless otherwise noted) (continued)

### high-side VDS sensing

| PARAMETER                        | TEST CO                                                                       | NDITIONS                                  | MIN  | TYP | MAX  | UNIT |

|----------------------------------|-------------------------------------------------------------------------------|-------------------------------------------|------|-----|------|------|

| Gain                             |                                                                               |                                           |      | 2   |      | V/V  |

| Initial accuracy                 | VHISENSE = 12 V,<br>Differential input to Vds                                 | VLOSENSE = 11.9 V<br>sensing amp = 100 mV | 194  |     | 206  | mV   |

| IOUTLO sink current              | $5 \text{ V} \le \text{V}_{\text{IOUTLO}} \le 13 \text{ V}$                   |                                           |      |     | 250  | nA   |

| IOUT source current              | V <sub>IOUT</sub> = 0.5 V,<br>V <sub>IOUTLO</sub> = 11.5 V                    | VHISENSE = 12 V,                          | 500  |     |      | μA   |

| IOUT sink current                | V <sub>IOUT</sub> = 0.05 V,<br>V <sub>IOUTLO</sub> = 12 V                     | VHISENSE = 12 V,                          | 50   |     |      | μΑ   |

|                                  | VHISENSE = 11 V                                                               |                                           | 0    |     | 2    |      |

| Output voltage swing             | VHISENSE = 4.5 V                                                              | R <sub>IOUT</sub> = 10 kΩ                 | 0    |     | 1.5  | V    |

|                                  | VHISENSE = 3 V                                                                |                                           | 0    |     | 0.75 |      |

| LOSENSE high-level input voltage | VHISENSE = 4.5 V,                                                             | See Note 2                                | 2.85 |     |      | V    |

| LOSENSE low-level input voltage  | VHISENSE = 4.5 V,                                                             | See Note 2                                |      |     | 2.4  | V    |

|                                  | 11.4 V ≤ VHISENSE ≤ 1<br>LOSENSE connected to<br>VHISENSE - VIOUTLO           | HISENSE,                                  | 50   | 60  | 80   |      |

| Sample/hold resistance           | 4.5 V $\leq$ VHISENSE $\leq$ 5.<br>LOSENSE connected to<br>VHISENSE - VIOUTLO | DHISENSE,                                 | 62   | 85  | 123  | Ω    |

|                                  | $3 V \le V_{HISENSE} \le 3.6$<br>LOSENSE connected to<br>VHISENSE - VIOUTLO   | HISENSE,                                  | 67   | 95  | 144  |      |

| CMRR                             | VHISENSE = 12.6 V to<br>VHISENSE - VOUTLO                                     |                                           | 69   | 75  |      | dB   |

NOTE 2: Ensured by design, not tested.

### deadtime

| PARAMETER |                                   | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----------|-----------------------------------|-----------------|-----|-----|-----|------|

| LOHIB     | 1 Pade Laws Propositional Comment | See Note 2      | 2.4 |     |     |      |

| LODR      | High-level input voltage          | See Note 2      | 3   |     |     | V    |

| LOHIB     |                                   | See Note 2      |     |     | 1.4 | V    |

| LODR      | Low-level input voltage           | See Note 2      |     |     | 1.7 | v    |

NOTE 2: Ensured by design, not tested.

#### LODRV

| PARAMETER |                          | TEST CONDITIONS | MIN  | TYP | MAX  | UNIT |

|-----------|--------------------------|-----------------|------|-----|------|------|

|           | High-level input voltage |                 | 1.85 |     |      | V    |

| LODRV     | Low-level input voltage  |                 |      |     | 0.95 | V    |

#### drive regulator

| PARAMETER             | TEST CONDITIONS                                           | MIN | TYP | MAX | UNIT |

|-----------------------|-----------------------------------------------------------|-----|-----|-----|------|

| Output voltage        | 11.4 V $\leq$ VCC $\leq$ 12.6 V, I <sub>DRV</sub> = 50 mA | 7   |     | 9   | V    |

| Output regulation     | $1 \text{ mA} \le I_{DRV} \le 500 \text{ mA}$             |     | 100 |     | mV   |

| Short-circuit current |                                                           | 100 |     |     | mA   |

SLVS177B - SEPTEMBER 1998 - REVISED JULY 2000

# electrical characteristics over recommended operating virtual junction temperature range, $V_{CC} = 12 \text{ V}$ , $I_{DRV} = 0 \text{ A}$ (unless otherwise noted) (continued)

#### bias regulator

| PARAMETER      | TEST CONDITIONS                             | MIN | TYP | MAX | UNIT |

|----------------|---------------------------------------------|-----|-----|-----|------|

| Output voltage | 11.4 V $\leq$ VCC $\leq$ 12.6 V, See Note 3 | 6   |     |     | V    |

NOTE 3: The bias regulator is designed to provide a quiet bias supply for the TPS56xx controller. External loads should not be driven by the bias regulator.

#### output drivers

| PARAMETER (see      | Note 4)          | TEST CONDITIONS                                                                                                                                        | MIN | TYP | MAX | UNIT |

|---------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

|                     | High-side sink   | Duty cycle < 2%, $t_{pW}$ < 100 µs, $T_J$ = 125°C,                                                                                                     | 2   |     |     |      |

| Peak output current | High-side source | VBOOT - VBOOTLO = 6.5 V,<br>VHIGHDR = 1.5 V (SRC) or 5 V (sink), See Note 2                                                                            |     |     |     | ^    |

|                     | Low-side sink    | Duty cycle < 2%, $t_{pW}$ < 100 µs, T <sub>J</sub> = 125°C,<br>V <sub>DRV</sub> = 6.5 V, V <sub>LOWDR</sub> = 1.5 V (SRC) or 5 V<br>(sink), See Note 2 |     |     |     | A    |

|                     | Low-side source  |                                                                                                                                                        |     |     |     |      |

|                     | High-side sink   | $T_J = 125^{\circ}C, V_{BOOT} - V_{BOOTLO} = 6.5 V,$                                                                                                   |     |     | 3   |      |

| Output resistance   | High-side source | V <sub>HIGHDR</sub> = 1.5 V (SRC) or 5 V (sink)                                                                                                        |     |     | 45  | Ω    |

|                     | Low-side sink    | $T_J = 125^{\circ}C$ , $V_{DRV} = 6.5 V$ ,<br>$V_{LOWDR} = 1.5 V$ (SRC) or 5 V (sink)                                                                  |     |     | 5.7 | 52   |

|                     | Low-side source  |                                                                                                                                                        |     |     | 45  |      |

NOTES: 2. Ensured by design, not tested.

4. The pull up/down circuits of the drivers are bipolar and MOSFET transistors in parallel. The peak output current rating is the combined current from the bipolar and MOSFET transistors. The output resistance is the R<sub>DS(ON)</sub> of the MOSFET transistor when the voltage on the driver output is less than the saturation voltage of the bipolar transistor.

#### supply current

| PARAMETER                                   | TEST CONDITIONS                                                                                                                                                                                                                                                                                                      | MIN  | TYP | MAX | UNIT |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| V <sub>CC</sub> supply voltage range        |                                                                                                                                                                                                                                                                                                                      | 11.4 | 12  | 13  | V    |

|                                             |                                                                                                                                                                                                                                                                                                                      |      | 3   | 10  |      |

| V <sub>CC</sub> quiescent current           | $ \begin{array}{ll} \mbox{V}_{\mbox{INHIBIT}} = 5 \mbox{ V}, & \mbox{V}_{\mbox{CC}} > 10.75 \mbox{ V} \mbox{ at startup}, \\ \mbox{V}_{\mbox{BOOTLO}} = 0 \mbox{ V}, & \mbox{C}_{\mbox{HIGHDR}} = 50 \mbox{ pF}, \\ \mbox{C}_{\mbox{LOWDR}} = 50 \mbox{ pF}, & \mbox{f}_{\mbox{swx}} = 200 \mbox{ kHz} \end{array} $ |      | 5   |     | mA   |

|                                             | $V_{INHIBIT} = 0 V \text{ or } V_{CC} < 9.25 V \text{ at startup,}$<br>$V_{BOOT} = 13 V$ , $V_{BOOTLO} = 0 V$                                                                                                                                                                                                        |      |     | 80  | μΑ   |

| High-side drive regulator quiescent current | $ \begin{array}{ll} V_{\text{INHIBIT}} = 5 \text{ V}, & V_{\text{CC}} > 10.75 \text{ V} \text{ at startup}, \\ V_{\text{BOOT}} = 13 \text{ V}, & V_{\text{BOOTLO}} = 0 \text{ V}, \\ C_{\text{HIGHDR}} = 50 \text{ pF}, & f_{\text{SWX}} = 200 \text{ kHz} \end{array} $                                             |      | 2   |     | mA   |

NOTE 2: Ensured by design, not tested.

SLVS177B - SEPTEMBER 1998 - REVISED JULY 2000

# switching characteristics over recommended operating virtual junction temperature range, $V_{CC} = 12 \text{ V}$ , $I_{DRV} = 0 \text{ V}$ (unless otherwise noted)

| PARA                                           | METER                                                                                 | TEST CONDITIONS                                                                                           | MIN | TYP | MAX | UNIT |

|------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

|                                                | VSENSE to HIGHDR or<br>LOWDR (excluding deadtime)                                     | Overdrive = 10 mV (see Note 2)                                                                            |     | 150 | 250 | ns   |

|                                                | OCP comparator                                                                        | See Note 2                                                                                                |     | 1   |     |      |

| Propagation delay                              | OVP comparator                                                                        | See Note 2                                                                                                |     | 1   |     | μs   |

|                                                | PWRGD comparator                                                                      | See Note 2                                                                                                |     | 1   |     |      |

|                                                | SLOWST comparator                                                                     | Overdrive = 10 mV (see Note 2)                                                                            |     | 560 | 900 | ns   |

| Discrime                                       | HIGHDR output                                                                         |                                                                                                           |     |     | 60  |      |

| Rise time                                      | LOWDR output                                                                          | $\begin{array}{ll} C_L = 9 \text{ nF}, & V_{DRV} = 6.5 \text{ V}, \\ T_J = 125^\circ\text{C} \end{array}$ |     |     | 60  | ns   |

|                                                | HIGHDR output                                                                         |                                                                                                           |     |     | 60  |      |

| Fall time                                      | LOWDR output $C_L = 9 \text{ nF}, V_{DRV} = 6.5 \text{ V}, T_J = 125^{\circ}\text{C}$ |                                                                                                           |     | 60  | ns  |      |

| Deglitch time (includes                        | OCP                                                                                   | See Note 2                                                                                                | 2   |     | 5   |      |

| comparator propagation delay)                  | OVP                                                                                   | See Note 2                                                                                                | 2   |     | 5   | μs   |

|                                                |                                                                                       | VHISENSE = 12 V,<br>VIOUTLO pulsed from 12 V to 11.9 V,<br>100 ns rise/fall times, See Note 2             |     |     | 2   |      |

| Response time                                  | High-side VDS sensing                                                                 | VHISENSE = 4.5 V,<br>VIOUTLO pulsed from 4.5 V to 4.4 V,<br>100 ns rise/fall times, See Note 2            |     |     | 3   | μs   |

|                                                |                                                                                       | VHISENSE = 3 V,<br>VIOUTLO pulsed from 3 V to 2.9 V,<br>100 ns rise/fall times, See Note 2                |     |     | 3   |      |

| Short-circuit protection rising-<br>edge delay | SCP                                                                                   | LOSENSE = 0 V, (see Note 2)                                                                               | 300 |     | 500 | ns   |

| Turn-on/turn-off delay                         | V <sub>DS</sub> sensing sample/hold switch                                            | 3 V ≤ V <sub>HISENSE</sub> ≤ 11 V,<br>VLOSENSE = V <sub>HISENSE</sub><br>(see Note 2)                     | 30  |     | 100 | ns   |

| Crossover delay time                           | LOWDR to HIGHDRV, and LOHIB to LOWDR                                                  | See Note 2                                                                                                | 30  |     | 100 | ns   |

| Prefilter pole frequency                       | Hysteretic comparator                                                                 | See Note 2                                                                                                |     | 5   |     | MHz  |

| Propagation delay                              | LODRV                                                                                 | See Note 2                                                                                                |     |     | 400 | ns   |

NOTE 2: Ensured by design, not tested.

SLVS177B - SEPTEMBER 1998 - REVISED JULY 2000

SLVS177B - SEPTEMBER 1998 - REVISED JULY 2000

SLVS177B - SEPTEMBER 1998 - REVISED JULY 2000

SLVS177B - SEPTEMBER 1998 - REVISED JULY 2000

SLVS177B - SEPTEMBER 1998 - REVISED JULY 2000

SLVS177B - SEPTEMBER 1998 - REVISED JULY 2000

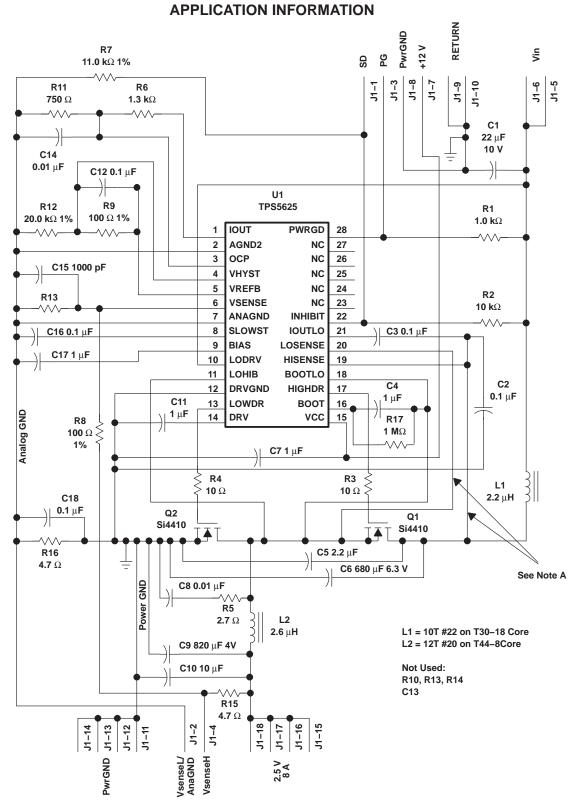

## **APPLICATION INFORMATION**

Synchronous rectifier buck regulator circuits are used where high efficiency and low dropout voltages are required. The TPS56xx controller is useful in applications with very high transient loads and wide dc load ranges, such as multiple-DSP applications.

The circuit below will meet a wide variety of applications with maximum continuous-rated output currents of up to 8 A. Design tradeoffs, such as cost, size, or efficiency may need to be addressed for specific applications. Care should be taken in the proper layout (see last section of this data sheet for specific layout guidelines), especially in the higher-current configurations, to ensure that noise and ripple are kept to a minimum. Basic layout considerations are discussed in the 1996 Power Supply Circuits Databook (Literature no. SLVD002). Design guidelines and equations are discussed in *Synchronous Buck Converter Design Using TPS56xx Controllers in SLVP10x EVMs User's Guide* (Literature no. SLVU007).

SLVS177B - SEPTEMBER 1998 - REVISED JULY 2000

NOTE A: Theses two traces should be physically close to each other for good noise immunity.

Figure 24. Typical Design Schematic

SLVS177B - SEPTEMBER 1998 - REVISED JULY 2000

| TEST            | CO                        | CONDITIONS                  |      |      |  |  |  |

|-----------------|---------------------------|-----------------------------|------|------|--|--|--|

| Output voltage  | V <sub>IN</sub> = 5.25 V, | IO = 8 A                    | 2.50 | V    |  |  |  |

| Load regulation | V <sub>IN</sub> = 5.25 V, | I <sub>O</sub> = 0.8 to 8 A | 0.4  | %    |  |  |  |

| Line regulation | I <sub>O</sub> =6 A,      | $V_{CC}$ = 4.5 V to 6 V     | 0.2  | %    |  |  |  |

| Ripple          | $V_{IN} = 5.25 V,$        | I <sub>O</sub> = 8 A        | 50   | mVpp |  |  |  |

| Efficiency      | V <sub>IN</sub> = 5.25 V, | I <sub>O</sub> = 8 A        | 89   | %    |  |  |  |

### Table 1. Test Results for 2.5-V, 8-A Converter

### Table 2. 2.5-V, 8-A Converter Bill of Materials

| REF DES | QTY | PART NUMBER        | DESCRIPTION                                              | MFG       |

|---------|-----|--------------------|----------------------------------------------------------|-----------|

| C1      | 1   | 10SS22M            | Capacitor, Os-Con, 22 μF, 10 V, 20%                      | Sanyo     |

| C2      | 4   | GRM39X7R104K016A   | Capacitor, Ceramic, 0.1 µF, 16 V, 10%, X7R               | muRata    |

| C3      |     | GRM39X7R104K016A   | Capacitor, Ceramic, 0.1 μF, 16 V, 10%, X7R               | muRata    |

| C4      | 4   | GRM42-6Y5V105Z016A | Capacitor, Ceramic, 1 μF, 16 V, +80%–20%                 | muRata    |

| C5      | 1   | GRM42-6Y5V225Z016A | Capacitor, Os-Con, 2.2 μF, 16 V, Y5U                     | muRata    |

| C6      | 1   | 6SP680M            | Capacitor, Os-Con, 680 μF, 6.3 V, 20%                    | Sanyo     |

| C7      |     | GRM42-6Y5V105Z016A | Capacitor, Ceramic, 1 µF, 16 V, +80%–20%                 | muRata    |

| C8      | 2   | GRM39X7R103K025A   | Capacitor, Ceramic, 0.01 µF, 25 V, 10%, X7R              | muRata    |

| C9      | 1   | 4SP820M            | Capacitor, Os-Con, 820 μF, 4 V, 20%                      | Sanyo     |

| C10     | 1   | GRM235Y5V106Z016A  | Capacitor, Ceramic, 10 µF, 16 V, Y5V                     | muRata    |

| C11     |     | GRM42-6Y5V105Z016A | Capacitor, Ceramic, 1 μF, 16 V, +80%–20%                 | muRata    |

| C12     |     | GRM39X7R104K016A   | Capacitor, Ceramic, 0.1 µF, 16 V, 10%, X7R               | muRata    |

| C14     |     | GRM39X7R103K025A   | Capacitor, Ceramic, 0.01 µF, 25 V, 10%, X7R              | muRata    |

| C15     | 1   | GRM39X7R102K050A   | Capacitor, Ceramic, 1000 pF, 50 V, 10%, X7R              | muRata    |

| C16     |     | GRM39X7R104K016A   | Capacitor, Ceramic, 0.1 μF, 16 V, 10%, X7R               | muRata    |

| C17     |     | GRM42-6Y5V105Z016A | Capacitor, Ceramic, 1 μF, 16 V, +80%–20%                 | muRata    |

| C18     |     | GRM39X7R104K016A   | Capacitor, Ceramic, 0.1 µF, 16 V, 10%, X7R               | muRata    |

| J1      | 1   | S1122-18-ND        | Header, RA, 18-pin, 0.23 Posts $\times$ 0.20 Tails       | Sullins   |

| L1      | 1   |                    | Inductor, Filter, 2.2 µH, 8.5 A (10T #22 on T30-18 Core) |           |

| L2      | 1   |                    | Inductor, Filter, 2.6 μH, 8.5 A (12T #20 on T44-8 Core)  |           |

| Q1      | 2   | Si4410DY           | FET, N-ch, 30-V, 10-A, 13-mΩ                             | Siliconix |

| Q2      |     | Si4410DY           | FET, N-ch, 30-V, 10-A, 13-mΩ                             | Siliconix |

| R1      | 3   | Std                | Resistor, Chip, 1.0 kΩ, 1/16W, 5%                        |           |

| R2      | 1   | Std                | Resistor, Chip, 10 kΩ, 1/16W, 5%                         |           |

| R3      | 2   | Std                | Resistor, Chip, 10 Ω, 1/10W, 5%                          |           |

| R4      |     | Std                | Resistor, Chip, 10 Ω, 1/10W, 5%                          |           |

| R5      | 1   | Std                | Resistor, Chip, 2.7 Ω, 1/4W, 5%                          |           |

| R6      |     | Std                | Resistor, Chip, 1.3 kΩ, 1/16W, 5%                        |           |

| R7      | 1   | Std                | Resistor, Chip, 11.0 kΩ, 1/16W, 1%                       |           |

| R8      | 2   | Std                | Resistor, Chip, 100 Ω, 1/16W, 1%                         |           |

| R9      |     | Std                | Resistor, Chip, 100 Ω, 1/16W, 1%                         |           |

| R11     |     | Std                | Resistor, Chip, 750 Ω, 1/16W, 5%                         |           |

| R12     | 1   | Std                | Resistor, Chip, 20.0 kΩ, 1/16W, 1%                       |           |

| R15     | 2   | Std                | Resistor, Chip, 4.7 Ω, 1/16W, 5%                         |           |

| R16     |     | Std                | Resistor, Chip, 4.7 Ω, 1/16W, 5%                         |           |

| R17     | 1   | Std                | Resistor, Chip, 1 MΩ, 1/16W, 5%                          |           |

| U1      | 1   | TPS5625PWP         | IC, PWM Ripple Controller, FIxed 2.5 V                   | TI        |

SLVS177B - SEPTEMBER 1998 - REVISED JULY 2000

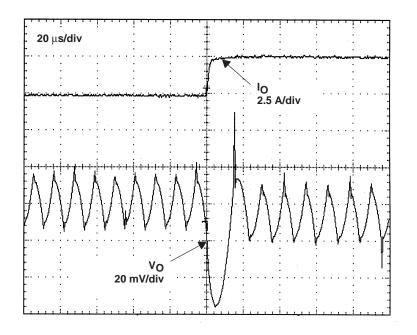

Figure 26. Output Voltage Ripple at 8 A

SLVS177B - SEPTEMBER 1998 - REVISED JULY 2000

## **APPLICATION INFORMATION**

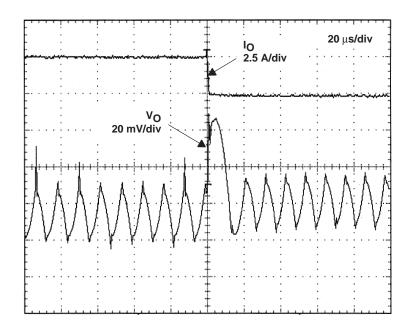

Figure 27. Rising Load Transient Response

Figure 28. Falling Load Transient Response

SLVS177B - SEPTEMBER 1998 - REVISED JULY 2000

## APPLICATION INFORMATION

### layout guidelines

Good power supply results will only occur when care is given to proper design and layout. Layout will affect noise pickup and generation and can cause a good design to perform with less than expected results. With a range of currents from milliamps to tens or even hundreds of amps, good power supply layout is much more difficult than most general PCB design. The general design should proceed from the switching node to the output, then back to the driver section and, finally, place the low-level components. Below are several specific points to consider before layout of a TPS56xx design begins.

- 1. All sensitive analog components should be referenced to ANAGND. These include components connected to SLOWST, IOUT, OCP, VSENSE, VREFB, VHYST, BIAS, and LOHIB.

- Analog ground and drive ground should be isolated as much as possible. Ideally, analog ground will connect to the ground side of the bulk storage capacitors, on V<sub>O</sub>, and drive ground will connect to the main ground plane close to the source of the low-side FET.

- 3. Connections from the drivers to the gate of the power FETs should be as short and wide as possible to reduce stray inductance. This becomes more critical if external gate resistors are not being used.

- The bypass capacitor for the DRV regulator should be placed close to the TPS56xx and be connected to DRVGND.

- 5. The bypass capacitor for  $V_{CC}$  should be placed close to the TPS56xx and be connected to DRVGND.

- 6. When configuring the high-side driver as a floating driver, the connection from BOOTLO to the power FETs should be as short and as wide as possible. The other pins that also connect to the power FETs, LOHIB and LOSENSE, should have a separate connection to the FETs, since BOOTLO will have large peak currents flowing through it.

- 7. When configuring the high-side driver as a floating driver, the bootstrap capacitor (connected from BOOT to BOOTLO) should be placed close to the TPS56xx.

- 8. When configuring the high-side driver as a ground referenced driver, BOOTLO should be connected to DRVGND.

- The bulk storage capacitors across V<sub>I</sub> should be placed close to the power FETs. High-frequency bypass capacitors should be placed in parallel with the bulk capacitors and connected close to the drain of the high-side FET and close to the source of the low-side FET.

- 10. High-frequency bypass capacitors should be placed across the bulk storage capacitors on  $V_{O}$ .

- 11. HISENSE and LOSENSE should be connected very close to the drain and source, respectively, of the high-side FET. HISENSE and LOSENSE should be routed very close to each other to minimize differential-mode noise coupling to these traces.

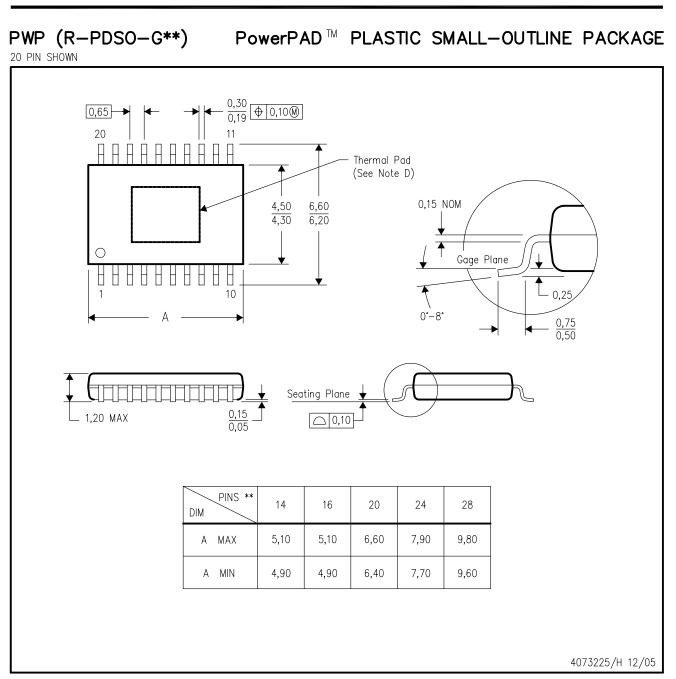

### PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| TPS5618PWP       | ACTIVE                | HTSSOP          | PWP                | 28   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS5618PWPG4     | ACTIVE                | HTSSOP          | PWP                | 28   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS5625PWP       | ACTIVE                | HTSSOP          | PWP                | 28   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS5625PWPG4     | ACTIVE                | HTSSOP          | PWP                | 28   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS5625PWPR      | ACTIVE                | HTSSOP          | PWP                | 28   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS5625PWPRG4    | ACTIVE                | HTSSOP          | PWP                | 28   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS5633PWP       | ACTIVE                | HTSSOP          | PWP                | 28   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS5633PWPR      | ACTIVE                | HTSSOP          | PWP                | 28   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS5633PWPRG4    | ACTIVE                | HTSSOP          | PWP                | 28   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details. **TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products           |                        | Applications       |                           |

|--------------------|------------------------|--------------------|---------------------------|

| Amplifiers         | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters    | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface          | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic              | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt         | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers   | microcontroller.ti.com | Security           | www.ti.com/security       |

| Low Power Wireless | www.ti.com/lpw         | Telephony          | www.ti.com/telephony      |

|                    |                        | Video & Imaging    | www.ti.com/video          |

|                    |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2007, Texas Instruments Incorporated