# onsemi

# 1/3-Inch Wide VGA CMOS Digital Image Sensor

# MT9V024/D

# Description

The MT9V024 is a 1/3-inch wide-VGA format CMOS active-pixel digital image sensor with global shutter and high dynamic range (HDR) operation. The sensor has specifically been designed to support the demanding interior and exterior automotive imaging needs, which makes this part ideal for a wide variety of imaging applications in real-world environments.

#### Table 1. KEY PERFORMANCE PARAMETERS

| Parameter                         | Value                                                                         |

|-----------------------------------|-------------------------------------------------------------------------------|

| Optical Format                    | 1/3-inch                                                                      |

| Active Imager Size                | 4.51 mm (H) × 2.88 mm (V)<br>5.35 mm Diagonal                                 |

| Active Pixels                     | 752 H × 480 V                                                                 |

| Pixel Size                        | 6.0 μm × 6.0 μm                                                               |

| Color Filter Array                | Monochrome or Color RGB Bayer or RCCC Pattern                                 |

| Shutter Type                      | Global Shutter                                                                |

| Maximum Data Rate<br>Master Clock | 27 Mp/s<br>27 MHz                                                             |

| Full Resolution                   | 752 × 480                                                                     |

| Frame Rate                        | 60 fps (at Full Resolution)                                                   |

| ADC Resolution                    | 10-bit Column-Parallel                                                        |

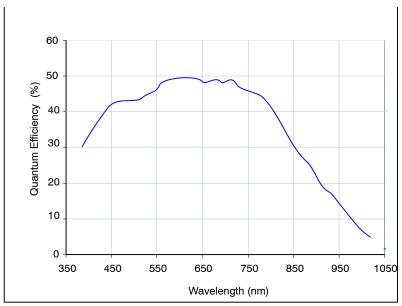

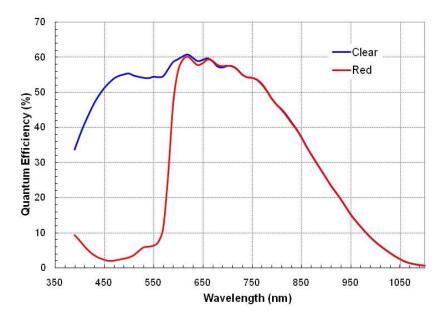

| Responsivity                      | 4.8 V/lux-sec (550 nm)                                                        |

| Dynamic Range                     | > 55 dB Linear;<br>> 100 dB in HDR Mode                                       |

| Supply Voltage                    | 3.3 V ±[0.3 V (All Supplies)                                                  |

| Power Consumption                 | < 160 mW at Maximum Data Rate (LVDS Disabled); 120 $\mu$ W Standby Power at 3 |

| Operating Tempera-<br>ture        | –40°C to +[]05°C                                                              |

| Packaging                         | 52-ball iBGA, Automotive-qualified; Wafer or Die                              |

# Features

- Array Format: Wide–VGA, Active 752 H x 480 V (360,960 pixels)

- Global Shutter Photodiode Pixels; Simultaneous Integration and Readout

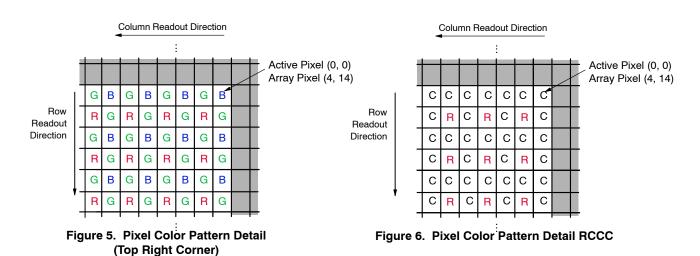

- RGB Bayer, Monochrome, or RCCC: NIR Enhanced Performance for Use with Non-visible NIR Illumination

- Readout Modes: Progressive or Interlaced

- Shutter Efficiency: >99%

- Simple Two-Wire Serial Interface

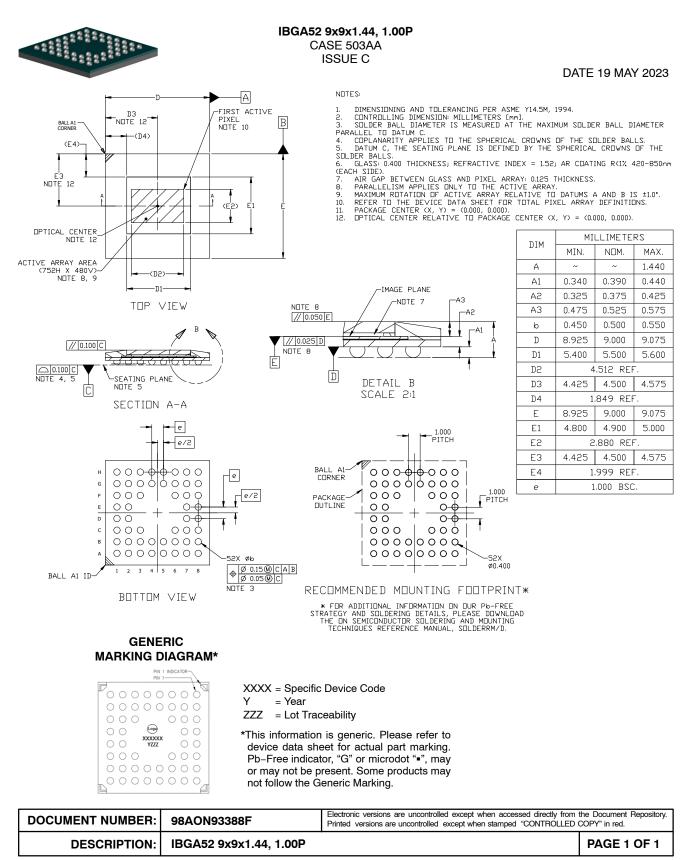

CASE 503AA

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 2 of this data sheet.

#### Features (continued)

- Real-Time Exposure Context Switching-Dual Register Set

- Register Lock Capability

- Window Size: User Programmable to Any Smaller Format (QVGA, CIF, QCIF). Data Rate Can Be Maintained Independent of Window Size

- Binning: 2 x 2 and 4 x 4 of The Full Resolution

- ADC: On-Chip, 10-bit Column-Parallel (Option to Operate in 12-bit to 10-bit Companding Mode)

- Automatic Controls: Auto Exposure Control (AEC) and Auto Gain Control (AGC); Variable Regional and Variable Weight AEC/ AGC

- Support for Four Unique Serial Control Register IDs to Control Multiple Imagers on the Same Bus

- Data Output Formats:

Single Sensor Mode: 10-bit Parallel/Stand-Alone 8-bit or 10-bit Serial LVDS

- Stereo Sensor Mode: Interspersed 8-bit Serial LVDS

- High Dynamic Range (HDR) Mode

# Applications

- Automotive

- Unattended Surveillance

- Stereo Vision

- Smart vision

- Automation

- Video as input

- Machine vision

# **ORDERING INFORMATION**

#### Table 2. AVAILABLE PART NUMBERS

| Part Number             | Product Description | Orderable Product Attribute Description |

|-------------------------|---------------------|-----------------------------------------|

| MT9V024D00XTCC13CC1-200 | VGA 1/3" GS CIS     | Die Sales, 200 $\mu m$ Thickness        |

| MT9V024D00XTMC13CC1-200 | VGA 1/3" GS CIS     | Die Sales, 200 µm Thickness             |

| MT9V024D00XTRC13CC1-200 | VGA 1/3" GS CIS     | Die Sales, 200 µm Thickness             |

| MT9V024D00XTRC13CC1-400 | VGA 1/3" GS CIS     | Die Sales, 400 μm Thickness             |

| MT9V024IA7XTC-DP        | VGA 1/3" GS CIS     | Dry Pack with Protective Film           |

| MT9V024IA7XTC-DR        | VGA 1/3" GS CIS     | Dry Pack without Protective Film        |

| MT9V024IA7XTM-DP        | VGA 1/3" GS CIS     | Dry Pack with Protective Film           |

| MT9V024IA7XTM-DR        | VGA 1/3" GS CIS     | Dry Pack without Protective Film        |

| MT9V024IA7XTM-TP        | WVGA 1/3" GS CIS    | Tape & Reel with Protective Film        |

| MT9V024IA7XTM-TR        | WVGA 1/3" GS CIS    | Tape & Reel without Protective Film     |

| MT9V024IA7XTR-DP        | VGA 1/3" GS CIS     | Dry Pack with Protective Film           |

| MT9V024IA7XTR-DR        | VGA 1/3" GS CIS     | Dry Pack without Protective Film        |

| MT9V024IA7XTR-TP        | VGA 1/3" GS CIS     | Tape & Reel with Protective Film        |

| MT9V024IA7XTR-TR        | VGA 1/3" GS CIS     | Tape & Reel without Protective Film     |

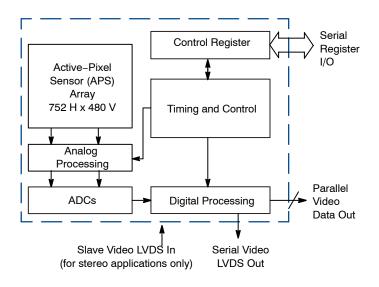

#### **GENERAL DESCRIPTION**

The MT9V024 is a 1/3-inch wide-VGA format CMOS active-pixel digital image sensor with global shutter and high dynamic range (HDR) operation. The sensor has specifically been designed to support the demanding interior and exterior automotive imaging needs, which makes this part ideal for a wide variety of imaging applications in real-world environments.

This wide–VGA CMOS image sensor features **onsemi**'s breakthrough low–noise CMOS imaging technology that achieves CCD image quality (based on signal–to–noise ratio and low–light sensitivity) while maintaining the inherent size, cost, and integration advantages of CMOS.

The active imaging pixel array is 752H x 480V. It incorporates sophisticated camera functions on-chip-such as binning 2 x 2 and 4 x 4, to improve sensitivity when operating in smaller resolutions-as well as windowing, column and row mirroring. It is programmable through a simple two-wire serial interface. The MT9V024 can be operated in its default mode or be programmed for frame size, exposure, gain setting, and other parameters. The default mode outputs a wide–VGA–size image at 60 frames per second (fps).

An on-chip analog-to-digital converter (ADC) provides 10 bits per pixel. A 12-bit resolution companded for 10 bits for small signals can be alternatively enabled, allowing more accurate digitization for darker areas in the image.

In addition to a traditional, parallel logic output the MT9V024 also features a serial low-voltage differential signaling (LVDS) output. The sensor can be operated in a stereo-camera, and the sensor, designated as a stereo-master, is able to merge the data from itself and the stereo-slave sensor into one serial LVDS stream.

The sensor is designed to operate in a wide temperature range ( $-40^{\circ}$ C to +  $105^{\circ}$ C).

|   | 1                       | 2                      | 3                            | 4                       | 5           | 6                    | 7                  | 8                  |

|---|-------------------------|------------------------|------------------------------|-------------------------|-------------|----------------------|--------------------|--------------------|

| A | V <sub>DD</sub><br>LVDS | SER<br>DATA            | , SER `\<br>DATA<br>`OUT N   | V <sub>DD</sub><br>LVDS | SYS-<br>CLK | D <sub>OUT</sub> 0   | D <sub>OUT</sub> 2 | D <sub>OUT</sub> 3 |

| в | LVDS<br>GND             | (SHFT)<br>CLKOUT)<br>P | , SHFT_`,<br>(CLKOUT)<br>`、N | V <sub>DD</sub>         | PIXCLK )    | (D <sub>OUT</sub> 1) | D <sub>OUT</sub> 4 | VAAPIX }           |

| С | BYPASS<br>_CLKIN<br>_P  | BYPASS                 | LVDS<br>GND                  |                         |             | D <sub>GND</sub>     | A <sub>GND</sub>   | V <sub>AA</sub>    |

| D | SER<br>DATA IN<br>P     | SER<br>DATIN           |                              |                         |             |                      | NC                 | NC                 |

| E | D <sub>OUT</sub> 5      | V <sub>DD</sub>        |                              |                         |             |                      | NC                 | NC                 |

| F | D <sub>OUT</sub> 6      | D <sub>OUT</sub> 7     | D <sub>GND</sub>             |                         |             | A <sub>GND</sub>     | VAA                | STAND-<br>BY       |

| G | D <sub>OUT</sub> 8 )    | (FRAME_)               | STLN_                        | S <sub>DATA</sub> ;     | STFRM       | LED_ )<br>OUT        | S_CTRL;            | RESET_;<br>BAR     |

| н | D <sub>OUT</sub> 9      | LINE_<br>VALID         | EXPO-                        | SCLK                    | ERROR )     | OE                   | RSVD               | S_CTRL<br>ADR1     |

Figure 2. Top View (Ball Down)

# **BALL DESCRIPTIONS**

# Table 3. BALL DESCRIPTIONS

| 52–Ball IBA<br>Numbers | Symbol             | Туре   | Descriptions                                                                                                                                          |  |

|------------------------|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| H7                     | RSVD               | Input  | Connect to D <sub>GND</sub>                                                                                                                           |  |

| D2                     | SER_DATAIN_N       | Input  | Serial data in for stereoscopy (differential negative). Tie to 1 k $\Omega$ pull-up (to 3.3 V) in non-stereoscopy mode                                |  |

| D1                     | SER_DATAIN_P       | Input  | Serial data in for stereoscopy (differential positive). Tie to D <sub>GND</sub> in non-stere-<br>oscopy mode                                          |  |

| C2                     | BYPASS_CLKIN_N     | Input  | Input bypass shift–CLK (differential negative). Tie to 1 $k\Omega$ pull–up (to 3.3 V) in non–stereoscopy mode                                         |  |

| C1                     | BYPASS_CLKIN_P     | Input  | Input bypass shift–CLK (differential positive). Tie to $D_{\text{GND}}$ in non–stereoscopy mode                                                       |  |

| H3                     | EXPOSURE           | Input  | Rising edge starts exposure in snapshot and slave modes                                                                                               |  |

| H4                     | SCLK               | Input  | Two-wire serial interface clock. Connect to $V_{DD}$ with 1.5 k $\Omega$ resistor even when no other two-wire serial interface peripheral is attached |  |

| H6                     | OE                 | Input  | D <sub>OUT</sub> enable pad, active HIGH                                                                                                              |  |

| G7                     | S_CTRL_ADR0        | Input  | Two-wire serial interface slave address select (see Table 6 on page 10)                                                                               |  |

| H8                     | S_CTRL_ADR1        | Input  | Two-wire serial interface slave address select (see Table 6 on page 10)                                                                               |  |

| G8                     | RESET_BAR          | Input  | Asynchronous reset. All registers assume defaults                                                                                                     |  |

| F8                     | STANDBY            | Input  | Shut down sensor operation for power saving                                                                                                           |  |

| A5                     | SYSCLK             | Input  | Master clock (26.6 MHz; 13 MHz – 27 MHz)                                                                                                              |  |

| G4                     | S <sub>DATA</sub>  | I/O    | Two-wire serial interface data. Connect to $V_{DD}$ with 1.5 $k\Omega$ resistor even when no other two-wire serial interface peripheral is attached   |  |

| G3                     | STLN_OUT           | I/O    | Output in master mode-start line sync to drive slave chip in-phase; input in slave mode                                                               |  |

| G5                     | STFRM_OUT          | I/O    | Output in master mode-start frame sync to drive a slave chip in-phase; input in slave mode                                                            |  |

| H2                     | LINE_VALID         | Output | Asserted when D <sub>OUT</sub> data is valid                                                                                                          |  |

| G2                     | FRAME_VALID        | Output | Asserted when D <sub>OUT</sub> data is valid                                                                                                          |  |

| E1                     | D <sub>OUT</sub> 5 | Output | Parallel pixel data output 5                                                                                                                          |  |

| F1                     | D <sub>OUT</sub> 6 | Output | Parallel pixel data output 6                                                                                                                          |  |

| F2                     | D <sub>OUT</sub> 7 | Output | Parallel pixel data output 7                                                                                                                          |  |

| G1                     | D <sub>OUT</sub> 8 | Output | Parallel pixel data output 8                                                                                                                          |  |

| H1                     | D <sub>OUT</sub> 9 | Output | Parallel pixel data output 9                                                                                                                          |  |

| H5                     | ERROR              | Output | Error detected. Directly connected to STEREO ERROR FLAG                                                                                               |  |

| G6                     | LED_OUT            | Output | LED strobe output                                                                                                                                     |  |

| B7                     | D <sub>OUT</sub> 4 | Output | Parallel pixel data output 4                                                                                                                          |  |

| A8                     | D <sub>OUT</sub> 3 | Output | Parallel pixel data output 3                                                                                                                          |  |

| A7                     | D <sub>OUT</sub> 2 | Output | Parallel pixel data output 2                                                                                                                          |  |

| B6                     | D <sub>OUT</sub> 1 | Output | Parallel pixel data output 1                                                                                                                          |  |

| A6                     | D <sub>OUT</sub> 0 | Output | Parallel pixel data output 0                                                                                                                          |  |

| B5                     | PIXCLK             | Output | Pixel clock out. D <sub>OUT</sub> is valid on rising edge of this clock                                                                               |  |

| B3                     | SHFT_CLKOUT_N      | Output | Output shift CLK (differential negative)                                                                                                              |  |

| B2                     | SHFT_CLKOUT_P      | Output | Output shift CLK (differential positive)                                                                                                              |  |

#### Table 3. BALL DESCRIPTIONS

| 52–Ball IBA<br>Numbers | Symbol               | Туре   | Descriptions                            |  |

|------------------------|----------------------|--------|-----------------------------------------|--|

| A3                     | SER_DATAOUT_N        | Output | Serial data out (differential negative) |  |

| A2                     | SER_DATAOUT_P        | Output | Serial data out (differential positive) |  |

| B4, E2                 | V <sub>DD</sub>      | Supply | Digital power 3.3 V                     |  |

| C8, F7                 | V <sub>AA</sub>      | Supply | Analog power 3.3 V                      |  |

| B8                     | VAAPIX               | Supply | Pixel power 3.3 V                       |  |

| A1, A4                 | V <sub>DD</sub> LVDS | Supply | Dedicated power for LVDS pads           |  |

| B1, C3                 | LVDSGND              | Ground | Dedicated GND for LVDS pads             |  |

| C6, F3                 | D <sub>GND</sub>     | Ground | Digital GND                             |  |

| C7, F6                 | A <sub>GND</sub>     | Ground | Analog GND                              |  |

| E7, E8, D7, D8         | NC                   | NC     | No connect (Note 3)                     |  |

1. Pin H7 (RSVD) must be tied to GND.

2. Output enable (OE) tri-states signals D<sub>OUT</sub>0-D<sub>OUT</sub>9, LINE\_VALID, FRAME\_VALID, and PIXCLK.

3. No connect. These pins must be left floating for proper operation.

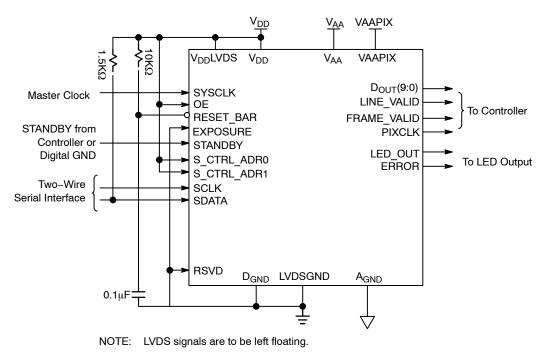

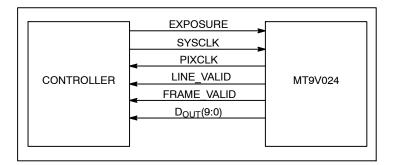

Figure 3. Typical Configuration (Connection)-Parallel Output Mode

# **PIXEL DATA FORMAT**

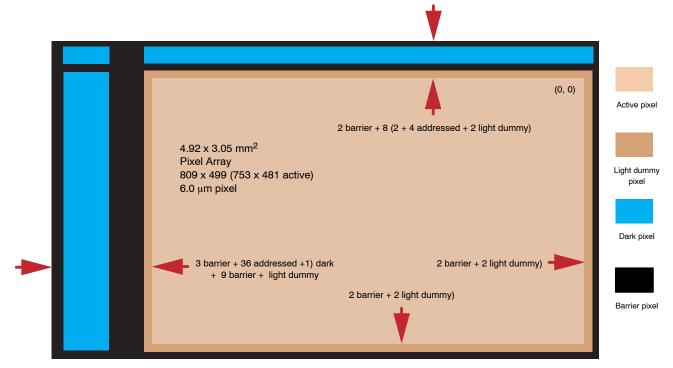

#### **PIXEL ARRAY STRUCTURE**

The MT9V024 pixel array is configured as 809 columns by 499 rows, shown in Figure 4. The dark pixels are optically black and are used internally to monitor black level. Of the left 52 columns, 36 are dark pixels used for row noise correction. Of the top 14 rows of pixels, two of the dark rows are used for black level correction. Also, three black rows from the top black rows can be read out by setting the show dark rows bit in the Read Mode register; setting show dark columns will display the 36 dark columns. There are 753 columns by 481 rows of optically active pixels. While the sensor's format is 752 x 480, one additional active column and active row are included for use when horizontal or vertical mirrored readout is enabled, to allow readout to start on the same pixel. This one pixel adjustment is always performed, for monochrome or color versions. The active area is surrounded with optically transparent dummy pixels to improve image uniformity within the active area. Neither dummy pixels nor barrier pixels can be read out.

# **COLOR (RGB BAYER) DEVICE LIMITATIONS**

The color version of the MT9V024 does not support or offers reduced performance for the following functionalities.

# **Pixel Binning**

Pixel binning is done on immediate neighbor pixels only, no facility is provided to skip pixels according to a Bayer pattern. Therefore, the result of binning combines pixels of different colors. See "Pixel Binning" for additional information.

#### Interlaced Readout

Interlaced readout yields one field consisting only of red and green pixels and another consisting only of blue and green pixels. This is due to the Bayer pattern of the CFA.

#### Automatic Black Level Calibration

When the color bit is set (R0x0F[1] = 1), the sensor uses black level correction values from one green plane, which are applied to all colors. To use the calibration value based on all dark pixels' offset values, the color bit should be cleared.

# **Defective Pixel Correction**

For defective pixel correction to calculate replacement pixel values correctly, for color sensors the color bit must be

set (R0x0F[1] = 1). However, the color bit also applies unequal offset to the color planes, and the results might not be acceptable for some applications.

# **Other Limiting Factors**

Black level correction and row-wise noise correction are applied uniformly to each color. The row-wise noise correction algorithm does not work well in color sensors. Automatic exposure and gain control calculations are made based on all three colors, not just the green channel. High dynamic range does operate in color; however, **onsemi** strongly recommends limiting use to linear operation where good color fidelity is required.

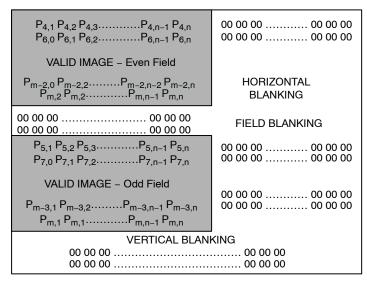

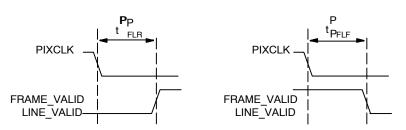

# **OUTPUT DATA FORMAT**

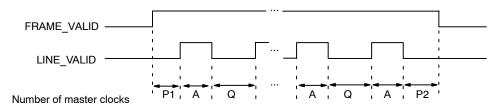

The MT9V024 image data can be read out in a progressive scan or interlaced scan mode. Valid image data is surrounded by horizontal and vertical blanking, as shown in Figure 7. The amount of horizontal and vertical blanking is programmable through R0x05 and R0x06, respectively (R0xCD and R0xCE for context B). LV is HIGH during the shaded region of the figure. See "Output Data Timing" for the description of FV timing.

| $\begin{array}{c} P_{0,0} \ P_{0,1} \ P_{0,2} & \cdots & P_{0,n-1} \ P_{0,n} \\ P_{1,0} \ P_{1,1} \ P_{1,2} & \cdots & P_{1,n-1} \ P_{1,n} \\ \\ \hline & VALID \ iMAGE \\ P_{m-1,0} \ P_{m-1,1} & \cdots & P_{m-1,n-1} \ P_{m-1,n} \\ P_{m,0} \ P_{m,1} & \cdots & P_{m,n-1} \ P_{m,n} \end{array}$ | 00 00 00 00 00 00<br>00 00 00 00 00 00<br>HORIZONTAL<br>BLANKING<br>00 00 00 00 00 00<br>00 00 00 00 00 00 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 00 00 00 00 00 00<br>00 00 00 00 00 00<br>VERTICAL BLANKING                                                                                                                                                                                                                                          | 00 00 00 00 00 00<br>00 00 00 00 00 00<br>VERTICAL/HORIZONTAL<br>BLANKING                                  |

| 00 00 00 00 00 00<br>00 00 00 00 00 00                                                                                                                                                                                                                                                               | 00 00 00 00 00 00<br>00 00 00 00 00 00                                                                     |

Figure 7. Spatial Illustration of Image Readout

# **Output Data Timing**

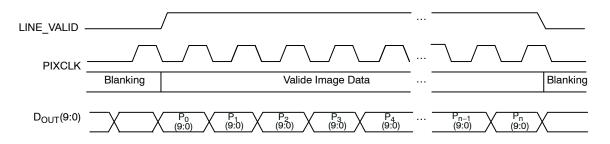

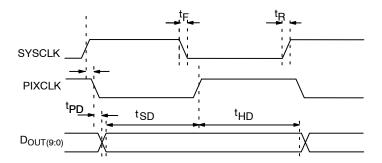

The data output of the MT9V024 is synchronized with the PIXCLK output. When LINE\_VALID (LV) is HIGH, one 10-bit pixel datum is output every PIXCLK period.

Figure 8. Timing Example of Pixel Data

The PIXCLK is a nominally inverted version of the master clock (SYSCLK). This allows PIXCLK to be used as a clock to latch the data. However, when column bin 2 is enabled, the PIXCLK is HIGH for one complete master clock master period and then LOW for one complete master clock period; when column bin 4 is enabled, the PIXCLK is HIGH for two complete master clock periods and then LOW for two complete master clock periods. It is continuously enabled, even during the blanking period. Setting R0x72 bit[4] = 1 causes the MT9V024 to invert the polarity of the PIXCLK.

The parameters P1, A, Q, and P2 in Figure 9 are defined in Table 4.

#### Table 4. FRAME TIME

| Parameter       | Name                 | Equation                                                             | Default Timing at 26.66 MHz                         |

|-----------------|----------------------|----------------------------------------------------------------------|-----------------------------------------------------|

| A               | Active data time     | Context A: R0x04<br>Context B: R0xCC                                 | 752 pixel clocks<br>= 752 master = 28.20 μs         |

| P1              | Frame start blanking | Context A: R0x05 – 23<br>Context B: R0xCD – 23                       | 71 pixel clocks<br>= 71master = 2.66 μs             |

| P2              | Frame end blanking   | 23 (fixed)                                                           | 23 pixel clocks<br>= 23 master = 0.86 μs            |

| Q               | Horizontal blanking  | Context A: R0x05<br>Context B: R0xCD                                 | 94 pixel clocks<br>= 94 master = 3.52 μs            |

| A+Q             | Row time             | Context A: R0x04 + R0x05<br>Context B: R0xCC + R0xCD                 | 846 pixel clocks<br>= 846 master = 31.72 μs         |

| V               | Vertical blanking    | Context A: (R0x03) x (A + Q) + 4<br>Context B: (R0xCB) x (A + Q) + 4 | 38,074 pixel clocks<br>= 38,074 master = 1.43 ms    |

| Nrows x (A + Q) | Frame valid time     | Context A: (R0x03) x (A + Q)<br>Context B: (R0xCB) x (A + Q)         | 406,080 pixel clocks<br>= 406,080 master = 15.23 ms |

| F               | Total frame time     | V + (Nrows x (A + Q))                                                | 444,154 pixel clocks<br>= 444,154 master = 16.66 ms |

Sensor timing is shown above in terms of pixel clock and master clock cycles (refer to Figure 8). The recommended master clock frequency is 26.66 MHz. The vertical blanking and the total frame time equations assume that the integration time (coarse shutter width plus fine shutter width) is less than the number of active rows plus the blanking rows minus the overhead rows: Window Height + Vertical Blanking - 2

(eq. 1)

If this is not the case, the number of integration rows must be used instead to determine the frame time, as shown in Table 4. In this example, it is assumed that the coarse shutter width control is programmed with 523 rows and the fine shutter width total is zero.

For Simultaneous mode, if the exposure time registers (coarse shutter width total plus Fine Shutter Width Total) exceed the total readout time, then the vertical blanking time is internally extended automatically to adjust for the additional integration time required. This extended value is not written back to the vertical blanking registers. The vertical blank register can be used to adjust frame-to-frame readout time. This register does not affect the exposure time but it may extend the readout time.

#### Table 5. FRAME TIME – LONG INTEGRATION TIME

| Parameter | Name                                              | Equation<br>(Number of Master Clock Cycles)                                                                        | Default Timing at 26.66 MHz                        |

|-----------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| V'        | Vertical blanking (long integration time)         | Context A: (R0x0B + 2 - R0x03) ×<br>(A + Q) + R0xD5 + 4<br>Context B: (R0xD2 + 2 - R0xCB) ×<br>(A + Q) + R0xD8 + 4 | 38,074 pixel clocks<br>= 38,074 master = 1.43ms    |

| F"        | Total frame time (long integration exposure time) | $(R0x0B + 2) \times (A + Q) + 4$                                                                                   | 444,154 pixel clocks<br>= 444,154 master = 16.66ms |

4. The MT9V024 uses column parallel analog-digital converters; thus short row timing is not possible. The minimum total row time is 704 columns (horizontal width + horizontal blanking). The minimum horizontal blanking is 61 for normal mode, 71 for column bin 2 mode, and 91 for column bin 4 mode. When the window width is set below 643, horizontal blanking must be increased. In binning mode, the minimum row time is R0x04+R0x05 = 704.

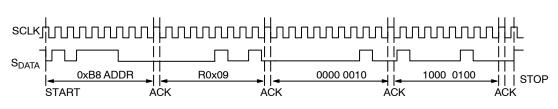

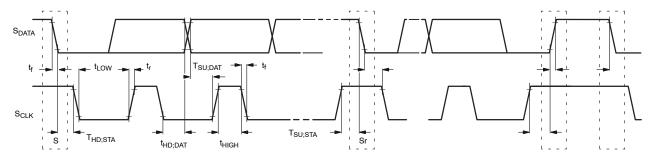

#### SERIAL BUS DESCRIPTION

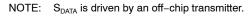

Registers are written to and read from the MT9V024 through the two-wire serial inter-face bus. The MT9V024 is a serial interface slave with four possible IDs (0x90, 0x98, 0xB0 and 0xB8) determined by the S\_CTRL\_ADR0 and S\_CTRL\_ADR1 input pins. Data is transferred into the MT9V024 and out through the serial data (SDATA) line. The SDATA line is pulled up to VDD off-chip by a 1.5 k $\Omega$  resistor. Either the slave or master device can pull the SDATA line down-the serial interface protocol determines which device is allowed to pull the SDATA line down at any given time. The registers are 16-bit wide, and can be accessed through 16-or 8-bit two-wire serial interface sequences.

#### Protocol

- 1. a start bit

- 2. the slave device 8-bit address

- 3. a(n) (no) acknowledge bit

- 4. an 8-bit message

- 5. a stop bit

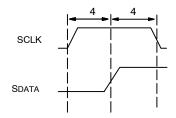

#### Start Bit

The start bit is defined as a HIGH-to-LOW transition of the data line while the clock line is HIGH.

#### **Slave Address**

The 8-bit address of a two-wire serial interface device consists of 7 bits of address and

1 bit of direction. A "0" in the LSB of the address indicates write mode, and a "1" indicates read mode. As indicated above, the MT9V024 allows four possible slave addresses determined by the two input pins, S\_CTRL\_ADR0 and S\_CTRL\_ADR1.

#### Acknowledge Bit

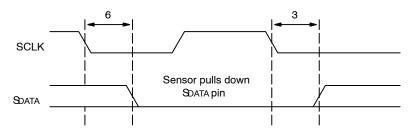

The master generates the acknowledge clock pulse. The transmitter (which is the master when writing, or the slave when reading) releases the data line, and the receiver indicates an acknowledge bit by pulling the data line LOW during the acknowledge clock pulse.

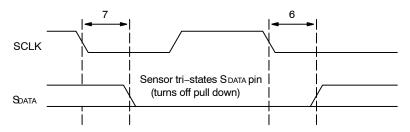

#### No-Acknowledge Bit

The no-acknowledge bit is generated when the data line is not pulled down by the receiver during the acknowledge clock pulse. A no-acknowledge bit is used to terminate a read sequence.

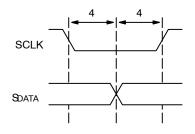

#### Stop Bit

The stop bit is defined as a LOW-to-HIGH transition of the data line while the clock line is HIGH.

#### Sequence

A typical READ or WRITE sequence begins by the master sending a start bit. After the start bit, the master sends the slave device's 8-bit address. The last bit of the address determines if the request is a read or a write, where a "0" indicates a WRITE and a "1" indicates a READ. The slave device acknowledges its address by sending an acknowledge bit back to the master.

If the request was a WRITE, the master then transfers the 8-bit register address to which a WRITE should take place. The slave sends an acknowledge bit to indicate that the register address has been received. The master then transfers the data 8 bits at a time, with the slave sending an acknowledge bit after each 8 bits. The MT9V024 uses 16-bit data for its internal registers, thus requiring two 8-bit transfers to write to one register. After 16 bits are transferred, the register address is automatically incremented, so that the next 16 bits are written to the next register address. The master stops writing by sending a start or stop bit.

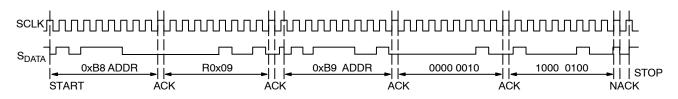

A typical READ sequence is executed as follows. First the master sends the write mode slave address and 8-bit register address, just as in the write request. The master then sends a start bit and the read mode slave address. The master then clocks out the register data 8 bits at a time. The master sends

an acknowledge bit after each 8-bit transfer. The register address is automatically incremented after every 16 bits is transferred. The data transfer is stopped when the master sends a no-acknowledge bit. The MT9V024 allows for 8-bit data transfers through the two-wire serial interface by writing (or reading) the most significant 8 bits to the register and then writing (or reading) the least significant 8 bits to byte-wise address register (0x0F0).

#### **Bus Idle State**

The bus is idle when both the data and clock lines are HIGH. Control of the bus is initiated with a start bit, and the bus is released with a stop bit. Only the master can generate the start and stop bits.

#### Table 6. SLAVE ADDRESS MODES

| {S_CTRL_ADR1, S_CTRL_ADR0} | Slave Address | Write/Read Mode |

|----------------------------|---------------|-----------------|

| 00                         | 0x90          | Write           |

|                            | 0x91          | Read            |

| 01                         | 0x98          | Write           |

|                            | 0x99          | Read            |

| 10                         | 0xB0          | Write           |

|                            | 0xB1          | Read            |

| 11                         | 0xB8          | Write           |

|                            | 0xB9          | Read            |

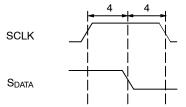

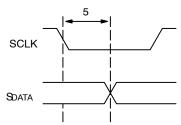

#### Data Bit Transfer

One data bit is transferred during each clock pulse. The two-wire serial interface clock pulse is provided by the master. The data must be stable during the HIGH period of the serial clock-it can only change when the two-wire serial interface clock is LOW. Data is transferred 8 bits at a time, followed by an acknowledge bit.

#### TWO-WIRE SERIAL INTERFACE SAMPLE READ AND WRITE SEQUENCES

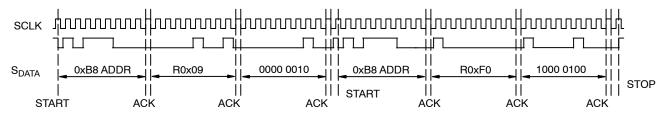

#### **16-Bit Write Sequence**

A typical write sequence for writing 16 bits to a register is shown in Figure 10. A start bit given by the master, followed by the write address, starts the sequence. The image sensor then gives an acknowledge bit and expects the register address to come first, followed by the 16-bit data. After each 8-bit word is sent, the image sensor gives an acknowledge bit. All 16 bits must be written before the register is updated. After 16 bits are transferred, the register address is automatically incremented, so that the next 16 bits are written to the next register. The master stops writing by sending a start or stop bit.

Figure 10. Timing Diagram Showing a Write to R0x09 with Value 0x0284

#### 16-Bit Read Sequence

A typical read sequence is shown in Figure 11. First the master has to write the register address, as in a write sequence. Then a start bit and the read address specify that a read is about to happen from the register. The master then

clocks out the register data 8 bits at a time. The master sends an acknowledge bit after each 8-bit transfer. The register address is auto-incremented after every 16 bits is transferred. The data transfer is stopped when the master sends a no-acknowledge bit.

Figure 11. Timing Diagram Showing a Read from R0x09; Returned Value 0x0284

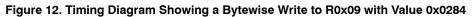

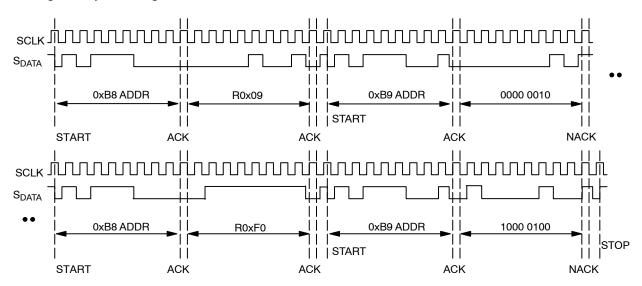

# 8-Bit Write Sequence

To be able to write 1 byte at a time to the register, a special register address is added. The 8-bit write is done by first writing the upper 8 bits to the desired register and then writing the lower 8 bits to the special register address

(R0xF0). The register is not updated until all 16 bits have been written. It is not possible to just update half of a register. In Figure 12, a typical sequence for 8-bit writing is shown. The second byte is written to the special register (R0xF0).

# 8-Bit Read Sequence

To read one byte at a time the same special register address is used for the lower byte. The upper 8 bits are read from the desired register. By following this with a read from the byte-wise address register (R0xF0) the lower 8 bits are accessed (Figure 13). The master sets the no-acknowledge bits shown.

Figure 13. Timing Diagram Showing a Bytewise Read from R0x09; Returned Value 0x0284

# **Register Lock**

Included in the MT9V024 is a register lock (R0xFE) feature that can be used as a solution to reduce the probability of an inadvertent noise-triggered two-wire serial interface write to the sensor. All registers, or only read mode registers – R0x0D and R0x0E can be locked. It is important to prevent an inadvertent two-wire serial interface write to the read mode registers in automotive applications since this register controls the image

orientation and any unintended flip to an image can cause serious results.

At power-up, the register lock defaults to a value of 0xBEEF, which implies that all registers are unlocked and any two-wire serial interface writes to the register get committed.

# Lock All Registers

If a unique pattern (0xDEAD) to R0xFE is programmed, any subsequent two-wire serial interface writes to registers (except R0xFE) are NOT committed. Alternatively, if the user writes a 0xBEEF to the register lock register, all registers are unlocked and any subsequent two-wire serial interface writes to the register are committed.

# Lock Only Read More Registers (R0x0D and R0x0E)

If a unique pattern (0xDEAF) to R0xFE is programmed, any subsequent two–wire serial interface writes to register 13 are NOT committed. Alternatively, if the user writes a 0xBEEF to register lock register, register 13 is unlocked and any subsequent two-wire serial interface writes to this register are committed.

# **REAL-TIME CONTEXT SWITCHING**

In the MT9V024, the user may switch between two full register sets (listed in Table 7) by writing to a context switch change bit in register 0x07. This context switch will change all registers (no shadowing) at the frame start time and have the new values apply to the immediate next exposure and readout time (frame n+1), except for shutter width and V1–V4 control, which will take effect for next exposure but will show up in the n+2 image.

| Table 7. REAL-TIME CONTEXT-SWITCHABLE REGISTERS |  |

|-------------------------------------------------|--|

|                                                 |  |

| Register Name                  | Register Number (Hex) For Context A | Register Number (Hex) for<br>Context B |

|--------------------------------|-------------------------------------|----------------------------------------|

| Column Start                   | 0x01                                | 0xC9                                   |

| Row Start                      | 0x02                                | 0xCA                                   |

| Window Height                  | 0x03                                | 0xCB                                   |

| Window Width                   | 0x04                                | 0xCC                                   |

| Horizontal Blanking            | 0x05                                | 0xCD                                   |

| Vertical Blanking              | 0x06                                | 0xCE                                   |

| Coarse Shutter Width 1         | 0x08                                | 0xCF                                   |

| Coarse Shutter Width 2         | 0x09                                | 0xD0                                   |

| Coarse Shutter Width Control   | 0x0A                                | 0xD1                                   |

| Coarse Shutter Width Total     | 0x0B                                | 0xD2                                   |

| Fine Shutter Width 1           | 0xD3                                | 0xD6                                   |

| Fine Shutter Width 2           | 0xD4                                | 0xD7                                   |

| Fine Shutter Width Total       | 0xD5                                | 0xD8                                   |

| Read Mode                      | 0x0D [5:0]                          | 0x0E [5:0]                             |

| High Dynamic Range enable      | 0x0F [0]                            | 0x0F [8]                               |

| ADC Resolution Control         | 0x1C [1:0]                          | 0x1C [9:8]                             |

| V1 Control – V4 Control        | 0x31 – 0x34                         | 0x39 – 0x3C                            |

| Analog Gain Control            | 0x35                                | 0x36                                   |

| Row Noise Correction Control 1 | 0x70 [1:0]                          | 0x70 [9:8]                             |

| Tiled Digital Gain             | 0x80 [3:0] – 0x98 [3:0]             | 0x80 [11:8] – 0x98 [11:8]              |

| AEC/AGC Enable                 | 0xAF [1:0]                          | 0xAF [9:8]                             |

# **RECOMMENDED REGISTER SETTINGS**

Table 8 describes new suggested register settings, and descriptions of performance improvements and conditions:

| Register | Current Default | New Setting | Performance Impact                                                                                                                                                                                                                                                                                       |

|----------|-----------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R0x20    | 0x01C1          | 0x03C7      | Recommended by design to improve performance in HDR<br>mode and when frame rate is low. We also recommended<br>using R0x13 = 0x2D2E with this setting for better column<br>FPN. NOTE: When coarse integration time set to 0 and fine<br>integration time less than 456, R0x20 should be set to<br>0x01C7 |

| R0x24    | 0x0010          | 0x001B      | Corrects pixel negative dark offset when global reset in R0x20[9] is enabled.                                                                                                                                                                                                                            |

| R0x2B    | 0x0004          | 0x0003      | Improves column FPN.                                                                                                                                                                                                                                                                                     |

| R0x2F    | 0x0004          | 0x0003      | Improves FPN at near-saturation.                                                                                                                                                                                                                                                                         |

# Table 8. RECOMMENDED REGISTER SETTINGS AND PERFORMANCE IMPACT (RESERVED REGISTERS)

# FEATURE DESCRIPTION

#### **Operational Modes**

The MT9V024 works in master, snapshot, or slave mode. In master mode the sensor generates the readout timing. In snapshot mode it accepts an external trigger to start integration, then generates the readout timing. In slave mode the sensor accepts both external integration and readout controls. The integration time is programmed through the two–wire serial interface during master or snapshot modes, or controlled through an externally generated control signal during slave mode.

#### Master Mode

There are two possible operation methods for master mode: simultaneous and sequential. One of these operation modes must be selected through the two-wire serial inter-face. Additional details on this mode can be found in AND9255/D Master Exposure Mode Operation.

#### Simultaneous Master Mode

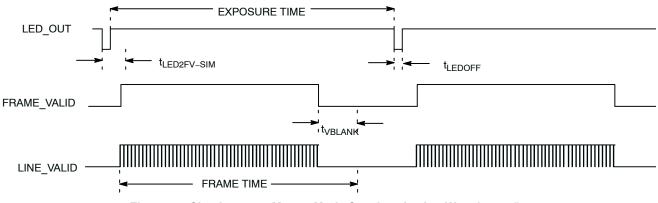

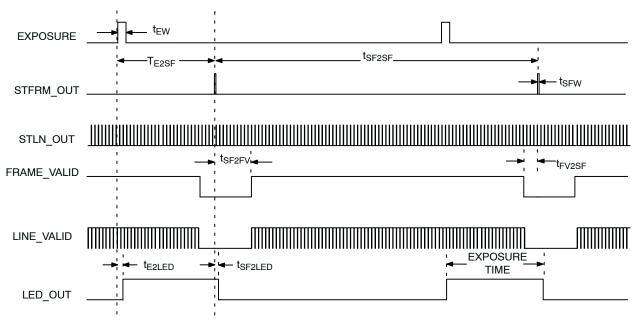

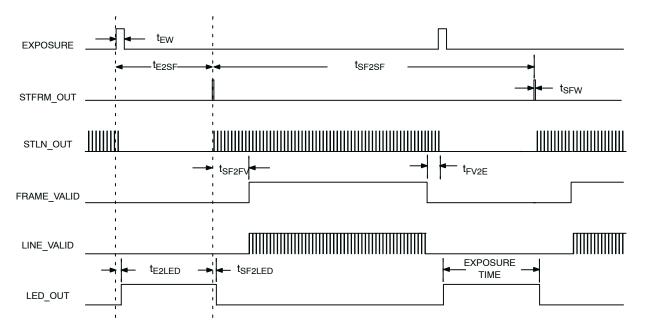

In simultaneous master mode, the exposure period occurs during readout. The frame synchronization waveforms are shown in Figure 14 and Figure 15. The exposure and readout happen in parallel rather than sequential, making this the fastest mode of operation.

Figure 14. Simultaneous Master Mode Synchronization Waveforms #1

Figure 15. Simultaneous Master Mode Synchronization Waveforms #2

When exposure time is greater than the sum of vertical blank and window height, the number of vertical blank rows is increased automatically to accommodate the exposure time.

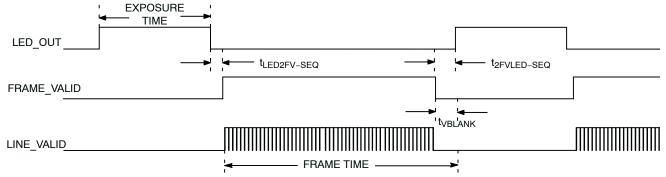

#### **Sequential Master Mode**

In sequential master mode the exposure period is followed by readout. The frame synchronization waveforms for sequential master mode are shown in Figure 16. The frame rate changes as the integration time changes.

Figure 16. Simultaneous Master Mode Synchronization Waveforms

# **Snapshot Mode**

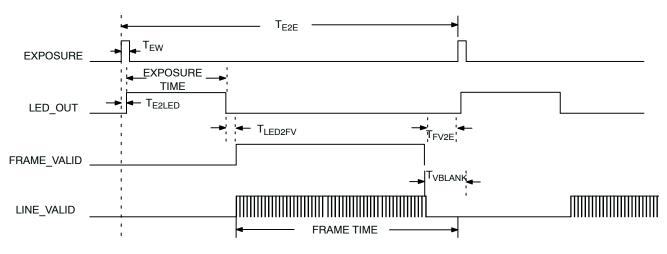

In snapshot mode the sensor accepts an input trigger signal which initiates exposure, and is immediately followed by readout. Figure 17 shows the interface signals used in snapshot mode. In snapshot mode, the start of the integration period is determined by the externally applied EXPOSURE pulse that is input to the MT9V024. The integration time is preprogrammed at R0x0B or R0xD2 through the two-wire serial interface. After the frame's integration period is complete the readout process commences and the syncs and data are output. Sensor in snapshot mode can capture a single image or a sequence of images. The frame rate may only be controlled by changing the period of the user supplied EXPOSURE pulse train. The frame synchronization waveforms for snapshot mode are shown in Figure 18. Additional details on this mode can be found in AND9248/D–Snapshot Exposure Mode Operation.

Figure 17. Snapshot Mode Interface Signals

Figure 18. Snapshot Mode Frame Synchronization Waveforms

#### **Slave Mode**

In slave mode, the exposure and readout are controlled using the EXPOSURE, STFRM\_OUT, and STLN\_OUT pins. When the slave mode is enabled, STFRM\_OUT and STLN\_OUT become input pins.

The start and end of integration are controlled by EXPOSURE and STFRM\_OUT pulses, respectively. While a STFRM\_OUT pulse is used to stop integration, it is also used to enable the readout process.

After integration is stopped, the user provides STLN\_OUT pulses to trigger row readout. A full row of data is read out with each STLN\_OUT pulse. The user must provide enough time between successive STLN\_OUT pulses to allow the complete readout of one row.

It is also important to provide additional STLN\_OUT pulses to allow the sensors to read the vertical blanking rows. It is recommended that the user program the vertical blank register (R0x06) with a value of 4, and achieve additional vertical blanking between frames by delaying the application of the STFRM\_OUT pulse.

The elapsed time between the rising edge of STLN\_OUT and the first valid pixel data is calculated for context A by [horizontal blanking register (R0x05) + 4] clock cycles. For context B, the time is (R0xCD + 4) clock cycles.

Additional details on this mode can be found in AND9241/D – Slave Exposure Mode Operation.

Figure 19. Exposure and Readout Timing (Simultaneous Mode)

NOTES: 1. No drawn to scale.

- 2. Frame readout shortened for clarity.

- 3. Simultaneous progressive scan readout mode shown.

Figure 20. Exposure and Readout Timing (Sequential Mode)

NOTES: 1. Not drawn to scale.

- 2. Frame readout shortened for clarity

- 3. STLN OUT pulses are optional during exposure time.

- 4. Sequential progressive scan readout mode shown.

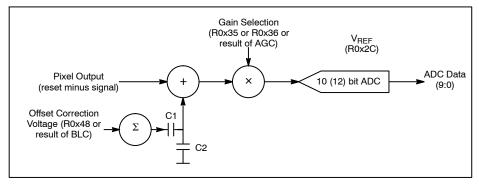

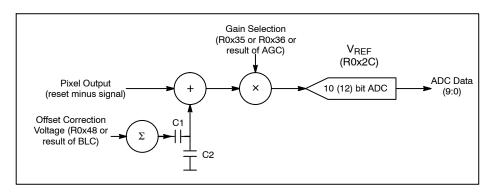

#### Signal Path

The MT9V024 signal path consists of a programmable gain, a programmable analog offset, and a 10-bit ADC. See

"Black Level Calibration" for the programmable offset operation description.

Figure 21. Signal Path

# **ON-CHIP BIASES**

#### **ADC Voltage Reference**

The ADC voltage reference is programmed through R0x2C, bits 2:0. The ADC reference ranges from 1.0 V to 2.1 V. The default value is 1.4 V. The increment size of the voltage reference is 0.1 V from 1.0 V to 1.6 V (R0x2C[2:0] values 0 to 6). At R0x2C[2:0] = 7, the reference voltage jumps to 2.1 V.

It is very important to preserve the correct values of the other bits in R0x2C. The default register setting is 0x0004. This corresponds to 1.4 V-at this setting 1 mV input to the ADC equals approximately 1 LSB.

#### V\_Step Voltage Reference

This voltage is used for pixel high dynamic range operations, programmable from R0x31 through R0x34 for context A, or R0x39 through R0x3B for context B.

#### **Chip Version**

Chip version register R0x00 is read-only.

#### WINDOW CONTROL

Registers column start A/B, row start A/B, window height A/B (row size), and window width (column size) A/B control the size and starting coordinates of the window.

The values programmed in the window height and width registers are the exact window height and width out of the sensor. The window start value should never be set below four.

To read out the dark rows set bit 6 of R0x0D. In addition, bit 7 of R0x0D can be used to display the dark columns in the image. Note that there are Show Dark settings only for context A.

# **BLANKING CONTROL**

Horizontal blank and vertical blank registers R0x05 and R0x06 (B: 0xCD and R0xCE), respectively, control the blanking time in a row (horizontal blanking) and between frames (vertical blanking).

- Horizontal blanking is specified in terms of pixel clocks.

- Vertical blanking is specified in terms of numbers of rows.

The actual imager timing can be calculated using Tables 4 and 5, which describe "Row Timing and FV/LV signals." The minimum number of vertical blank rows is 4.

# **PIXEL INTEGRATION CONTROL**

# **Total Integration**

Total integration time is the result of coarse shutter width and fine shutter width registers, and depends also on whether manual or automatic exposure is selected.

The actual total integration time, t<sub>INT</sub> is defined as:

$t_{INT} = t_{INTCoarse} + t_{INTint}$  (eq. 2)

= (number of rows of integration × row time)

+ (number of pixels of integration × pixel time)

where:

• Number of Rows of Integration

(Auto Exposure Control: Enabled)

When automatic exposure control (AEC) is enabled, the number of rows of integration may vary from frame to frame, with the limits controlled by R0xAC (minimum coarse shutter width) and R0xAD (maximum coarse shutter width).

• Number of Rows of Integration (Auto Exposure Control: Disabled) If AEC is disabled, the number of rows of integration equals the value in R0x0B. or If context B is enabled, the number of rows of integration equals the value in R0xD2.

- Number of pixels of Integration The number of fine shutter width pixels is independent of AEC mode (enabled or disabled):

- Context A: the number of pixels of integration equals the values in R0xD5.

- Context B: the number of pixels of integration equals the value in R0xD8.

# **Row Timing**

Context A:

Row time = (R0x04 + R0x05)master clock periods (eq. 3)

Context B:

Row time = (R0xCC + R0xCD) master clock periods (eq. 4)

Typically, the value of the Coarse Shutter Width Total registers is limited to the number of rows per frame (which includes vertical blanking rows), such that the frame rate is not affected by the integration time. If the Coarse Shutter Width Total is increased beyond the total number of rows per frame, the user must add additional blanking rows using the Vertical Blanking registers as needed. See descriptions of the Vertical Blanking registers, R0x06 and R0xCE in Tables 1and 2 of the MT9V024 register reference.

A second constraint is that  $t_{INT}$  must be adjusted to avoid banding in the image from light flicker. Under 60 Hz flicker, this means the frame time must be a multiple of 1/120 of a second. Under 50 Hz flicker, the frame time must be a multiple of 1/100 of a second.

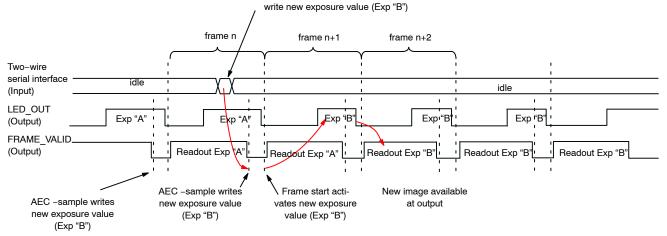

# **Changes to Integration Time**

With automatic exposure control disabled (R0xAF[0] for context A, or R0xAF[8] for context B) and if the total integration time (R0x0B or R0xD2) is changed through the two-wire serial interface while FV is asserted for frame n, the first frame output using the new integration time is frame (n + 2). Similarly, when automatic exposure control is enabled, any change to the integration time for frame n first appears in frame (n + 2) output. Additional details on this latency can be found in AND9251/D – Latency of Exposure or Gain Switch. The sequence is as follows:

- 1. During frame *n*, the new integration time is held in the R0x0B or R0D2 live register.

- 2. Prior to the start of frame (n + 1) readout, the new integration time is transferred to the exposure control module. Integration for each row of frame (n + 1) has been completed using the old integration time. The earliest time that a row can start integrating using the new integration time is immediately after that row has been read for frame

(n + 1). The actual time that rows start integrating using the new integration time is dependent on the new value of the integration time.

3. When frame (n + 2) is read out, it is integrated using the new integration time. If the integration time is changed (R0x0B or R0xD2 written) on successive frames, each value written is applied to a single frame; the latency between writing a value and it affecting the frame readout remains at two frames.

Figure 22. Latency of Exposure Register in Master Mode

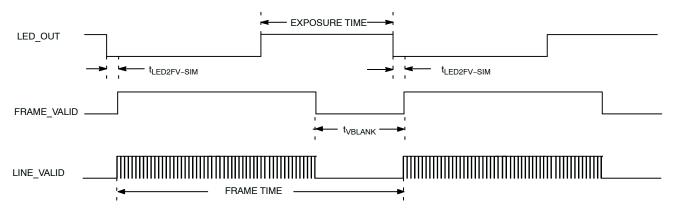

# **Exposure Indicator**

The exposure indicator is controlled by:

• R0x1B LED OUT Control

The MT9V024 provides an output pin, LED\_OUT, to indicate when the exposure takes place. When R0x1B bit 0 is clear, LED\_OUT is HIGH during exposure. By using R0x1B, bit 1, the polarity of the LED\_OUT pin can be inverted.

# High Dynamic Range

High dynamic range is controlled by:

# Table 9. HIGH DYNAMIC RANGE

|                       | Context A   | Context B   |

|-----------------------|-------------|-------------|

| High Dynamic Enable   | R0x0F[0]    | R0x0F[8]    |

| Shutter Width 1       | R0x08       | R0xCF       |

| Shutter Width 2       | R0x09       | R0xD0       |

| Shutter Width Control | R0x0A       | R0xD1       |

| V_Step Voltages       | R0x31-R0x34 | R0x39-R0x3C |

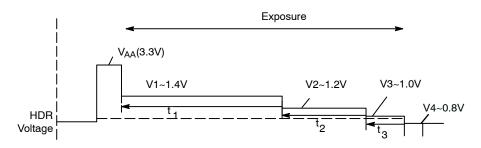

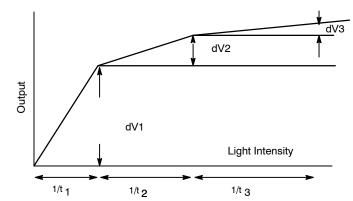

In the MT9V024, high dynamic range (by setting R0x0F, bit 0 or 8 to 1) is achieved by controlling the saturation level of the pixel (HDR or high dynamic range gate) during the exposure period. The sequence of the control voltages at the HDR gate is shown in Figure 23. After the pixels are reset, the step voltage, V\_Step, which is applied to HDR gate, is set up at V1 for integration time  $t_1$ , then to V2 for time  $t_2$ , then V3 for time  $t_3$ , and finally it is parked at V4, which also serves as an antiblooming voltage for the photodetector. This sequence of voltages leads to a piecewise linear pixel response, illustrated (approximately) in Figure 23 and in Figure 24.

Figure 23. Sequence of Control Voltages at the HDR Gate

Figure 24. Sequence of Voltages in a Piecewise Linear Pixel Response

The parameters of the step voltage V\_Step, which take values V1, V2, and V3, directly affect the position of the knee points in Figure 24.

Light intensities work approximately as a reciprocal of the partial exposure time. Typically, <sup>1</sup>1 is the longest exposure, <sup>1</sup>2 shorter, and so on. Thus the range of light intensities is shortest for the first slope, providing the highest sensitivity.

The register settings for V\_Step and partial exposures are: V1 = R0x31, bits 5:0 (Context B: R0x39, bits 5:0) V2 = R0x32, bits 5:0 (Context B: R0x3A, bits 5:0) V3 = R0x33, bits 5:0 (Context B: R0x3B, bits 5:0) V4 = R0x34, bits 5:0 (Context B: R0x3C, bits 5:0)  $t_{INT} = t_1 + t_2 + t_3$

There are two ways to specify the knee points timing, the first by manual setting and the second by automatic knee point adjustment. Knee point auto adjust is controlled for context A by R0x0A[8] (where default is ON), and for context B by R0xD1[8] (where default is OFF ).

When the knee point auto adjust enabler is enabled (set HIGH), the MT9V024 calculates the knee points automatically using the following equations:

1

$$l_1 = l_{\rm INT} - l_2 - l_3$$

(eq. 5)

$t_2 = t_{INT} x(1/2)^{R0x0A[3:0]orR0xD1[3:0]}$  (eq. 6)

$$t_3 = t_{INT} x(1/2)^{R0x0A[7:4]orR0xD1[7:4]}$$

(eq. 7)

As a default for auto exposure,  $t_2$  is 1/16 of  $t_{INT}$ ,  $t_3$  is 1/64 of  $t_{INT}$ .

When the auto adjust enabler is disabled (set LOW),  $t_1$ ,  $t_2$ , and  $t_3$  may be programmed through the two-wire serial interface:

$$t_1 = \text{Coarse SW1(row - times)} + \text{Fine SW1(pixel - times)}$$

$t_3 = Total Integration - t_1 - t_2$

+ Fine Shutter Width Totall

$$-t_1 - t_2$$

For context A these become:

$$t_1 = R0x08 + R0xD3$$

(eq. 11)

$$t_3 = R0x09 - R0x08 + R0xD4 - R0xD3$$

(eq. 12)

$$t_3 = R0x0B + R0xD4 - t_1 - t_2$$

(eq. 13)

For context B these are:

$$t_1 = R0xCF + R0xD6$$

(eq. 14)

$$t_3 = R0xD0 - R0xCF + R0xD7 - R0xD6$$

(eq. 15)

$$t_3 = R0xD2 + R0xD8 - t_1 - t_2$$

(eq. 16)

In all cases above, the coarse component of total integration time may be based on the result of AEC or values in R0x0B and R0xD2, depending on the settings.

Similar to Fine Shutter Width Total registers, the user must not set the Fine Shutter Width 1 or Fine Shutter Width 2 register to exceed the row time (Horizontal Blanking + Window Width). The absolute maximum value for the Fine Shutter Width registers is 1774 master clocks. enabled by the ADC Companding Mode register. This mode allows higher ADC resolution, which means less quantization noise at low light, and lower resolution at high light, where good ADC quantization is not so critical because of the high level of the photon's shot noise.

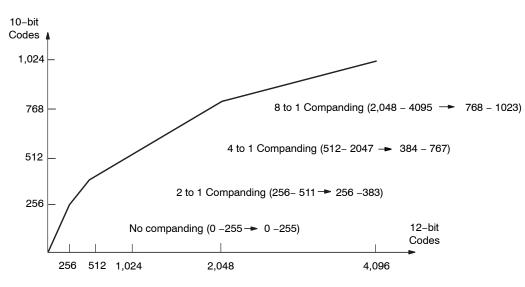

#### **ADC Companding Mode**

By default, ADC resolution of the sensor is 10-bit. Additionally, a companding scheme of 12-bit into 10-bit is

Figure 25. 12- to 10-Bit Companding Chart

#### **GAIN SETTINGS**

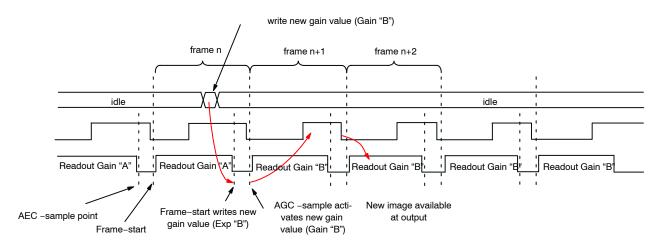

#### **Changes to Gain Settings**

When the analog gain (R0x35 for context A or R0x36 for context B) or the digital gain settings (R0x80–R0x98) are changed, the gain is updated on the next frame start. The gain setting must be written before the frame boundary to take effect the next frame. The frame boundary is slightly after

the falling edge of Frame\_Valid. In Figure 26 this is shown by the dashed vertical line labeled Frame Start.

Both analog and digital gain change regardless of whether the integration time is also changed simultaneously. Digital gain will change as soon as the register is written. Additional details on this latency can be found in AND9251/D Latency of Exposure or Gain Switch.

Figure 26. Latency of Gain Register(s) in Master Mode

# Analog Gain

Analog gain is controlled by:

- R0x35 Global Gain context A

- R0x36 Global Gain context B

The formula for gain setting is:

Gain = Bits[6 : 0] x 0.0625 (eq. 17)

The analog gain range supported in the MT9V024 is 1X-4X with a step size of 6.25 percent. To control gain manually with this register, the sensor must NOT be in AGC mode. When adjusting the luminosity of an image, it is recommended to alter exposure first and yield to gain increases only when the exposure value has reached a maximum limit.

Analog gain = bits (6:0) x 0.0625 for values 16-31

Analog gain = bits  $(6:0)/2 \ge 0.125$  for values 32–64

For values 16–31: each LSB increases analog gain 0.0625v/v. A value of 16 = 1X gain.

Range: 1X to 1.9375X.

For values 32-64: each 2 LSB increases analog gain 0.125v/v (that is, double the gain increase for 2 LSB). Range: 2X to 4X. Odd values do not result in gain increases; the gain increases by 0.125 for values 32, 34, 36, and so on.

# **Digital Gain**

Digital gain is controlled by:

- R0x99-R0xA4 Tile Coordinates

- R0x80-R0x98 Tiled Digital Gain and Weight

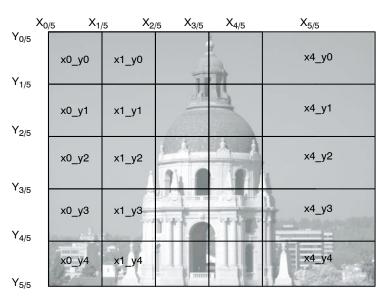

In the MT9V024, the gain logic divides the image into 25 tiles, as shown in Figure 27. The size and gain of each tile can be adjusted using the above digital gain control registers. Separate tile gains can be assigned for context A and context B.

Registers 0x99-0x9E and 0x9F-0xA4 represent the coordinates X0/5-X5/5 and Y0/5-Y5/5 in Figure 27, respectively.

Digital gains of registers 0x80-0x98 apply to their corresponding tiles. The MT9V024 supports a digital gain of 0.25-3.75X.

When binning is enabled, the tile offsets maintain their absolute values; that is, tile coordinates do not scale with row or column bin setting. Digital gain is applied as soon as register is written.

NOTE: There is one exception, for the condition when Column Bin 4 is enabled (R0x0D[3:2] or R0x0E[3:2] = 2). For this case, the value for Digital Tile Coordinate X-direction must be doubled.

The formula for digital gain setting is:

Digital Gain = Bits[3 : 0] x 0.25

(eq. 18)

Figure 27. Tiled Sample

# Black Level Calibration

Black level calibration is controlled by:

- Frame Dark Average: R0x42

- Dark Average Thresholds: R0x46

- Black Level Calibration Control: R0x47

- Black Level Calibration Value: R0x48

• Black Level Calibration Value Step Size: R0x4C

The MT9V024 has automatic black level calibration on-chip, and if enabled, its result may be used in the offset correction shown in Figure 28.

Figure 28. Black Level Calibration Flow Chart

The automatic black level calibration measures the average value of pixels from 2 dark rows (1 dark row if row bin 4 is enabled) of the chip. (The pixels are averaged as if they were light-sensitive and passed through the appropriate gain.)

This row average is then digitally low-pass filtered over many frames (R0x47, bits 7:5) to remove temporal noise and random instabilities associated with this measurement.

Then, the new filtered average is compared to a minimum acceptable level, low threshold, and a maximum acceptable level, high threshold.

If the average is lower than the minimum acceptable level, the offset correction voltage is increased by a programmable offset LSB in R0x4C. (Default step size is 2 LSB Offset = 1 ADC LSB at analog gain = 1X.)

If it is above the maximum level, the offset correction voltage is decreased by 2 LSB (default).

To avoid oscillation of the black level from below to above, the region the thresholds should be programmed so the difference is at least two times the offset DAC step size.

In normal operation, the black level calibration value/offset correction value is calculated at the beginning of each frame and can be read through the two-wire serial inter-face from R0x48. This register is an 8-bit signed two's complement value.

However, if R0x47, bit 0 is set to "1," the calibration value in R0x48 is used rather than the automatic black level calculation result. This feature can be used in conjunction with the "show dark rows" feature (R0x0D[6]) if using an external black level calibration circuit.

The offset correction voltage is generated according to the following formulas:

| OffsetCorrectionVoltage = (8 - bit signed two's complement calibration value, 127 $	imes$ 0.25mV | (eq. 19) |

|--------------------------------------------------------------------------------------------------|----------|

|--------------------------------------------------------------------------------------------------|----------|

ADC input voltage = (Pixel Output Voltage) \* Analog Gain + Offset Correction Voltage × (AnalogGain + 1) (eq. 20)

#### **Defective Pixel Correction**

Defective pixel correction is intended to compensate for defective pixels by replacing their value with a value based on the surrounding pixels, making the defect less notice– able to the human eye. The locations of defective pixels are stored in a ROM on chip during the manufacturing process; the maximum number of defects stored is 32. There is no provision for later augmenting the table of programmed defects. In the defect correction block, bad pixels will be substituted by either the average of its neighboring pixels, or its nearest–neighbor pixel, depending on pixel location.

Defective Pixel Correction is enabled by R0x07[9]. By default, correction is enabled, and pixels mapped in internal ROM are replaced with corrected values. This might be unacceptable to some applications, in which case pixel correction should be disabled (R0x07[9] = 0).

For complete details on using Defective Pixel Correction, refer to AND9554/D, "Defective Pixel Correction – Description and Usage".

#### **Row-wise Noise Correction**

Row-wise noise correction is controlled by the following registers:

- R0x70 Row Noise Control

- R0x72 Row Noise Constant

Row-wise noise cancellation is performed by calculating a row average from a set of optically black pixels at the start of each row and then applying each average to all the active pixels of the row. Read Dark Columns register bit and Row Noise Correction Enable register bit must both be set to enable row-wise noise cancellation to be performed. The behavior when Read Dark Columns register bit = 0 and Row Noise Correction Enable register bit = 1 is undefined.

The algorithm works as follows:

Logical columns 755–790 in the pixel array provide 36 optically black pixel values. Of the 36 values, two smallest value and two largest values are discarded. The remaining 32 values are averaged by summing them and discarding the 5 LSB of the result. The 10–bit result is subtracted from each pixel value on the row in turn. In addition, a positive constant will be added (Reg0x71, bits 7:0). This constant should be set to the dark level targeted by the black level algorithm plus the noise expected on the measurements of the averaged

values from dark columns; it is meant to prevent clipping from negative noise fluctuations.

Pixel value = ADC value - dark column average + R0x71[9 : 0] (eq. 21)

Note that this algorithm does not work in color sensor.

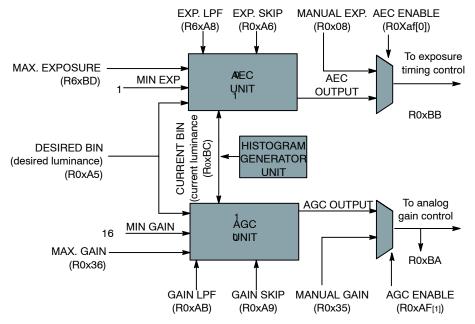

#### Automatic Gain Control and Automatic Exposure Control

The integrated AEC/AGC unit is responsible for ensuring that optimal auto settings of exposure and (analog) gain are computed and updated every frame.

AEC and AGC can be individually enabled or disabled by R0xAF. When AEC is disabled (R0xAF[0] = 0), the sensor uses the manual exposure value in coarse and fine shutter width registers. When AGC is disabled (R0xAF[1] = 0), the sensor uses the manual gain value in R0x35 or R0x36. See "Pixel Integration Control" for more information.

Figure 29. Controllable and Observable AEC/AGC Registers

The exposure is measured in row-time by reading R0xBB. The exposure range is 1 to 2047. The gain is measured in gain-units by reading R0xBA. The gain range is 16 to 63 (unity gain = 16 gain-units; multiply by 1/16 to get the true gain).

When AEC is enabled (R0xAF), the maximum auto exposure value is limited by R0xBD; minimum auto exposure is limited by AEC Minimum Exposure, R0xAC.

NOTE: AEC does not support sub-row timing; calculated exposure values are rounded down to the nearest row-time. For smoother response, manual control is recommended for short exposure times.

When AGC is enabled (R0xAF), the maximum auto gain value is limited by R0xAB; minimum auto gain is fixed to 16 gain–units.

The exposure control measures current scene luminosity and desired output luminosity by accumulating a histogram of pixel values while reading out a frame. All pixels are used, whether in color or mono mode. The desired exposure and gain are then calculated from this for subsequent frame. When binning is enabled, tuning of the AEC may be required. The histogram pixel count register, R0xB0, may be adjusted to reflect reduced pixel count. Desired bin register, R0xA5, may be adjusted as required.

#### **Pixel Clock Speed**

The pixel clock speed is same as the master clock (SYSCLK) at 26.66 MHz by default. However, when column binning 2 or 4 (R0x0D or R0x0E, bit 2 or 3) is enabled, the pixel clock speed is reduced by half and one-fourth of the master clock speed respectively. See "Read Mode Options" and "Column Binning" for additional information.

#### Hard Reset of Logic

The RC circuit for the MT9V024 uses a 10 k $\Omega$  resistor and a 0.1  $\mu F$  capacitor. The rise time for the RC circuit is 1  $\mu s$  maximum.

#### Soft Reset of Logic

Soft reset of logic is controlled by:

R0x0C Reset

Bit 0 is used to reset the digital logic of the sensor while preserving the existing two-wire serial interface configuration. Furthermore, by asserting the soft reset, the sensor aborts the current frame it is processing and starts a new frame. Bit 1 is a shadowed reset control register bit to explicitly reset the automatic gain and exposure control feature.

These two bits are self-resetting bits and also return to "0" during two-wire serial inter-face reads.

#### **STANDBY Control**

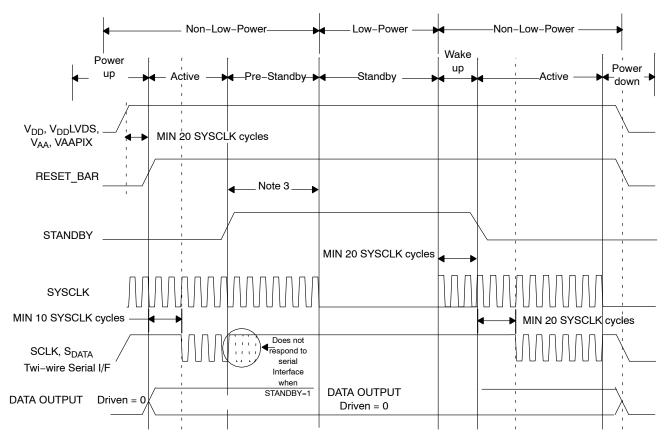

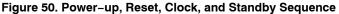

The sensor goes into standby mode by setting STANDBY to HIGH. Once the sensor detects that STANDBY is asserted, it completes the current frame before disabling the digital logic, internal clocks, and analog power enable signal. To release the sensor out from the standby mode, reset STANDBY back to LOW. The LVDS must be powered to ensure that the device is in standby mode. See "Appendix A: Power–On Reset and Standby Timing" for more information on standby.

#### **Monitor Mode Control**

Monitor mode is controlled by:

- R0xD9 Monitor Mode Enable

- R0xC0 Monitor Mode Image Capture Control

The sensor goes into monitor mode when R0xD9[0] is set to HIGH. In this mode, the sensor first captures

a programmable number of frames (R0xC0), then goes into a sleep period for five minutes. The cycle of sleeping for five minutes and waking up to capture a number of frames continues until R0xD9[0] is cleared to return to normal operation.

In some applications when monitor mode is enabled, the purpose of capturing frames is to calibrate the gain and exposure of the scene using automatic gain and exposure control feature. This feature typically takes less than 10 frames to settle. In case a larger number of frames is needed, the value of R0xC0 may be increased to capture more frames.

During the sleep period, none of the analog circuitry and a very small fraction of digital logic (including a five-minute timer) is powered. The master clock (SYSCLK) is therefore always required.

# **READ MODE OPTIONS**

(Also see "Output Data Format" and "Output Data Timing".)

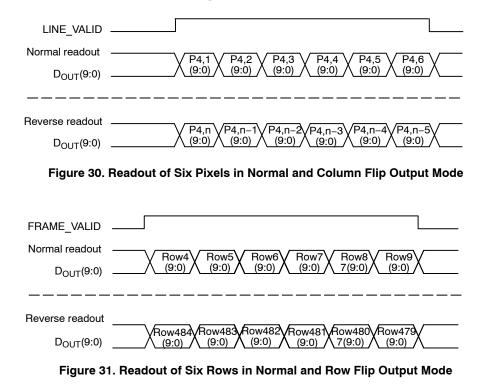

# Column Flip

By setting bit 5 of R0x0D or R0x0E the readout order of the columns is reversed, as shown in Figure 30.

#### **Row Flip**

By setting bit 4 of R0x0D or R0x0E the readout order of the rows is reversed, as shown in Figure 31.

#### **Pixel Binning**

In addition to windowing mode in which smaller resolutions (CIF, QCIF) are obtained by selecting a smaller window from the sensor array, the MT9V024 also provides

the ability to down-sample the entire image captured by the pixel array using pixel binning.

There are two resolution options: binning 2 and binning 4, which reduce resolution by two or by four, respectively. Row

and column binning are separately selected. Image mirroring options will work in conjunction with binning.

For column binning, either two or four columns are combined by averaging to create the resulting column. For row binning, the binning result value depends on the difference in pixel values: for pixel signal differences of less than 200 LSBs, the result is the average of the pixel values. For pixel differences of greater than 200 LSBs, the result is the value of the darker pixel value.

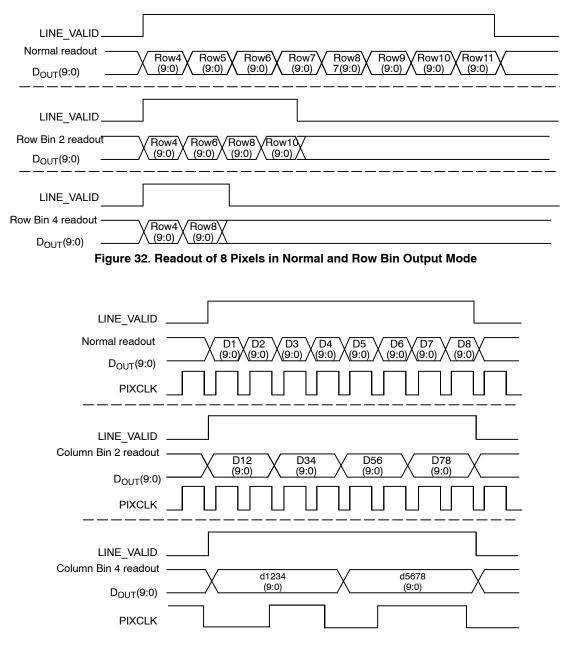

#### **Row Binning**

By setting bit 0 or 1 of R0x0D or R0x0E, only half or one-fourth of the row set is read out, as shown in Figure 32. The number of rows read out is half or one-fourth of the value set in R0x03. The row binning result depends on the difference in pixel values: for pixel signal differences less than 200 LSBs, the result is the average of the pixel values.

For pixel differences of 200 LSBs or more, the result is the value of the darker pixel value.

#### **Column Binning**

For column binning, either two or four columns are combined by averaging to create the result. In setting bit 2 or 3 of R0x0D or R0x0E, the pixel data rate is slowed down by a factor of either two or four, respectively. This is due to the overhead time in the digital pixel data processing chain. As a result, the pixel clock speed is also reduced accordingly.

Figure 33. Readout of 8 Pixels in Normal and Column Bin Output Mode

# Interlaced Readout

The MT9V024 has two interlaced readout options. By setting R0x07[2:0] = 1, all the even-numbered rows are read out first, followed by a number of programmable field blanking rows (set by R0xBF[7:0]), then the odd-numbered rows, and finally the vertical blanking rows. By setting R0x07[2:0] = 2 only one field row is read out.

Consequently, the number of rows read out is half what is set in the window height register. The row start register determines which field gets read out; if the row start register is even, then the even field is read out; if row start address is odd, then the odd field is read out.

Figure 34. Spatial Illustration of Interlaced Image Readout

When interlaced mode is enabled, the total number of blanking rows are determined by both field blanking register

(R0xBF) and vertical blanking register (R0x06). The followings are their equations.

| Field Blanking | y = R0xBF[7:0]  (eq. 2) | 22) |

|----------------|-------------------------|-----|

|                |                         |     |

Vertical Blanking = R0x06[8:0] - R0xBF[7:0] (contextA) or R0xCE[8:0] - R0xBF[7:0] (contextB) (eq. 23) with

| minimum vertical blanking requirement = 4(absolute minimum operate; see Vertical Blanking Registers |  |

|-----------------------------------------------------------------------------------------------------|--|

| description for VBlank minimums for valid image output)                                             |  |

Similar to progressive scan, FV is logic LOW during the valid image row only. Binning should not be used in conjunction with interlaced mode.

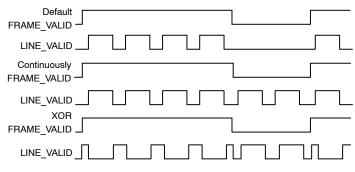

rows and two vertical blanking rows are shown in Figure 35. In the last format, the LV signal is the XOR between the continuous LV signal and the FV signal.

(eq. 24)

# LINE\_VALID

By setting bit 2 and 3 of R0x72, the LV signal can get three different output formats. The formats for reading out four

Figure 35. Different LINE\_VALID Formats

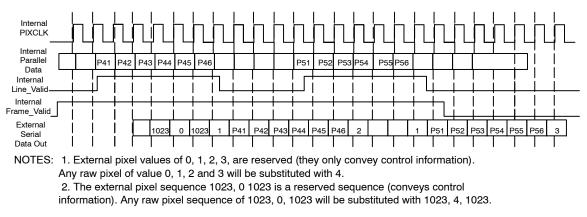

# LVDS Serial (Stand-Alone/Stereo) Output

The LVDS interface allows for the streaming of sensor data serially to a standard off-the-shelf deserializer up to eight meters away from the sensor. The pixels (and controls) are packeted-12-bit packets for stand-alone mode and 18-bit packets for stereoscopy mode. All serial signaling (CLK and data) is LVDS. The LVDS serial output could either be data from a single sensor (stand-alone) or stream-merged data from two sensors (self and its stereoscopic slave pair). The appendices describe in detail the topologies for both stand-alone and stereoscopic modes.

There are two standard deserializers that can be used. One for a stand-alone sensor stream and the other from a stereoscopic stream. The deserializer attached to a standalone sensor is able to reproduce the standard parallel output (8-bit pixel data, LV, FV, and PIXCLK). The deserializer attached to a stereoscopic sensor is able to reproduce 8- bit pixel data from each sensor (with embedded LV and FV ) and pixel-clk. An additional (simple) piece of logic is required to extract LV and FV from the 8-bit pixel data. Irrespective of the mode (stereoscopy/stand-alone), LV and FV are always embedded in the pixel data.

In stereoscopic mode, the two sensors run in lock-step, implying all state machines are in the same state at any given time. This is ensured by the sensor-pair getting their sys-clks and sys-resets in the same instance. Configuration writes through the two-wire serial interface are done in such a way that both sensors can get their configuration updates at once. The inter-sensor serial link is designed in such a way that once the slave PLL locks and the data-dly, shft-clk-dly and stream-latency-sel are configured, the master sensor streams valid stereo content irrespective of any variation voltage and/or temperature as long as it is within specification. The configuration values of data-dly, and stream-latency-sel shft-clk-dly are either predetermined from the board-layout or can be empirically determined by reading back the stereo-error flag. This flag is asserted when the two sensor streams are not in sync when merged. The combo reg is used for out-of-sync diagnosis.

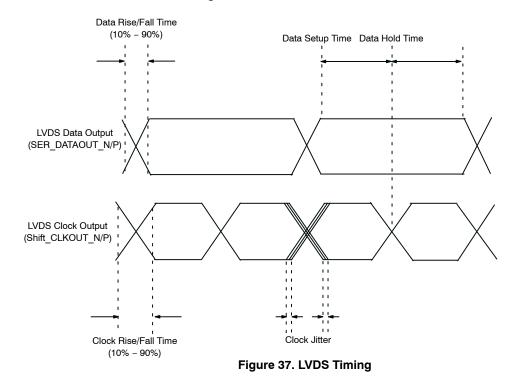

Figure 36. Serial Output Format for 6x2 Frame

# **LVDS Output Format**

In stand-alone mode, the packet size is 12 bits (2 frame bits and 10 payload bits); 10-bit pixels or 8-bit pixels can be selected. In 8-bit pixel mode (R0xB6[0] = 0), the packet

consists of a start bit, 8-bit pixel data (with sync codes), the line valid bit, the frame valid bit and the stop bit. For 10-bit pixel mode (R0xB6[0] = 1), the packet consists of a start bit, 10-bit pixel data, and the stop bit.

# Table 10. LVDS PACKET FORMAT IN STAND-ALONE MODE (Stereoscopy Mode Bit De-Asserted)

| 12 Bit Packet | Use_10-bit_pixels Bit De-Asserted<br>(8-Bit Mode) | Use_10-bit_pixels Bit Asserted<br>(10-Bit Mode) |