# **DAC4813**

# QUAD 12-BIT DIGITAL-TO-ANALOG CONVERTER (12-bit port interface)

○ V<sub>REF OUT</sub>

V<sub>OUT 1</sub>

O VOUT 2

O V<sub>OUT 3</sub>

V<sub>OUT 4</sub>

₩-+-₩

ΛŴ

////-●

/₩-•-₩

-W

### FEATURES

- COMPLETE WITH REFERENCE AND OUTPUT AMPLIFIERS

- 12-BIT PORT INTERFACE

- ANALOG OUTPUT RANGE: ±10V

- MONOTONICITY GUARANTEED OVER TEMPERATURE

- INTEGRAL LINEARITY ERROR: ±1/2LSB max

- ±12V to ±15V SUPPLIES

10V

Reference

12-bit

Latches

DAC4813

DB0 LSB

DB11<sup>O</sup> MSB

12

• 28-PIN PLASTIC DIP PACKAGE

## DESCRIPTION

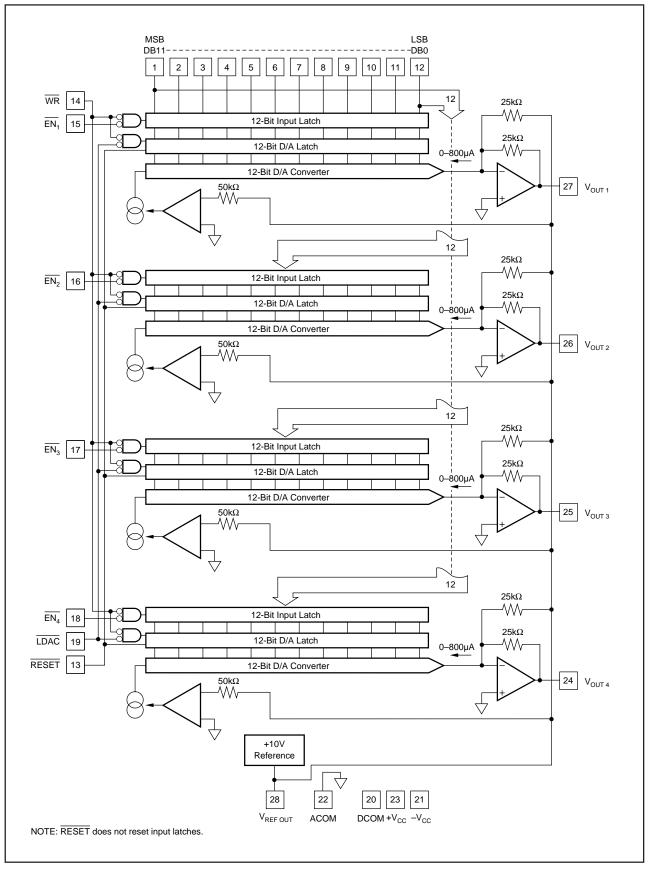

DAC4813 is a complete quad 12-bit digital-to-analog converter with bus interface logic. Each package includes a precision +10V voltage reference, doublebuffered bus interface including a RESET function and 12-bit D/A converters with voltage-output operational amplifiers.

The double-buffered interface consists of a 12-bit input latch and a D/A latch for each D/A converter. A RESET control allows the D/A outputs to be asynchronously reset to bipolar zero, a feature useful for power-up reset, system initialization and recalibration.

DAC4813 D/A converters are committed to the  $\pm 10V$  output range only. Gain and offset are not externally adjustable.

DAC4813 is available with a integral linearity error of 1/2LSB and 12-bit monotonicity guaranteed over temperature. It is packaged in a 28-pin 0.6in. wide plastic DIP package and specified over  $-40^{\circ}$ C to  $+85^{\circ}$ C and  $0^{\circ}$ C to  $+70^{\circ}$ C.

## **SPECIFICATIONS**

#### ELECTRICAL

$T_{A}$  = +25°C, +V\_{CC} = +12V or +15V, -V\_{CC} = -12V or -15V, unless otherwise noted.

|                                                   |                            |                | ]                     |                |                          |  |

|---------------------------------------------------|----------------------------|----------------|-----------------------|----------------|--------------------------|--|

| PARAMETER                                         | CONDITIONS                 | MIN            | ТҮР                   | MAX            | UNITS                    |  |

| INPUTS                                            |                            |                |                       |                |                          |  |

| DIGITAL INPUTS                                    | Over Temperature           |                |                       |                |                          |  |

| Input Code <sup>(1)</sup>                         | Range                      |                | Bipolar Offset Binary |                |                          |  |

| Logic Levels <sup>(2)</sup>                       |                            | . 0            |                       |                |                          |  |

| V <sub>IH</sub> <sup>(3)</sup><br>V <sub>II</sub> |                            | +2             |                       | +5.5<br>+0.8   | V                        |  |

| Logic Input Currents                              |                            | 0              |                       | +0.0           | v                        |  |

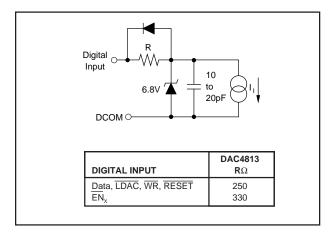

| DB0-DB11, WR, LDAC, RESET, EN <sub>x</sub>        |                            |                |                       |                |                          |  |

| III                                               | V <sub>1</sub> = +2.7V     |                |                       | ±40            | μΑ                       |  |

| IL                                                | V <sub>1</sub> = +0.4V     |                |                       | ±40            | μΑ                       |  |

| TRANSFER CHARACTERISTICS                          |                            |                |                       |                |                          |  |

| ACCURACY                                          |                            |                |                       |                |                          |  |

| Linearity Error                                   |                            |                | ±1/4                  | ±1/2           | LSB                      |  |

| Differential Linearity Error                      |                            |                | ±1/2                  | ±1             | LSB                      |  |

| Gain Error<br>Bipolar Zero Error <sup>(5)</sup>   |                            |                | ±0.05<br>±0.05        | ±0.2<br>±0.2   | %<br>%FSR <sup>(4)</sup> |  |

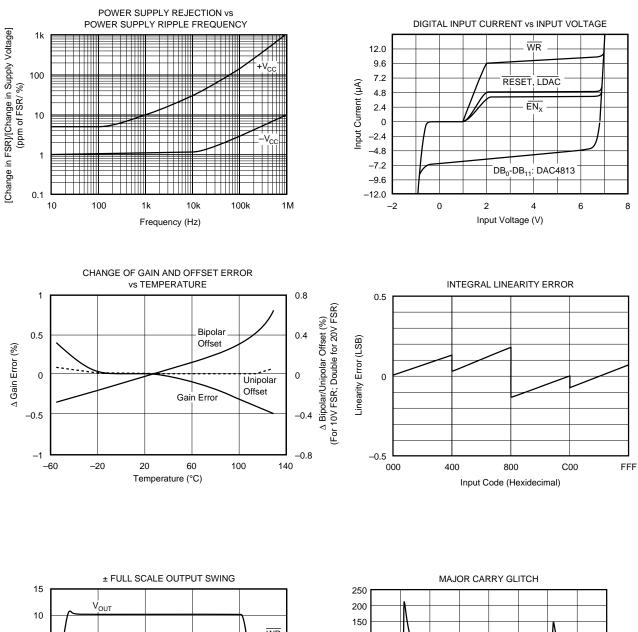

| Power Supply Sensitivity                          |                            |                | 10.00                 | <u>+0.2</u>    |                          |  |

| Of Full Scale +V <sub>CC</sub>                    |                            |                | ±5                    | ±20            | ppmFSR/%+V <sub>CC</sub> |  |

| -V <sub>cc</sub>                                  |                            |                | ±1                    | ±10            | ppmFSR/%-V <sub>CC</sub> |  |

| DRIFT                                             | Over Specification         |                |                       |                |                          |  |

| Caia                                              | Temperature Range          |                |                       | 100            | Pr = /00                 |  |

| Gain<br>Bipolar Zero Drift                        |                            |                | ±5<br>±5              | ±30<br>±15     | ppm/°C<br>ppmFSR/°C      |  |

| Linearity Error over Temperature                  |                            |                | ±1/2                  | ±15<br>±3/4    | LSB                      |  |

| Monotonicity                                      |                            |                | Guaranteed            | 20/1           | 200                      |  |

| DYNAMIC CHARACTERISTICS                           |                            |                |                       |                | •                        |  |

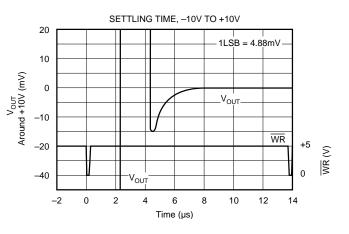

| SETTLING TIME (6)                                 | To within ±0.012%FSR       |                |                       |                |                          |  |

|                                                   | of Final Value             |                |                       |                |                          |  |

|                                                   | 5kΩ    500pF Load          |                |                       |                |                          |  |

| Full Scale Range Change                           | 20V Range                  | 0              | 4.5                   | 6              | μs                       |  |

| 1LSB Output Step (7) At Major Carry<br>Slew Rate  |                            | 2              | 10                    |                | μs<br>V/μs               |  |

| Crosstalk <sup>(8)</sup>                          | 5kΩ Loads                  |                | 0.2                   |                | LSB                      |  |

| OUTPUT                                            |                            |                |                       |                |                          |  |

| Output Voltage Range                              | $\pm V_{CC} \ge \pm 11.4V$ |                |                       | ±10            | V                        |  |

| Output Current                                    |                            | ±5             |                       |                | mA                       |  |

| Output Impedance                                  |                            |                | 0.2                   |                | Ω                        |  |

| Short Circuit to ACOM Duration                    | at DC                      |                | Indefinite            |                |                          |  |

|                                                   |                            | .0.05          | . 40.00               | . 40.05        | V                        |  |

| Voltage<br>Source Current Available               |                            | +9.95          | +10.00                | +10.05         | v                        |  |

| for External Loads                                |                            | 2              |                       |                | mA                       |  |

| Impedance                                         |                            |                | 0.2                   |                | Ω                        |  |

| Temperature Coefficient                           |                            |                | ±5                    | ±25            | ppm/°C                   |  |

| Short Circuit to Common Duration                  | at DC                      |                | Indefinite            |                |                          |  |

| POWER SUPPLY REQUIREMENTS                         |                            |                |                       | . 40 5         |                          |  |

| Voltage: +V <sub>CC</sub><br>-V <sub>CC</sub>     |                            | +11.4<br>–11.4 | +15<br>-15            | +16.5<br>-16.5 | V                        |  |

| Current:                                          | No Load                    | -11.4          | -15                   | -10.5          | v                        |  |

|                                                   | $\pm V_{CC} = \pm 15V$     |                |                       |                |                          |  |

| +V <sub>CC</sub>                                  |                            |                | 48                    | 60             | mA                       |  |

| -V <sub>CC</sub>                                  |                            |                | 24                    | 28             | mA                       |  |

| Power Dissipation<br>Potential at DCOM with       |                            |                | 1080                  | 1320           | mW                       |  |

| Respect to ACOM <sup>(9)</sup>                    |                            | -3             |                       | +3             | V                        |  |

| TEMPERATURE RANGES                                |                            | -              |                       | -              | +                        |  |

| Specification: AP                                 |                            | -40            |                       | +85            | °C                       |  |

| JP                                                |                            | 0              |                       | +70            | °C                       |  |

| Storage                                           |                            | -60            |                       | +100           | °C                       |  |

| Thermal Resistance, $\theta_{JA}$ , Plastic DIP   |                            |                |                       | 30             | °C/W                     |  |

NOTES: (1) For Two's Complement Input Coding invert the MSB with an external logic inverter. (2) Digital inputs are TTL and +5V CMOS compatible over the specification temperature range. (3) Open DATA input lines will be pulled above +5.5V. See discussion under LOGIC INPUT COMPATIBILITY in the OPERATION section. (4) FSR means Full Scale Range. For example, for  $\pm$ 10V output, FSR = 20V. (5) Error at input code 800<sub>HEX</sub>. (6) Maximum represents the 3 $\sigma$  limit. Not 100% tested for this parameter. (7) For the worst-case code change: 7FF<sub>HEX</sub> to 800<sub>HEX</sub> and 800<sub>HEX</sub> to 7FF<sub>HEX</sub>. (8) Crosstalk is defined as the change in any output as a result of any other output being driven from -10V to +10V at rated output current. (9) The maximum voltage at which ACOM and DCOM may be separated without affecting accuracy specifications.

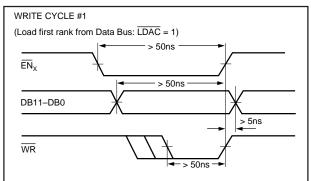

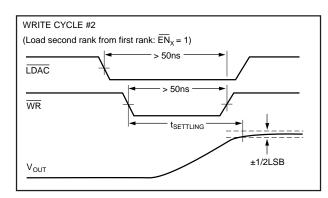

#### TIMING DIAGRAMS

#### **ABSOLUTE MAXIMUM RATINGS**

| +V <sub>CC</sub> to ACOM<br>-V <sub>CC</sub> to ACOM<br>+V <sub>CC</sub> to -V <sub>CC</sub> | 0 to –18V                |

|----------------------------------------------------------------------------------------------|--------------------------|

| ACOM to DCOM<br>Digital Inputs to DCOM<br>External Voltage applied to BPO Resistor           | $-1V$ to $+V_{CC}$       |

| V <sub>REF</sub> OUT                                                                         | Indefinite short to ACOM |

| Lead Temperature, soldering 10s<br>Max Junction Temperature                                  | +300°C                   |

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

### PACKAGE/ORDERING INFORMATION

| PRODUCT | PACKAGE                                                    | PACKAGE<br>DRAWING<br>NUMBER <sup>(1)</sup> | TEMPERATURE<br>RANGE           |

|---------|------------------------------------------------------------|---------------------------------------------|--------------------------------|

|         | 28-Pin Plastic DBL Wide DIP<br>28-Pin Plastic DBL Wide DIP |                                             | -40°C to +85°C<br>0°C to +70°C |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.

### ELECTROSTATIC DISCHARGE SENSITIVITY

Electrostatic discharge can cause damage ranging from performance degradation to complete device failure. Burr-Brown Corporation recommends that all integrated circuits be handled and stored using appropriate ESD protection methods.

#### **TRUTH TABLE**

| WR | EN1 | EN2 | EN3 | EN4 | LDAC | RESET | OPERATION                                  |

|----|-----|-----|-----|-----|------|-------|--------------------------------------------|

| Х  | Х   | Х   | Х   | Х   | Х    | 0     | Reset all D/A Latches                      |

| 1  | X   | Х   | Х   | Х   | Х    | 1     | No Operation                               |

| X  | 1   | 1   | 1   | 1   | 1    | 1     | No Operation                               |

| 0  | 1   | 1   | 1   | 0   | 1    | 1     | Load Data into First Rank for D/A 4        |

| 0  | 1   | 1   | 0   | 1   | 1    | 1     | Load Data into First Rank for D/A 3        |

| 0  | 1   | 0   | 1   | 1   | 1    | 1     | Load Data into First Rank for D/A 2        |

| 0  | 0   | 1   | 1   | 1   | 1    | 1     | Load Data into First Rank for D/A 1        |

| 0  | 1   | 1   | 1   | 1   | 0    | 1     | Load Second Rank from First Rank, All D/As |

| 0  | 0   | 0   | 0   | 0   | 0    | 1     | All Latches Transparent                    |

"X" = Don't Care

**DAC4813**

#### **PIN DESCRIPTIONS**

| 1 DB11 DATA, MSB, positive true.   2 DB10 DATA   3 DB9 DATA   4 DB8 DATA   5 DB7 DATA   6 DB6 DATA   7 DB5 DATA   8 DB4 DATA   9 DB3 DATA   11 DB1 DATA   12 DB0 DATA, LSB.   13 RESET Resets output of all D/As to bipolar-zero. The D/A remains in this state until overwritten by a LDAC-WR command. RE does not reset the input latch. After power-up and reset, input latches will be in an indeterminant state.   14 WR Resets output of all D/As to bipolar-zero. The D/A remains in this state until overwritten by a LDAC-WR command. RE does not reset the input latch. After power-up and reset, input latches will be in an indeterminant state.   14 WR Resets output of all D/As to bipolar-zero. The D/A remains in this state until overwritten by a LDAC-WR command. RE does not reset the input latch. After power-up and reset, input latches will be in an indeterminant state.   14 WR Enable for 12-bit input data latch of D/A1. NOTE: This logic path is slower than the WR/ path.   16 EN2 Enable for 12-bit input data latch of D/A2. NOTE: This logic path is slower                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 3 DB9 DATA   4 DB8 DATA   5 DB7 DATA   6 DB6 DATA   7 DB5 DATA   8 DB4 DATA   9 DB3 DATA   10 DB2 DATA   11 DB1 DATA   12 DB0 DATA, LSB.   13 RESET Resets output of all D/As to bipolar-zero. The D/A remains in this state until overwritten by a LDAC-WR command. RE   does not reset the input latch. After power-up and reset, input latches will be in an indeterminant state.   14 WR Write strobe. Must be low for data transfer to any latch (except RESET).   15 EN1 Enable for 12-bit input data latch of D/A1. NOTE: This logic path is slower than the WR/ path.   16 EN2 Enable for 12-bit input data latch of D/A2. NOTE: This logic path is slower than the WR/ path.   17 EN3 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR/ path.   18 EN4 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR/ path.   19 LDAC Load DAC enable. Must be low with WR for data transfer to the D/A latch and simul                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| 4 DB8 DATA   5 DB7 DATA   6 DB6 DATA   7 DB5 DATA   8 DB4 DATA   9 DB3 DATA   10 DB2 DATA   11 DB1 DATA   12 DB0 DATA, LSB.   13 RESET Resets output of all D/As to bipolar-zero. The D/A remains in this state until overwritten by a LDAC-WR command. RE   does not reset the input latch. After power-up and reset, input latches will be in an indeterminant state.   14 Write strobe. Must be low for data transfer to any latch (except RESET).   15 EN1 Enable for 12-bit input data latch of D/A1. NOTE: This logic path is slower than the WR/ path.   16 EN2 Enable for 12-bit input data latch of D/A3. NOTE: This logic path is slower than the WR / path.   17 EN3 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR / path.   18 EN4 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR / path.   19 LDAC Load DAC enable. Must be low with WR for data transfer to the D/A latch and simultaneous update of all D/A convertupating theadat transfer to the D/A latch and simultaneou                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

| 5 DB7 DATA   6 DB6 DATA   7 DB5 DATA   8 DB4 DATA   9 DB3 DATA   10 DB2 DATA   11 DB1 DATA   12 DB0 DATA, LSB.   13 RESET Resets output of all D/As to bipolar-zero. The D/A remains in this state until overwritten by a LDAC-WR command. RE   14 WR Write strobe. Must be low for data transfer to any latch (except RESET).   15 EN1 Enable for 12-bit input data latch of D/A1. NOTE: This logic path is slower than the WR/ path.   16 EN2 Enable for 12-bit input data latch of D/A3. NOTE: This logic path is slower than the WR / path.   17 EN3 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR / path.   18 EN4 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR / path.   18 EN4 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR / path.   19 LDAC Load DAC enable. Must be low with WR for data transfer to the D/A latch and simultaneous update of all D/A converture.   20 DCOM Digital com                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| 6 DB6 DATA   7 DB5 DATA   8 DB4 DATA   9 DB3 DATA   10 DB2 DATA   11 DB1 DATA   12 DB0 DATA, LSB.   13 RESET Resets output of all D/As to bipolar-zero. The D/A remains in this state until overwritten by a LDAC-WR command. RE does not reset the input latch. After power-up and reset, input latches will be in an indeterminant state.   14 WR Write strobe. Must be low for data transfer to any latch (except RESET).   15 EN1 Enable for 12-bit input data latch of D/A1. NOTE: This logic path is slower than the WR/ path.   16 EN2 Enable for 12-bit input data latch of D/A2. NOTE: This logic path is slower than the WR / path.   17 EN3 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR / path.   18 EN4 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR / path.   19 LDAC Load DAC enable. Must be low with WR for data transfer to the D/A latch and simultaneous update of all D/A converted DCOM   20 DCOM Digital common, logic currents return.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |

| 7 DB5 DATA   8 DB4 DATA   9 DB3 DATA   10 DB2 DATA   11 DB1 DATA   12 DB0 DATA, LSB.   13 RESET Resets output of all D/As to bipolar-zero. The D/A remains in this state until overwritten by a LDAC-WR command. RE does not reset the input latch. After power-up and reset, input latches will be in an indeterminant state.   14 WR Write strobe. Must be low for data transfer to any latch (except RESET).   15 EN1 Enable for 12-bit input data latch of D/A1. NOTE: This logic path is slower than the WR/ path.   16 EN2 Enable for 12-bit input data latch of D/A2. NOTE: This logic path is slower than the WR / path.   17 EN3 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR / path.   18 EN4 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR / path.   19 LDAC Load DAC enable. Must be low with WR for data transfer to the D/A latch and simultaneous update of all D/A converted DCOM   20 DCOM Digital common, logic currents return.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 8 DB4 DATA   9 DB3 DATA   10 DB2 DATA   11 DB1 DATA   12 DB0 DATA, LSB.   13 RESET Resets output of all D/As to bipolar-zero. The D/A remains in this state until overwritten by a LDAC-WR command. RE   14 WR Write strobe. Must be low for data transfer to any latch (except RESET).   15 EN1 Enable for 12-bit input data latch of D/A1. NOTE: This logic path is slower than the WR/ path.   16 EN2 Enable for 12-bit input data latch of D/A2. NOTE: This logic path is slower than the WR/ path.   17 EN3 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR / path.   18 EN4 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR / path.   18 EnAble for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR / path.   19 LDAC Load DAC enable. Must be low with WR for data transfer to the D/A latch and simultaneous update of all D/A converted DCOM   20 DCOM Digital common, logic currents return.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 9 DB3 DATA   10 DB2 DATA   11 DB1 DATA   12 DB0 DATA, LSB.   13 RESET Resets output of all D/As to bipolar-zero. The D/A remains in this state until overwritten by a LDAC-WR command. Rt   14 WR Write strobe. Must be low for data transfer to any latch (except RESET).   15 EN1 Enable for 12-bit input data latch of D/A1. NOTE: This logic path is slower than the WR/ path.   16 EN2 Enable for 12-bit input data latch of D/A2. NOTE: This logic path is slower than the WR/ path.   17 EN3 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR / path.   18 EN4 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR / path.   19 LDAC Load DAC enable. Must be low with WR for data transfer to the D/A latch and simultaneous update of all D/A converted DCOM   20 DCOM Digital common, logic currents return.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| 10 DB2 DATA   11 DB1 DATA   12 DB0 DATA, LSB.   13 RESET Resets output of all D/As to bipolar-zero. The D/A remains in this state until overwritten by a LDAC-WR command. RE does not reset the input latch. After power-up and reset, input latches will be in an indeterminant state.   14 WR Write strobe. Must be low for data transfer to any latch (except RESET).   15 EN1 Enable for 12-bit input data latch of D/A1. NOTE: This logic path is slower than the WR/ path.   16 EN2 Enable for 12-bit input data latch of D/A3. NOTE: This logic path is slower than the WR/ path.   17 EN3 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR / path.   18 EN4 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR / path.   19 LDAC Load DAC enable. Must be low with WR for data transfer to the D/A latch and simultaneous update of all D/A converted DCOM   20 DCOM Digital common, logic currents return.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

| 11 DB1 DATA   12 DB0 DATA, LSB.   13 RESET Resets output of all D/As to bipolar-zero. The D/A remains in this state until overwritten by a LDAC-WR command. RE does not reset the input latch. After power-up and reset, input latches will be in an indeterminant state.   14 WR Write strobe. Must be low for data transfer to any latch (except RESET).   15 EN1 Enable for 12-bit input data latch of D/A1. NOTE: This logic path is slower than the WR/ path.   16 EN2 Enable for 12-bit input data latch of D/A3. NOTE: This logic path is slower than the WR/ path.   17 EN3 Enable for 12-bit input data latch of D/A3. NOTE: This logic path is slower than the WR/ path.   18 EN4 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR/ path.   19 LDAC Load DAC enable. Must be low with WR for data transfer to the D/A latch and simultaneous update of all D/A converter 20   20 DCOM Digital common, logic currents return.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

| 12 DB0 DATA, LSB.   13 RESET Resets output of all D/As to bipolar-zero. The D/A remains in this state until overwritten by a LDAC-WR command. Red does not reset the input latch. After power-up and reset, input latches will be in an indeterminant state.   14 WR Write strobe. Must be low for data transfer to any latch (except RESET).   15 EN1 Enable for 12-bit input data latch of D/A1. NOTE: This logic path is slower than the WR/ path.   16 EN2 Enable for 12-bit input data latch of D/A3. NOTE: This logic path is slower than the WR / path.   17 EN3 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR / path.   18 EN4 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR / path.   19 LDAC Load DAC enable. Must be low with WR for data transfer to the D/A latch and simultaneous update of all D/A converted DCOM   20 DCOM Digital common, logic currents return.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| 13 RESET Resets output of all D/As to bipolar-zero. The D/A remains in this state until overwritten by a LDAC-WR command. RE does not reset the input latch. After power-up and reset, input latches will be in an indeterminant state.   14 WR Write strobe. Must be low for data transfer to any latch (except RESET).   15 EN1 Enable for 12-bit input data latch of D/A1. NOTE: This logic path is slower than the WR/ path.   16 EN2 Enable for 12-bit input data latch of D/A2. NOTE: This logic path is slower than the WR/ path.   17 EN3 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR /path.   18 EN4 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR /path.   18 EN4 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR /path.   19 LDAC Load DAC enable. Must be low with WR for data transfer to the D/A latch and simultaneous update of all D/A converted Digital common, logic currents return.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |

| 14 WR does not reset the input latch. After power-up and reset, input latches will be in an indeterminant state.   14 WR Write strobe. Must be low for data transfer to any latch (except RESET).   15 EN1 Enable for 12-bit input data latch of D/A1. NOTE: This logic path is slower than the WR/ path.   16 EN2 Enable for 12-bit input data latch of D/A2. NOTE: This logic path is slower than the WR/ path.   17 EN3 Enable for 12-bit input data latch of D/A3. NOTE: This logic path is slower than the WR / path.   18 EN4 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR / path.   19 LDAC Load DAC enable. Must be low with WR for data transfer to the D/A latch and simultaneous update of all D/A converter   20 DCOM Digital common, logic currents return.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 14 WR Write strobe. Must be low for data transfer to any latch (except RESET).   15 EN1 Enable for 12-bit input data latch of D/A1. NOTE: This logic path is slower than the WR/ path.   16 EN2 Enable for 12-bit input data latch of D/A2. NOTE: This logic path is slower than the WR/ path.   17 EN3 Enable for 12-bit input data latch of D/A3. NOTE: This logic path is slower than the WR / path.   18 EN4 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR / path.   18 EN4 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR / path.   19 LDAC Load DAC enable. Must be low with WR for data transfer to the D/A latch and simultaneous update of all D/A converted Digital common, logic currents return.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RESET  |

| 15 EN1 Enable for 12-bit input data latch of D/A1. NOTE: This logic path is slower than the WR/ path.   16 EN2 Enable for 12-bit input data latch of D/A2. NOTE: This logic path is slower than the WR/ path.   17 EN3 Enable for 12-bit input data latch of D/A3. NOTE: This logic path is slower than the WR/ path.   18 EN4 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR/ path.   19 LDAC Load DAC enable. Must be low with WR for data transfer to the D/A latch and simultaneous update of all D/A converted Digital common, logic currents return.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 16 EN2 Enable for 12-bit input data latch of D/A2. NOTE: This logic path is slower than the WR/ path.   17 EN3 Enable for 12-bit input data latch of D/A3. NOTE: This logic path is slower than the WR/ path.   18 EN4 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR/ path.   19 LDAC Load DAC enable. Must be low with WR for data transfer to the D/A latch and simultaneous update of all D/A converted to D/A4. DCM   20 DCOM Digital common, logic currents return.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |

| 17 EN3 Enable for 12-bit input data latch of D/A3. NOTE: This logic path is slower than the WR /path.   18 EN4 Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR/ path.   19 LDAC Load DAC enable. Must be low with WR for data transfer to the D/A latch and simultaneous update of all D/A converted to D/A big transfer to the D/A latch and simultaneous update of all D/A converted to D/A big transfer to the D/A latch and simultaneous update of all D/A converted to D/A big transfer to the D/A latch and simultaneous update of all D/A converted to D/A big transfer to the D/A latch and simultaneous update of all D/A converted to D/A big transfer to the D/A latch and simultaneous update of all D/A converted to D/A big transfer to the D/A latch and simultaneous update of all D/A converted to D/A big transfer to the D/A latch and simultaneous update of all D/A converted to D/A big transfer to the D/A latch and simultaneous update of all D/A converted to D/A big transfer to the D/A latch and simultaneous update of all D/A converted to D/A big transfer to the D/A latch and simultaneous update of all D/A converted to D/A big transfer to the D/A latch and simultaneous update of all D/A converted to D/A big transfer to the                                                                       |        |

| 18   EN4   Enable for 12-bit input data latch of D/A4. NOTE: This logic path is slower than the WR/ path.     19   LDAC   Load DAC enable. Must be low with WR for data transfer to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to the D/A latch and simultaneous update of all D/A converted provide to t |        |

| 19   LDAC   Load DAC enable. Must be low with WR for data transfer to the D/A latch and simultaneous update of all D/A converted 20     20   DCOM   Digital common, logic currents return.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |

| 20 DCOM Digital common, logic currents return.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | rters. |

| 21 –V Analog supply input nominally –12V or –15V referred to ACOM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

| 22 ACOM Analog common, +V <sub>cc</sub> , -V <sub>cc</sub> supply return.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |

| 23 +V <sub>cc</sub> Analog supply input, nominally +12V or +15V referred to ACOM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| 24 V <sub>out 4</sub> D/A 4 analog output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |

| $25 V_{0/T,3}$ D/A 3 analog output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 26 V <sub>OUT 2</sub> D/A 2 analog output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |

| 27 V <sub>out 1</sub> D/A 1 analog output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |

| 28 V <sub>REF OUT</sub> +10V reference output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

#### **BLOCK DIAGRAM**

DAC4813

## **TYPICAL PERFORMANCE CURVES**

$T_{_A}$  = +25°C,  $V_{_{CC}}$  =  $\pm 15V$  unless otherwise noted.

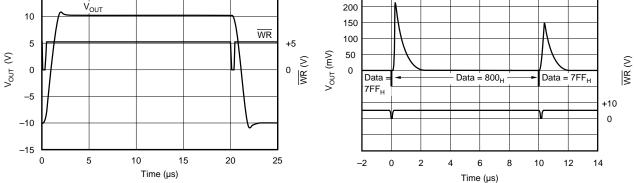

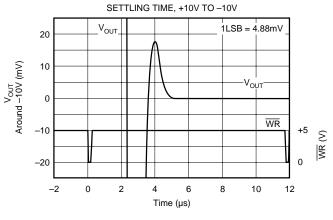

## **TYPICAL PERFORMANCE CURVES (CONT)**

$T_{_{\rm A}}$  = +25°C,  $V_{_{\rm CC}}$  = ±15V unless otherwise noted.

## DISCUSSION OF SPECIFICATIONS

### LINEARITY ERROR

Linearity error is defined as the deviation of the analog output from a straight line drawn between the end points (digital inputs all "1s" and all "0s"). DAC4813 linearity error is  $\pm 1/2$ LSB max at  $\pm 25^{\circ}$ C.

#### DIFFERENTIAL LINEARITY ERROR

Differential Linearity Error (DLE) is the deviation from a 1LSB output change from one adjacent state to the next. A DLE specification of 1/2LSB means that the output step size can range from 1/2LSB to 3/2LSB when the digital input code changes from one code word to the adjacent code word If the DLE is more positive than -1LSB, the D/A is said to be monotonic.

#### MONOTONICITY

A D/A converter is monotonic if the output either increases or remains the same for increasing digital input values. DAC4813 is monotonic over their specification temperature range  $-40^{\circ}$ C to  $+85^{\circ}$ C.

#### DRIFT

*Gain Drift* is a measure of the change in the Full Scale Range (FSR) output over the specification temperature range. Gain Drift is expressed in parts per million per degree Celsius (ppm/°C).

*Bipolar Zero Drift* is measured with a data input of  $800_{HEX}$ . The D/A is configured for bipolar output. Bipolar Zero Drift is expressed in parts per million of Full Scale Range per degree Celsius (ppm of FSR/°C).

### SETTLING TIME

Settling Time is the total time (including slew time) for the output to settle to within an error band around its final value after a change in input. Settling times are specified to  $\pm 0.01\%$  of Full Scale Range (FSR) for two conditions: one for a FSR output change of 20V (25k $\Omega$  feedback) and one for a 1LSB change. The 1LSB change is measured at the Major Carry (7FF<sub>HEX</sub> to 800<sub>HEX</sub>, and 800<sub>HEX</sub> to 7FF<sub>HEX</sub>), the input code transition at which worst-case settling time occurs.

### OPERATION

### INTERFACE LOGIC

The bus interface logic of the DAC4813 consists of two independently addressable latches in two ranks for each D/A converter. The first rank consists of one 12-bit input latch which can be loaded directly from a 12- or 16-bit microprocessor/microcontroller bus. The input latch holds data temporarily before it is loaded into the second latch, the D/A latch. This double buffered organization permits simultaneous update of all D/As.

All latches are level-triggered. Data present when the control signals are logic "0" will enter the latch. When the control signals return to logic "1", the data is latched.

**CAUTION:** DAC4813 was designed to use  $\overline{WR}$  as the fast strobe.  $\overline{WR}$  has a much faster logic path than  $\overline{EN}_x$  (or  $\overline{LDAC}$ ). Therefore, if one permanently wires  $\overline{WR}$  to DCOM and uses only  $\overline{EN}_x$  to strobe data into the latches, the DATA HOLD time will be long, approximately 20ns to 30ns, and this time will vary considerably in this range from unit to unit. DATA HOLD time using  $\overline{WR}$  is 5ns max.

#### **RESET FUNCTION**

The Reset function resets only the D/A latch. Therefore, after a RESET, good data must be written to **all** the input latches before an  $\overline{\text{LDAC}} - \overline{\text{WR}}$  command is issued. Otherwise, old data or unknown data is present in the input latches and will be transferred to the D/A latch producing an analog output value that may be unwanted.

#### LOGIC INPUT COMPATIBILITY