# 带有一个锁相环的通用闪存可编程时钟 发生器

### 特性

- ■集成锁相环 (PLL)

- ■商业级和工业级操作

- 闪存可编程

- 现场可编程

- 低时滞、低抖动、高精度输出

- 当输出电压为 2.5 V 时, 工作电压将为 3.3 V

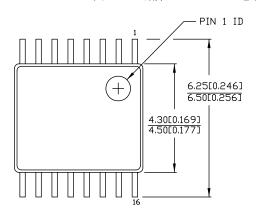

- 16 引脚 TSSOP 封装 (CY22050)

- 具有 NiPdAu 引线焊点的 16 引脚 TSSOP 封装 (CY220501)

- 输入频率范围:

- □ 8 MHz 至 30 MHz (外部晶振)

- □ 1 MHz 至 133 MHz (驱动时钟)

- 输出频率范围:

- □商业级温度

- 8 kHz 至 200 MHz (3.3 V)

- 8 kHz 至 166.6 MHz (2.5 V)

- □工业级温度

- 8 kHz 至 166.6 MHz (3.3 V)

- 8 kHz 至 150 MHz (2.5 V)

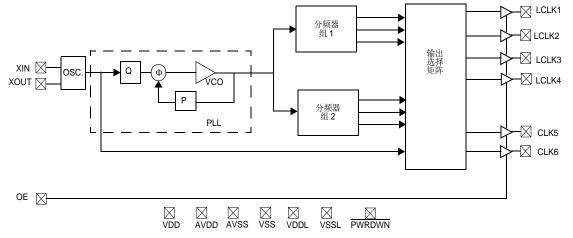

### 功能说明

CY22050 是一款可编程时钟发生器,适用于网络、电信、数据通信和其他通用应用。在 16 引脚 TSSOP 封装中, CY22050 提供了多达六个可配置输出,使用了 3.3 V 的电源。片上参考振荡器使用的是 8~30 MHz 晶体或 1~133 MHz 的外部时钟信号。

CY22050 具有一个 PLL,用于驱动六个可编程输出时钟。输出时钟是由 PLL 或参考频率 (REF)派生出的。输出后分频器可提供给这两项使用。可以将四个输出设置为 3.3 V 或 2.5 V,从而能够用于各种便携式和低功耗应用。

CY220501 是带有 NiPdAu 引线焊点的 CY22050。

### 逻辑框图

### 目录

| 引脚配置              | 3 |

|-------------------|---|

| 引脚定义              | 3 |

| 编程说明              |   |

| 对 CY22050F 进行现场编程 | 4 |

| CyberClocks™ 软件   | 4 |

| CY3672 开发套件       | 4 |

| 应用                |   |

| 控制抖动              | 4 |

| CY22050 频率校准      |   |

| 时钟输出设置:交叉点开关矩阵    | 5 |

| 参考晶体输入            |   |

| 晶体的驱动电平和功耗        |   |

| 最大绝对值条件           |   |

| 建议工作条件            | 7 |

| 建议的晶体规格           |   |

| 直流电气特性            |   |

|                   | 8 |

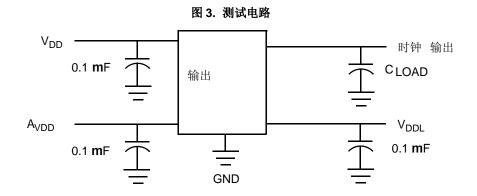

| 测试电路                   | 9 |

|------------------------|---|

| 开关波形                   |   |

| 订购信息                   |   |

| 各种配置                   |   |

| 订购代码定义                 |   |

| 16 引脚 TSSOP 封装特性       |   |

| 封装图和尺寸                 |   |

| 缩略语                    |   |

| 文档规范                   |   |

| 测量单位                   |   |

| 文档修订记录                 |   |

| 销售、解决方案和法律信息           |   |

| 全球销售和设计支持              |   |

| 产品                     |   |

| PSoC <sup>®</sup> 解决方案 |   |

| 赛普拉斯开发者社区              |   |

| サ <del>ナ</del> キ柱      |   |

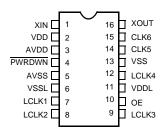

### 引脚配置

图 1. 16 引脚 TSSOP 的引脚分布

### 引脚定义

| TATION            |      |                                                                                       |  |  |

|-------------------|------|---------------------------------------------------------------------------------------|--|--|

| 名称                | 引脚编号 | 说明                                                                                    |  |  |

| XIN               | 1    | 参考输入。由晶体(8 MHz-30 MHz)或外部时钟(1 MHz-133 MHz)驱动。根据制造商、流程、性能或品质选择晶体时,可编程输入负载电容能够提供最大的灵活性。 |  |  |

| VDD               | 12   | 3.3 V 的供电电压                                                                           |  |  |

| AVDD              | 3    | 3.3 V 的模拟供电电压                                                                         |  |  |

| PWRDWN [1]        | 4    | 断电。当引脚 4 为低电平时, CY22050 将进入关闭模式。                                                      |  |  |

| AVSS              | 5    | 模拟接地                                                                                  |  |  |

| VSSL              | 6    | LCLK 接地                                                                               |  |  |

| LCLK1             | 7    | V <sub>DDL</sub> 电平 (3.3 V 或 2.5 V) 下的可配置时钟输出 1                                       |  |  |

| LCLK2             | 8    | V <sub>DDL</sub> 电平 (3.3 V 或 2.5 V) 下的可配置时钟输出 2                                       |  |  |

| LCLK3             | 9    | V <sub>DDL</sub> 电平 (3.3 V 或 2.5 V) 下的可配置时钟输出 3                                       |  |  |

| OE <sup>[1]</sup> | 10   | 输出使能。当引脚 10 为低电平时,所有输出为三态。                                                            |  |  |

| VDDL              | 11   | LCLK 供电电压 (2.5 V 或 3.3 V)                                                             |  |  |

| LCLK4             | 12   | V <sub>DDL</sub> 电平 (3.3 V 或 2.5 V) 下的可配置时钟输出 4                                       |  |  |

| VSS               | 13   | 接地                                                                                    |  |  |

| CLK5              | 14   | 可配置时钟输出 5 (3.3 V)                                                                     |  |  |

| CLK6              | 15   | 可配置时钟输出 6 (3.3 V)                                                                     |  |  |

| XOUT [2]          | 16   | 参考输出                                                                                  |  |  |

#### 注释:

- 1. CY22050 没有内部上拉或下拉电阻。必须正确驱动 PWRDWN 和 OE 引脚或将这些引脚连接到电源上或接地。 2. 如果 XIN 由外部时钟源驱动,请将 XOUT 置于悬空状态。

#### 编程说明

#### 对 CY22050F 进行现场编程

CY22050 被编程为封装级别,即为安装到 PCB 上之前位于编程器套接字内。CY22050 是以闪存技术为基础的,因此可以对这些器件进行多达一百次的编程。这样可以快速、轻松地进行设计更改和产品更新,从而可以避免有关陈旧和库存过期等问题。

可以在 CY3672 编程器上进行编程样本和少数原型。赛普拉斯增值分销合作伙伴和 BP Microsystems、HiLo Systems 以及其他团队中第三方编程系统可进行大批量生产。

#### CyberClocks™ 软件

CyberClocks 是一款易用的软件应用,用户通过它可以对CY22050 进行自定义配置。在 CyberClocks 中,选择CyClocksRT™工具。用户可以指定 REF、PLL 频率、输出频率和/或后分频器,以及不同的功能选项。 CyClocksRT 输出一个符合工业标准的 JEDEC 文件,用于编程 CY22050。

CyClocksRT 可以从 http://www.cypress.com 赛普拉斯网站上免费下载。在某个运行 Windows 操作系统的 PC 上安装并运行它。

#### CY3672 开发套件

赛普拉斯 CY3672 开发套件与 CY22050 结合使用是优选方法,它适用于编程样本和少数原型。该套件包含了最新版本的 CyClocksRT 和一个小型便携式编程器,该编程器连接着 PC,用以随时编程自定义频率。

可以将 CyClocksRT 的 JEDEC 文件输出下载到便携式编程器上,以进行小批量编程,或一起使用该文件输出和生产编程系统来进行更大的批量编程。

### 应用

#### 控制抖动

可以通过多种方式定义抖动。相位噪声、长期抖动、周期间抖动、周期抖动、绝对抖动和确定抖动。这些抖动术语通常在 rms、峰至峰等术语中出现,或在与基频相关的相位噪声 dBC/Hz 情况下出现。实际抖动取决于 XIN 抖动及沿速率、有效输出数量、输出频率、  $V_{DDI}$  (2.5 V 或 3.3 V)、温度以及输出负载。

电源噪声和时钟输出负载是时钟抖动的两个主要系统来源。通过对时钟进行合适的电源去耦(通过一个 0.1 mF 陶瓷电容),可以减轻电源噪声并确保地面和芯片间较低的阻抗。将电容时钟输出负载降低到最小值可降低时钟沿上的电流尖刺,从而减少抖动。

降低有效输出总量也能同时线性降低抖动。但与使用一个输出来 驱动两个负载相比,应该选择使用两个输出执行该操作。

PLL 纠正 VCO 频率的速率和幅度直接与抖动性能相关。如果该速率过慢,那么长期抖动和相位噪声非常小。因此,要想改善长期抖动和相位噪声,需要将Q设置为最小值。该技术会递增相位频率检测器的速率(该检测器依次驱动 VCO 的输入电压)。同样,递增P,直到 VCO 达到它的最大额定速率也能降低长期抖动和相位噪声。例如:输入参考为12 MHz;所需要的输出频率为33.3 MHz。可以采用以下解决方案:设置Q=3、P=25、Post Div=3。但最好的抖动结果为。Q=2、P=50、Post Div=9。

欲了解更多有关信息,请参考 http://www.cypress.com 网站上提供的应用笔记 "基于 PLL 系统中的抖动:原因、影响和解决方案" (点击 "Application Notes" (应用笔记))或联系您当地的赛普拉斯现场应用工程师。

### CY22050 频率校准

CY22050 是一个非常灵活的时钟发生器,它带有从 PLL 生成的 六个单独输出。

通过下面四个变量可以确定最后的输出频率: 输入 REF、P 和 Q 分频器以及后分频器。用于确定基于 CY22150 设计的最后输出 频率的三个基本公式分别为:

- CLK = ((REF \* P)/Q)/ 后分频器

- CLK = REF/ 后分频器

#### ■ CLK = REF

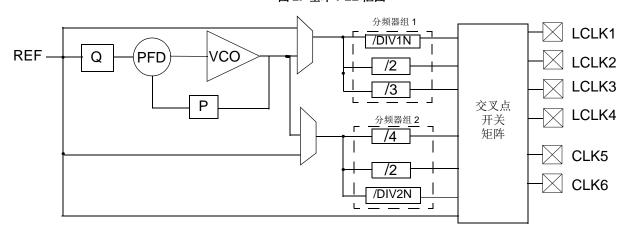

图 2 中显示的是基本 PLL 框图。每个时钟输出共有七个可用的输出选项。有六个后分频器选项,分别为:/2(两个)、/3、/4、/DIV1N 和 DIV2N。DIV1N 和 DIV2N 被单独计算并相互独立。可以将后分频器选项应用于已计算的 PLL 频率或直接应用于 REF。除了六个后分频器选项外,第七个选项会旁路 PLL 并将 REF 直接传送给交叉点开关矩阵。

#### 图 2. 基本 PLL 框图

### 时钟输出设置:交叉点开关矩阵

每个时钟输出都来自七个独立频率源中的某一个。交叉点开关矩阵定义了连接到每个独立时钟输出的频率源。虽然看起来分频器 选项数量是无限的,但选择分频器选项时,必须遵循某些规则。

#### 表 1. 时钟输出定义

| 时钟输出分频器 | 定义和注释                                                                              |

|---------|------------------------------------------------------------------------------------|

| 无       | 时钟输出源是参考输入频率。                                                                      |

| /DIV1N  | 时钟输出使用了从分频器组 1 生成的 /DIV1N 选项。 DIV1N 的可选择值为 4 ~ 130。如果未使用分频器组 1, 那么 DIV1N 被设置为 8。   |

| /2      | 时钟输出使用了分频器组 1 中的固定 /2 选项。如果使用该选项, DIV1N 必须能被 4 整除。                                 |

| /3      | 时钟输出使用了分频器组 1 中的固定 /3 选项。如果使用该选项,则 DIV1N 被设置为 6。                                   |

| /DIV2N  | 时钟输出使用了从分频器组 2 生成的 /DIV2N 选项。DIV2N 的可选值范围为 4 ~ 130。如果未使用分频器组 2, 那么应该将 DIV2N 设置为 8。 |

| /2      | 时钟输出使用了分频器组 2 中的固定 /2 选项。如果使用该选项,则 DIV2N 必须能被 4 整除。                                |

| /4      | 时钟输出 2 使用了分频器组 2 中的固定 /4 选项。如果使用该选项, DIV2N 必须能被 8 整除。                              |

### 参考晶体输入

CY22050的输入晶体振荡器是一项重要的性能,它为用户选择晶体作为参考时钟源提供了灵活性。该振荡器反相器拥有可编程增益,能够根据制造商、流程、性能和品质与参考晶体相兼容。

输入负载电容的大小由某个可编程寄存器中的八位值确定。通过 以下公式可以确定总负载电容:

$CapLoad = (C_L - C_{BRD} - C_{CHIP})/0.09375 pF$

在 CyClocksRT 中,输入晶体电容(C<sub>L</sub>)。CapLoad 的值被自动确认,并被编程到 CY22050 内。

如果您需要更好地控制 CapLoad 的值,请使用 CY22150 来控制 串行配置和输入负载电容。对于外部时钟源,该默认值为 0。

为了降低外部组件成本,在 CY22050 芯片上放置了一个输入负载电容。这些电容是真正的平行板电容器,它们能够降低非线性负载电容与负载、偏压、电源和温度变化时可能发生的频率移位。

#### 晶体的驱动电平和功耗

指定了晶体,用以接收最大的驱动电平。通常,晶体越大,可以接受的电源也越大。下表中的驱动电平规范提供了 CY22050 中振荡器电路可驱动电源的一般上限。

对于一个电压摆幅而言,晶体的功耗与 ESR 和晶体频率的平方成正比。(请注意,有时候实际的 ESR 比晶体制造商所指定的值低很多。)功耗也基本与  $C_L$  的平方成正比。

通过使用具有低  $C_L$  和低  $R_1$  (ESR) 的频率被降低的晶体,可使功耗下降到低于表中的 DL 规格。

### 最大绝对值条件

| 参数             | 说明                               | 最小值             | 最大值                   | 单位 |

|----------------|----------------------------------|-----------------|-----------------------|----|

| $V_{DD}$       | 供电电压                             | -0.5            | 7.0                   | V  |

| $V_{DDL}$      | I/O 供电电压                         | -0.5            | 7.0                   | V  |

| T <sub>S</sub> | 存放温度 [3]                         | <del>-</del> 65 | 125                   | °C |

| T <sub>J</sub> | 结温                               | _               | 125                   | °C |

|                | 封装功耗 — 商业级温度                     | _               | 450                   | mW |

|                | 封装功耗 — 工业级温度                     | -               | 380                   | mW |

|                | 数字输入                             | $AV_{SS} - 0.3$ | $AV_{DD} + 0.3$       | V  |

|                | 参照 V <sub>DD</sub> 的数字输出         | $V_{SS} - 0.3$  | $V_{DD} + 0.3$        | V  |

|                | 参照 V <sub>DDL</sub> 的数字输出        | $V_{SS} - 0.3$  | V <sub>DDL</sub> +0.3 | V  |

| ESD            | 静电放电电压 (根据 MIL-STD-833, 方法 3015) | -               | 2000                  | V  |

#### 注释:

3. 在 10 年中测量

## 建议工作条件

| 参数                 | 说明                                               | 最小值   | 典型值 | 最大值   | 单位  |

|--------------------|--------------------------------------------------|-------|-----|-------|-----|

| $V_{DD}$           | 工作电压                                             | 3.135 | 3.3 | 3.465 | V   |

| VDDL <sub>HI</sub> | 工作电压                                             | 3.135 | 3.3 | 3.465 | V   |

| VDDL <sub>LO</sub> | 工作电压                                             | 2.375 | 2.5 | 2.625 | V   |

| T <sub>AC</sub>    | 商业级环境温度                                          | 0     | _   | 70    | °C  |

| T <sub>AI</sub>    | 工业级环境温度                                          | -40   | _   | 85    | °C  |

| C <sub>LOAD</sub>  | 最大负载电容 V <sub>DD</sub> /V <sub>DDL</sub> = 3.3 V | _     | _   | 15    | pF  |

| C <sub>LOAD</sub>  | 最大负载电容 V <sub>DDL</sub> = 2.5 V                  | _     | _   | 15    | pF  |

| f <sub>REFD</sub>  | 驱动 REF                                           | 1     | _   | 133   | MHz |

| f <sub>REFC</sub>  | 晶体 REF                                           | 8     | _   | 30    | MHz |

| t <sub>PU</sub>    | 所有 V <sub>DD</sub> 均达到最小指定电压所需的上电时间 (电源变化必须是单向的) | 0.05  | -   | 500   | ms  |

## 建议的晶体规格

| 参数                | 说明           | 注释            | 最小值 | 典型值 | 最大值 | 单位  |

|-------------------|--------------|---------------|-----|-----|-----|-----|

| f <sub>NOM</sub>  | 额定晶体频率       | 并联谐振,基本模式     | 8   | -   | 30  | MHz |

| C <sub>LNOM</sub> | 额定负载电容       |               | 10  | -   | 20  | pF  |

| R <sub>1</sub>    | 等效串联电阻 (ESR) | 基本模式          | _   | -   | 50  | Ω   |

| DL                | 晶体驱动电平       | 假定不存在任何外部串联电阻 | _   | 0.5 | 12  | mW  |

### 直流电气特性

| 参数 [4]                                 | 说明    | 条件                                                                 | 最小值 | 典型值 | 最大值 | 单位       |

|----------------------------------------|-------|--------------------------------------------------------------------|-----|-----|-----|----------|

| I <sub>ОН3.3</sub>                     | 输出大电流 | $V_{OH} = V_{DD} - 0.5 \text{ V},  V_{DD}/V_{DDL} = 3.3 \text{ V}$ | 12  | 24  | _   | mA       |

| I <sub>OL3.3</sub>                     | 输出小电流 | $V_{OL} = 0.5 \text{ V}, V_{DD}/V_{DDL} = 3.3 \text{ V}$           | 12  | 24  | _   | mA       |

| I <sub>OH2.5</sub>                     | 输出大电流 | $V_{OH} = V_{DDL} - 0.5 \text{ V}, V_{DDL} = 2.5 \text{ V}$        | 8   | 16  | ı   | mA       |

| I <sub>OL2.5</sub>                     | 输出小电流 | $V_{OL} = 0.5 \text{ V}, V_{DDL} = 2.5 \text{ V}$                  | 8   | 16  | ı   | mA       |

| $V_{IH}$                               | 输入高电压 | CMOS 电平, V <sub>DD</sub> 的 70%                                     | 0.7 | -   | 1.0 | $V_{DD}$ |

| $V_{IL}$                               | 输入低电压 | CMOS 电平, V <sub>DD</sub> 的 30%                                     | 0   | -   | 0.3 | $V_{DD}$ |

| I <sub>VDD</sub> <sup>[5, 6]</sup>     | 供电电流  | AV <sub>DD</sub> /V <sub>DD</sub> 电流                               | -   | 45  | -   | mA       |

| I <sub>VDDL3.3</sub> <sup>[5, 6]</sup> | 供电电流  | V <sub>DDL</sub> 电流 (V <sub>DDL</sub> = 3.465 V)                   | -   | 25  | _   | mA       |

| I <sub>VDDL2.5</sub> <sup>[5, 6]</sup> | 供电电流  | V <sub>DDL</sub> 电流 (V <sub>DDL</sub> = 2.625 V)                   | _   | 17  | _   | mA       |

| I <sub>DDS</sub>                       | 断电电流  | $V_{DD} = V_{DDL} = AV_{DD} = 3.465 \text{ V}$                     | _   | _   | 50  | mA       |

| I <sub>OHZ</sub><br>I <sub>OLZ</sub>   | 输出漏电流 | $V_{DD} = V_{DDL} = AV_{DD} = 3.465 \text{ V}$                     | _   | _   | 10  | mA       |

### 交流电气特性

| 参数 [4]                        | 说明                                    | 条件                                                                                                 | 最小值           | 典型值  | 最大值   | 单位   |

|-------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------|---------------|------|-------|------|

| t <sub>1</sub>                | 输出频率、商业级温度                            | 时钟输出限制, 3.3 V                                                                                      | 0.008 (8 kHz) | _    | 200   | MHz  |

|                               |                                       | 时钟输出限制, 2.5 V                                                                                      | 0.008 (8 kHz) | _    | 166.6 | MHz  |

|                               | 输出频率、工业级温度                            | 时钟输出限制, 3.3 V                                                                                      | 0.008 (8 kHz) | _    | 166.6 | MHz  |

|                               |                                       | 时钟输出限制, 2.5 V                                                                                      | 0.008 (8 kHz) | _    | 150   | MHz  |

| t <sub>2</sub>                | 输出占空比                                 | 占空比定义在图 4 中, t <sub>1</sub> /t <sub>2</sub> ,<br>f <sub>OUT</sub> > 166 MHz, V <sub>DD</sub> 的 50% | 40            | 50   | 60    | %    |

|                               |                                       | 占空比定义在图 4 中, t <sub>1</sub> /t <sub>2</sub> ,<br>f <sub>OUT</sub> < 166 MHz, V <sub>DD</sub> 的 50% | 45            | 50   | 55    | %    |

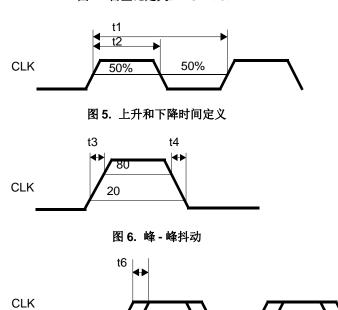

| t <sub>3LO</sub>              | 上升沿转换速率<br>(V <sub>DDL</sub> = 2.5 V) | 输出时钟上升时间,从 V <sub>DDL</sub> 的 20% 逐渐增大到 80%,如图 5 中所定义的内容                                           | 0.6           | 1.2  | _     | V/ns |

| t <sub>4LO</sub>              | 下降沿转换速率<br>(V <sub>DDL</sub> = 2.5 V) | 输出时钟下降时间,从 V <sub>DDL</sub> 的 80% 下降到 20%,如图 5 中所定义的内容                                             | 0.6           | 1.2  | _     | V/ns |

| t <sub>3HI</sub>              | 上升沿转换速率<br>(V <sub>DDL</sub> = 3.3 V) | 输出时钟上升时间,从 $V_{DD}/V_{DDL}$ 的 20% 逐渐增大到 80%,如图 5 中所定义的内容                                           | 0.8           | 1.4  | _     | V/ns |

| t <sub>4HI</sub>              | 下降沿转换速率<br>(V <sub>DDL</sub> = 3.3 V) | 输出时钟下降时间,从 V <sub>DD</sub> /V <sub>DDL</sub> 的 80% 下降到 20%,如图 5 中所定义的内容                            | 0.8           | 1.4  | _     | V/ns |

| t <sub>5</sub> <sup>[7]</sup> | 时滞                                    | 相关输出间的输出 — 输出时滞                                                                                    | _             | _    | 250   | ps   |

| t <sub>6</sub> <sup>[8]</sup> | 时钟抖动                                  | 峰 - 峰周期抖动 (请参考图 6)                                                                                 | _             | 250  | _     | ps   |

| t <sub>10</sub>               | PLL 锁定时间                              |                                                                                                    | _             | 0.30 | 3     | ms   |

- **注释:**4. 未经过 100% 测试,得到了设计保证。

5. 指定 I<sub>VDD</sub> 电流用于频率为 125 MHz 的两个 CLK 输出、频率为 80 MHz 的两个 LCLK 输出和频率为 66.6 MHz 的两个 LCLK 输出。所有输出的负载电容均为 15 pF。

6. 使用 CyClocksRT 为特定输出频率配置进行计算实际的 I<sub>VDD</sub> 和 I<sub>VDDL</sub> 大小。

7. 如果输出是由同一个分频器组生成的,那么时滞值得到保证。请参考逻辑框图了解更多信息。

8. 抖动测量将发生改变。实际抖动取决于 X<sub>IN</sub> 抖动及沿速率、有效输出数量、输出频率、V<sub>DDL</sub> (2.5 V 或 3.3 V)、温度和输出负载。欲了解更多有关信息,请参考http://www.cypress.com 网站上提供的应用笔记 "基于 PLL 系统中的抖动:原因、影响和解决方案"或联系您当地的赛普拉斯现场应用工程师。

### 测试电路

### 开关波形

图 4. 占空比定义: DC = t2/t1

### 订购信息

| 订购代码          | 封装类型                                             | 工作温度范围               | 工作电压  |

|---------------|--------------------------------------------------|----------------------|-------|

| CY22050KFC    | 16 引脚 TSSOP                                      | 商业级 (0℃至70℃)         | 3.3 V |

| CY22050KFI    | 16 引脚 TSSOP                                      | 工业级 (-40 °C 至 85 °C) | 3.3 V |

| 无铅            |                                                  |                      |       |

| CY22050KFZXC  | 16 引脚 TSSOP                                      | 商业级 (0°C至70°C)       | 3.3 V |

| CY22050KFZXCT | 16 引脚 TSSOP — 盘带封装                               |                      |       |

| CY22050KFZXI  | 16 引脚 TSSOP                                      | 工业级 (-40 °C 至 85 °C) | 3.3 V |

| 编程器           |                                                  |                      |       |

| CY3672-USB    | 编程套件                                             |                      |       |

| CY3695        | CY3672 编程器的 CY22050F、 CY22050KF 和 CY220501KF 适配器 |                      |       |

所提供的部分产品为用户特定的工厂可编程器件,它们带有已制定的器件型号。可能配置表显示了可用的器件类型,但未显示整个器件的型号。更多详细信息,请联系当地的赛普拉斯 FAE 或销售代表。

### 各种配置

| 订购代码                | 封装类型               | 工作温度范围             | 工作电压  |

|---------------------|--------------------|--------------------|-------|

| CY22050KZXI-xxx [9] | 16 引脚 TSSOP        | 工业级 (-40°C 至 85°C) | 3.3 V |

| CY22050KZXI-xxxT    | 16 引脚 TSSOP — 盘带封装 | 工业级 (-40°C 至 85°C) | 3.3 V |

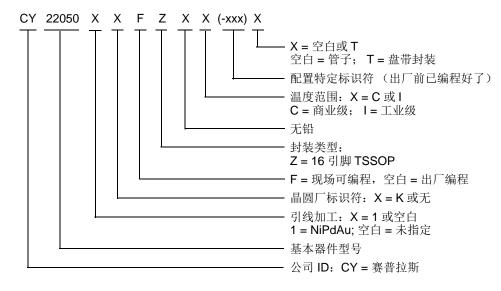

#### 订购代码定义

#### 注释:

9. 这些均是出厂编程配置。出厂编程适用于产量较大的设计(每年 100 Ku 或更多)。更多详细信息,请联系当地的赛普拉斯现场应用工程师或赛普拉斯销售代表。

### 16 引脚 TSSOP 封装特性

| 参数                | 名称       | 数值     | 单位   |

|-------------------|----------|--------|------|

| $\theta_{\sf JA}$ | theta JA | 115    | °C/W |

| 复杂性               | 晶体管计数    | 74,600 | 晶体管  |

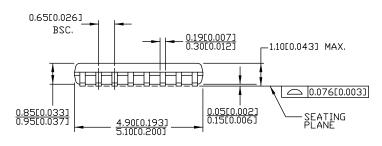

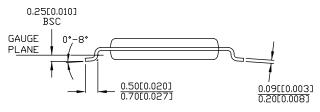

### 封装图和尺寸

### 图 7. 16 引脚 TSSOP 4.40 毫米芯片 Z16.173/ZZ16.173 封装外形, 51-85091

DIMENSIONS IN MM[INCHES] MIN. MAX.

REFERENCE JEDEC MD-153

PACKAGE WEIGHT 0.05gms

| PART #   |                |  |  |  |

|----------|----------------|--|--|--|

| Z16.173  | STANDARD PKG.  |  |  |  |

| ZZ16.173 | LEAD FREE PKG. |  |  |  |

51-85091 \*E

### 缩略语

| 缩略语   | 说明          |  |  |  |  |

|-------|-------------|--|--|--|--|

| ESR   | 等效串联电阻      |  |  |  |  |

| FAE   | 现场应用工程师     |  |  |  |  |

| I/O   | 输入/输出       |  |  |  |  |

| JEDEC | 联合电子器件工程委员会 |  |  |  |  |

| OE    | 输出使能        |  |  |  |  |

| PC    | 个人电脑        |  |  |  |  |

| PCB   | 印刷电路板       |  |  |  |  |

| PLL   | 锁相环         |  |  |  |  |

| TSSOP | 紧凑的小外形封装    |  |  |  |  |

| VCO   | 压控振荡器       |  |  |  |  |

### 文档规范

### 测量单位

| 符号  | 测量单位   |  |  |  |

|-----|--------|--|--|--|

| °C  | 摄氏度    |  |  |  |

| dBC | 分贝相对载波 |  |  |  |

| Hz  | 赫兹     |  |  |  |

| kHz | 千赫兹    |  |  |  |

| MHz | 兆赫兹    |  |  |  |

| μΑ  | 微安     |  |  |  |

| μF  | 微法     |  |  |  |

| mA  | 毫安     |  |  |  |

| mm  | 毫米     |  |  |  |

| ms  | 毫秒     |  |  |  |

| mW  | 毫瓦     |  |  |  |

| ns  | 纳秒     |  |  |  |

| Ω   | 欧姆     |  |  |  |

| %   | 百分比    |  |  |  |

| pF  | 皮法     |  |  |  |

| ps  | 皮秒     |  |  |  |

| V   | 伏特     |  |  |  |

| W   | 瓦特     |  |  |  |

## 文档修订记录

| 文档标题: CY22050/CY220501,带有一个锁相环的通用闪存可编程时钟发生器<br>文档编号: 001-95832 |         |      |            |                                     |  |

|----------------------------------------------------------------|---------|------|------------|-------------------------------------|--|

| 版本                                                             | ECN     | 变更者  | 提交日期       | 变更说明                                |  |

| **                                                             | 4691535 | WEIZ | 04/22/2015 | 本文档版本号为 Rev**,译自英文版 38-07006 Rev*M。 |  |

### 销售、解决方案和法律信息

#### 全球销售和设计支持

赛普拉斯公司拥有一个由办事处、解决方案中心、厂商代表和经销商组成的全球性网络。要找到距您最近的办事处,请访问赛普拉斯所在地。

#### 产品

汽车级产品 时钟与缓冲器 接口

照明与电源控制

存储器 PSoC

触摸感应产品 USB 控制器 无线/射频 cypress.com/go/automotive cypress.com/go/clocks cypress.com/go/interface cypress.com/go/powerpsoc cypress.com/go/plc cypress.com/go/memory cypress.com/go/psoc cypress.com/go/touch cypress.com/go/USB cypress.com/go/wireless

### PSoC® 解决方案

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

### 赛普拉斯开发者社区

社区 | 论坛 | 博客 | 视频 | 训练

#### 技术支持

cypress.com/go/support

② 赛普拉斯半导体公司, 2001-2015。此处所包含的信息可能会随时更改, 恕不另行通知。除赛普拉斯产品内嵌的电路外, 赛普拉斯半导体公司不对任何其他电路的使用承担任何责任。也不会以明示 或暗示的方式挖予任何专利许可或其他权利。除非与赛普拉斯签订明确的书面协议, 否则赛普拉斯不保证产品能够用于或适用于医疗、生命支持、救生、关键控制或安全应用领域。此外, 对于可能发 生运转异常和故障并对用户造成严重伤害的生命支持系统, 赛普拉斯不授权将其产品用作此类系统的关键组件。若将赛普拉斯产品用于生命支持系统,则表示制造商将承担因此类使用而招致的所有风 险, 并确保赛普拉斯免于因此而受到任何指控。

所有源代码(软件和/或固件)均归赛普拉斯半导体公司(赛普拉斯)所有,并受全球专利法规(美国和美国以外的专利法规)、美国版权法以及国际条约规定的保护和约束。赛普拉斯据此向获许可者授予适用于个人的、非独占性、不可转让的许可,用以复制、使用、修改、创建赛普拉斯源代码的派生作品、编译赛普拉斯源代码和派生作品,并且其目的只能是创建自定义软件和/或固件,以支持获许可者仅将其获得的产品依照适用协议规定的方式与赛普拉斯集成电路配合使用。除上述指定的用途外,未经赛普拉斯明确的书面许可,不得对此类源代码进行任何复制、修改、转换、编译或演示。

免责声明:赛普拉斯不针对此材料提供任何类型的明示或暗示保证,包括(但不限于)针对特定用途的适销性和适用性的暗示保证。赛普拉斯保留在不做出通知的情况下对此处所述材料进行更改的权利。赛普拉斯不对此处所述之任何产品或电路的应用或使用承担任何责任。对于合理预计可能发生运转异常和故障,并对用户造成严重伤害的生命支持系统,赛普拉斯不授权将其产品用作此类系统的关键组件。若将赛普拉斯产品用于生命支持系统中,则表示制造商将承担因此类使用而招致的所有风险,并确保赛普拉斯免于因此而受到任何指控。

产品使用可能受适用的赛普拉斯软件许可协议限制。