# **1Gb LPDDR2 Specification**

# Specifications

- Density: 1G bits

- Organization

- o 8 banks x 8M words x 16 bits

- Power supply

- $\circ$  V<sub>DD1</sub>=1.7 to 1.95V

- $\circ$  V<sub>DD2</sub>,V<sub>DDQ</sub>=1.14 to 1.3V

- Clock frequency

- 533/466/400/333/266/200/166Mhz (max.)

- 2KB page size

- Row address: AX0 to AX12

- Column address: AY0 to AY9 (x16 bits)

- 8 internal banks for concurrent operation

- Interface: HSUL\_12

- Burst lengths (BL): 4, 8, 16

- Burst type (BT)

- Sequential (4, 8, 16)

- Interleave (4, 8)

- Read latency (RL): 3, 4, 5, 6, 7, 8

- Write latency (WL): 1, 2, 3, 4

- Precharge: auto precharge option for each burst access

- Programmable driver strength

- **Refresh**: auto-refresh, self-refresh

- Average refresh period:

- o 7.8uS @≤85°C

- $\circ$  3.9uS @ > 85°C and ≤ 95°C

- 1.95uS @ > 95°C and ≤ 105°C

- Operating temperature range

- TC = -25°C to +85°C

- TC = -40°C to +105°C (extended range)

# Features

- DLL is not implemented

- Low power consumption

- JEDEC LPDDR2-S4B compliance

- Partial Array Self-Refresh (PASR)

- Auto Temperature Compensated Self-Refresh (ATCSR) by built-in temperature sensor

- Deep power-down mode

- Double-data-rate architecture; two data transfers per one clock cycle

- The high-speed data transfer is realized by the 8 bits prefetch pipelined architecture

- Differential clock inputs (CK and /CK)

- Commands entered on each positive CK edge; data and data mask referenced to both edges of DQS

- Data mask (DM) for write data

# **Differences from JEDEC:**

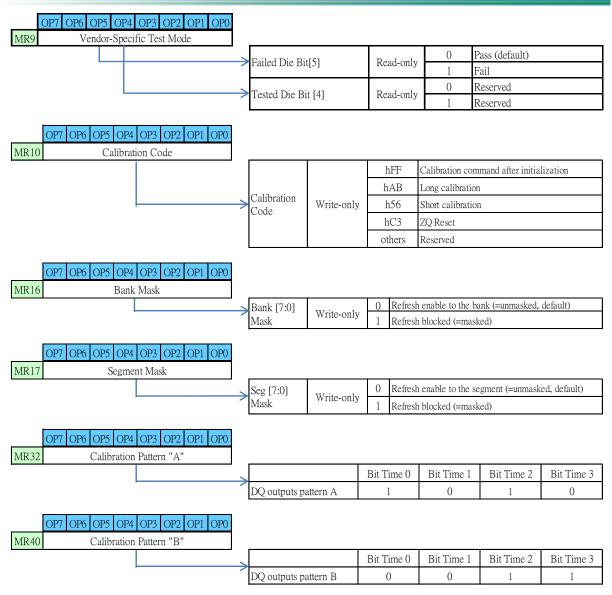

Mode Register 9, bit [5] is a readable Failed Die Bit

# **Table of Contents**

| 1 | Ordering Information:       | 4   |

|---|-----------------------------|-----|

| _ |                             |     |

| 2 | Package Ball Assignment     | 5   |

| 3 | Electrical Specifications:  | 7   |

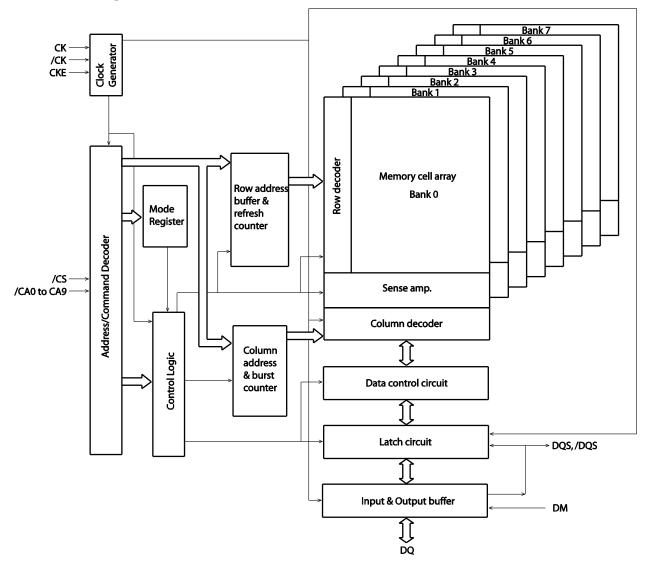

| 4 | Block Diagram               | 19  |

|   |                             |     |

| 5 | Pin Function                | .20 |

| 6 | Command Operation           | .23 |

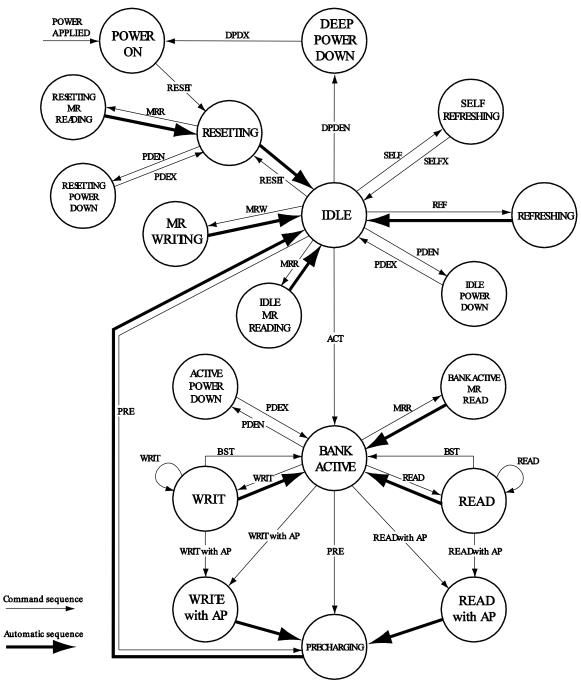

| 7 | Simplified State Diagram    | .26 |

| 8 | Operation of the LPDDR2 RAM | .27 |

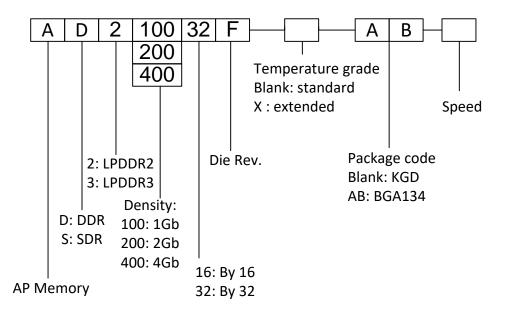

# **1** Ordering Information:

| Part Number    | Configuration | Temperature Range | Max Frequency | Note     |

|----------------|---------------|-------------------|---------------|----------|

| AD210032F      | X32           | -25°C to +85°C    | 533 MHz       | Bare die |

| AD210016F      | X16           | -25°C to +85°C    | 533 MHz       | Bare die |

| AD210032F-X    | X32           | -40°C to +105°C   | 533 MHz       | Bare die |

| AD210016F-X    | X16           | -40°C to +105°C   | 533 MHz       | Bare die |

| AD210032F-AB   | X32           | -25°C to +85°C    | 466 MHz       | Package  |

| AD210016F-AB   | X16           | -25°C to +85°C    | 466 MHz       | Package  |

| AD210032F-X-AB | X32           | -40°C to +105°C   | 466 MHz       | Package  |

| AD210016F-X-AB | X16           | -40°C to +105°C   | 466 MHz       | Package  |

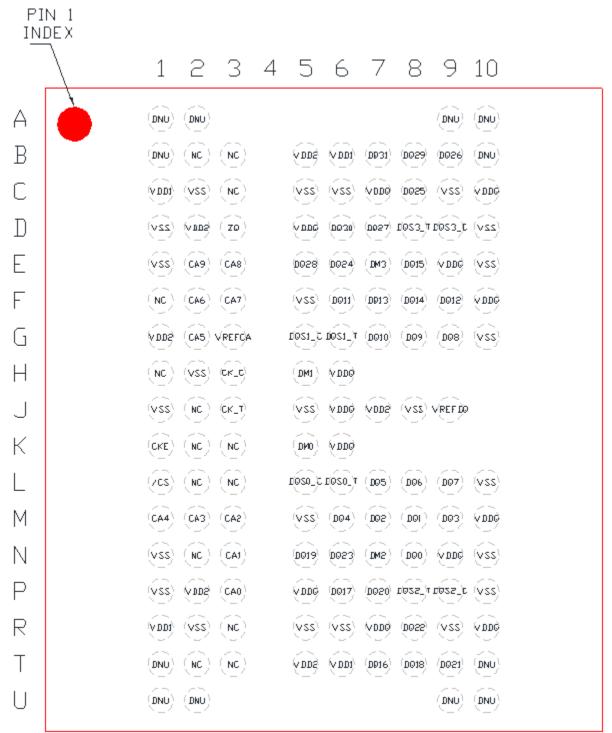

# 2 Package Ball Assignment

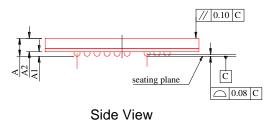

x32/x16: "134-Ball FBGA –10x11.5x1.0 mm, ball pitch 0.65 mm, ball size 0.4 mm. (package code AB)"

Top View

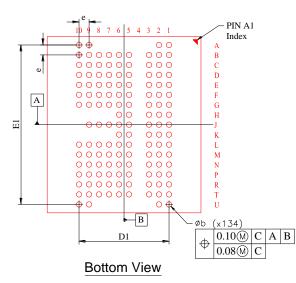

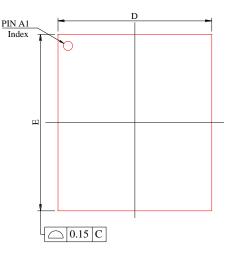

# Package Outline Drawing

# x32/x16: "134-Ball FBGA -10x11.5x1.0 mm, ball pitch 0.65 mm, ball size 0.4 mm. (package code AB)"

Top View

| G11    | MIL   | LIMETI  | ERS   |

|--------|-------|---------|-------|

| Symbol | MIN.  | NOM.    | MAX.  |

| А      |       |         | 1.00  |

| A1     | 0.27  | 0.32    | 0.37  |

| A2     | 0.545 | 0.58    | 0.63  |

| D      | 9.90  | 10.00   | 10.10 |

| D1     |       | 5.85 BS | С     |

| Е      | 11.40 | 11.50   | 11.60 |

| E1     |       | 10.40 B | SC    |

| b      | 0.35  | 0.40    | 0.45  |

| e      |       | 0.65 BS | С     |

# 3 Electrical Specifications:

All voltages are referenced to each GND level (VSS, VSSCA, and VSSQ). Execute power-up and Initialization sequence before proper device operation can be achieved.

# 3.1 Absolute Maximum Ratings

| Parameter                                                      | Symbol           | Rating       | Unit | Notes |

|----------------------------------------------------------------|------------------|--------------|------|-------|

| Voltage on any pin relative to $V_{SSCA}$ , $V_{SSQ}$          | VT               | -0.4 to +1.6 | V    |       |

| Power supply voltage (core power1) relative to V <sub>ss</sub> | V <sub>DD1</sub> | -0.4 to +2.3 | V    |       |

| Power supply voltage (core power2) relative to V <sub>ss</sub> | V <sub>DD2</sub> | -0.4 to +1.6 | V    |       |

| Power supply voltage for output relative to $V_{SSQ}$          | V <sub>DDQ</sub> | -0.4 to +1.6 | V    |       |

| Storage temperature                                            | T <sub>STG</sub> | -55 to +125  | °C   | 1     |

Notes:

Storage temperature the case surface temperature on the center/top side of the DRAM.

Caution:

Exposing the device to stress above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

# 3.2 Operating Temperature Condition

| Temperature Range | Symbol | Rating      | Unit | Notes |

|-------------------|--------|-------------|------|-------|

| Normal            | тс     | -25 to +85  | °C   | 1     |

| Extended          |        | -40 to +105 | °C   | 2     |

Notes:

Operating temperature is the case surface temperature on the center/top side of the DRAM. Refer to MR4 programming table for Temperature Sensor de-rating & refresh rate numbers.

# 3.3 Recommended DC Operating Conditions

| Para           | meter            | Symbol           | min. | typical | тах  | Unit | Notes |

|----------------|------------------|------------------|------|---------|------|------|-------|

|                | Core Power1      | V <sub>DD1</sub> | 1.7  | 1.8     | 1.95 | V    | 1     |

|                |                  | V <sub>SS</sub>  | 0    | 0       | 0    | V    |       |

| Supply voltage | Core Power2      | V <sub>DD2</sub> | 1.14 | 1.2     | 1.3  | V    | 1     |

| Supply voltage |                  | V <sub>SS</sub>  | 0    | 0       | 0    | V    |       |

|                |                  | V <sub>DDQ</sub> | 1.14 | 1.2     | 1.3  | V    | 1     |

|                | I/O Buffer Power | V <sub>SSQ</sub> | 0    | 0       | 0    | V    |       |

Notes:

$V_{\text{DDQ}}$  tracks with  $V_{\text{DD2}}.~$  AC parameters are measured with  $V_{\text{DD2}}$  and  $V_{\text{DDQ}}$  tied together.

# 3.4 AC and DC Input Measurement Levels

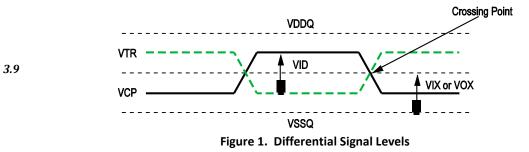

[Refer to section 8 in JEDEC Standard No. 209-2E]

# 3.5 DC Characteristics 1

|                                    |                                                                                                                                                                                                                                                                                                         |                               | D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Parameter                          | Test Condition                                                                                                                                                                                                                                                                                          | Symbol                        | Power<br>Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DDR<br>1066                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DDR<br>933                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DDR<br>800 | DDR<br>667                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DDR<br>533                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DDR<br>400                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DDR<br>333                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Unit |

| Operating one bank                 | Test ConditionSymbolPower<br>SupplyDDR<br>lossDDR<br>lossDDR<br>lossDDR<br>lossDDR<br>lossDDR<br>lossDDR<br>lossDDR<br>lossDDR<br>lossDDR<br>lossDDR<br>lossDDR<br>lossDDR<br>lossDDR<br>lossDDR<br>lossDDR<br>lossDDR<br>lossDDR<br>lossDDR<br>lossDDR<br>lossDDR<br>lossDDR<br>lossDDR<br>lossDDR<br> | mA                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| active-precharge                   | CS_n is HIGH between valid commands;                                                                                                                                                                                                                                                                    | $I_{\text{DD02}}$             | $\rm V_{DD2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            | DDR<br>800DDR<br>667DDR<br>333DDR<br>400DDR<br>333141470707070707011.40.81.40.81.40.81.51.51.581                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| current                            | Data bus inputs are STABLE                                                                                                                                                                                                                                                                              | $\mathrm{I}_{\mathrm{DD0IN}}$ | $V_{\text{DDQ}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DDR         DDR         DDR         DDR         DDR         BDR         BIN         BIN <td>mA</td> | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|                                    | t <sub>CK</sub> = t <sub>CK(min)</sub> ; CKE is LOW; CS_n is HIGH; all                                                                                                                                                                                                                                  | $I_{\text{DD2P1}}$            | $\rm V_{\rm DD1}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            | 0.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R DDR DDR DDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| Idle power-down<br>standby current | banks idle;<br>CA bus inputs are SWITCHING:                                                                                                                                                                                                                                                             | I <sub>dd2p2</sub>            | $\mathrm{V}_{\text{DD2}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            | 1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | mA   |

|                                    | Data bus inputs are STABLE                                                                                                                                                                                                                                                                              | I <sub>dd2pin</sub>           | $V_{\text{DDQ}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R DDR DDR DDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| Idle power-down                    | CK_t = LOW; CK_c = HIGH; CKE is LOW;                                                                                                                                                                                                                                                                    | I <sub>dd2ps1</sub>           | $\rm V_{\rm DD1}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            | 0.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | mA   |

| standby current                    | CS_n is HIGH; all banks idle;<br>CA bus inputs are STABLE:                                                                                                                                                                                                                                              | I <sub>dd2ps2</sub>           | $\mathrm{V}_{\text{DD2}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            | DDR<br>667     DDR<br>533     DDR<br>400     DDR<br>333     DDR<br>333     DDR<br>335       14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |