LMX2487E

SNAS404B - MAY 2007 - REVISED JANUARY 2016

# LMX2487E 7.5-GHz, High-Performance, Delta-Sigma Low-Power Dual PLLatinum™ Frequency Synthesizers With 3-GHz Integer PLL

#### **Features**

- Quadruple Modulus Prescaler for Lower Divids

- RF PLL: 16/17/20/21 or 32/33/36/37

- IF PLL: 8/9 or 16/17

- Advanced Delta Sigma Fractional Compensation

- 12-Bit or 22-Bit Selectable Fractional Modulus

- Up to 4th Order Programmable Delta-Sigma Modulator

- Features for Improved Lock Time

- Fastlock / Cycle Slip Reduction that Requires Single-Word Write

- Integrated Time-Out Counter

- Wide Operating Range

- LMX2487E RF PLL: 3.0 GHz to 7.5 GHz

- **Useful Features**

- Digital Lock Detect Output

- Hardware and Software Power-Down Control

- On-Chip Crystal Reference Frequency Doubler

- RF Phase Comparison Frequency Up to 50 MHz

- 2.5-V to 3.6-V Operation With  $I_{CC} = 8.5$  mA at 3.0 V

## 2 Applications

- Cellular Phones and Base Stations

- **Direct Digital Modulation Applications**

- Satellite and Cable TV Tuners

- WLAN Standards

## 3 Description

The LMX2487E device is a low power, high performance delta-sigma fractional-N PLL with an auxiliary integer-N PLL. It is fabricated using TI's advanced process.

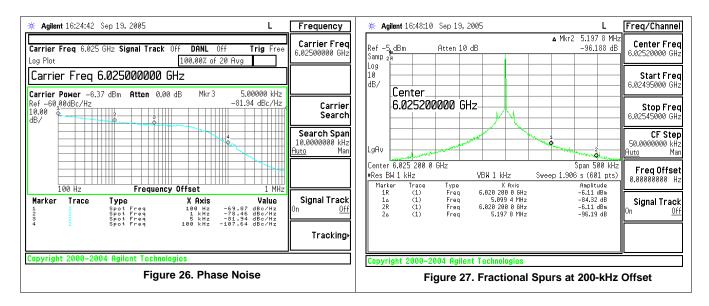

With delta-sigma architecture, fractional spurs at lower offset frequencies are pushed to higher frequencies outside the loop bandwidth. The ability to push close in spur and phase noise energy to higher frequencies is a direct function of the modulator order. Unlike analog compensation, the digital feedback technique used in the LMX2487E is highly resistant to changes in temperature and variations in wafer processing. The LMX2487E delta-sigma modulator is programmable up to fourth order, which allows the designer to select the optimum modulator order to fit the phase noise, spur, and lock time requirements of the system.

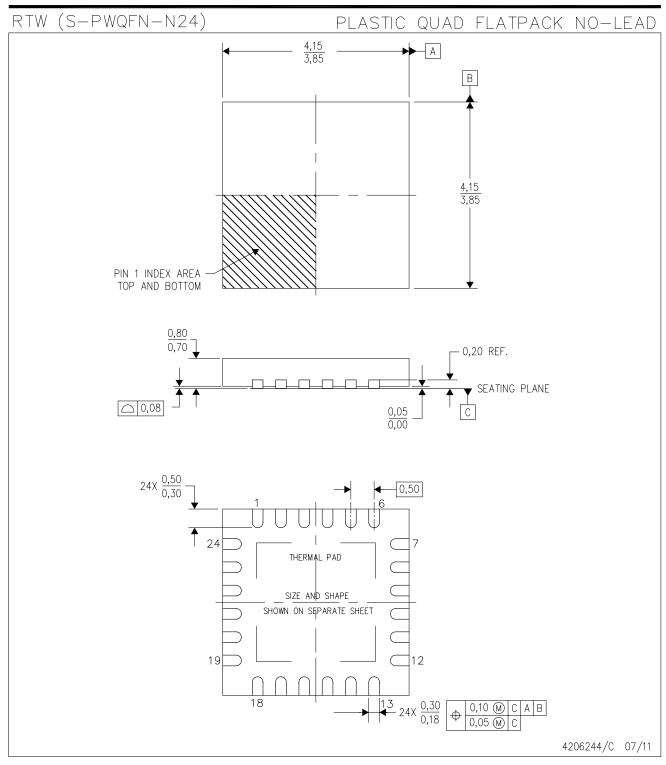

Serial data for programming the LMX2487E is transferred through a three-line, high-speed (20-MHz) MICROWIRE interface. The LMX2487E offers fine frequency resolution, low spurs, fast programming speed, and a single-word write to change the frequency. This makes it ideal for direct digital modulation applications, where the N-counter is directly modulated with information. The LMX2487E is available in a 24-lead 4.0 × 4.0 × 0.8 mm WQFN package.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| LMX2487E    | WQFN (24) | 4.00 mm × 4.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

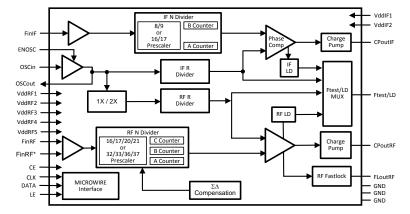

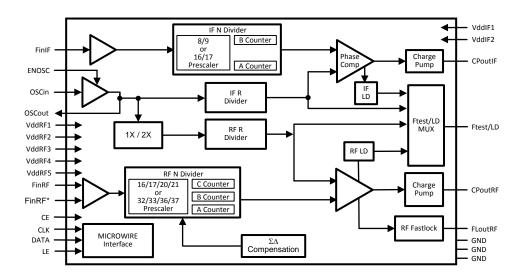

## **Functional Block Diagram**

| Table of C | ontents |

|------------|---------|

|------------|---------|

| 1 | Features 1                           |    | 8.3 Feature Description              | 1  |

|---|--------------------------------------|----|--------------------------------------|----|

| 2 | Applications 1                       |    | 8.4 Device Functional Modes          | 2  |

| 3 | Description 1                        |    | 8.5 Programming                      | 2  |

| 4 | Revision History2                    |    | 8.6 Register Maps                    | 20 |

| 5 | Pin Configuration and Functions      | 9  | Application and Implementation       | 3  |

| 6 | Specifications4                      |    | 9.1 Application Information          |    |

|   | 6.1 Absolute Maximum Ratings         |    | 9.2 Typical Application              | 38 |

|   | 6.2 ESD Ratings                      | 10 | Power Supply Recommendations         | 40 |

|   | 6.3 Recommended Operating Conditions | 11 | Layout                               | 40 |

|   | 6.4 Thermal Information              |    | 11.1 Layout Guidelines               | 40 |

|   | 6.5 Electrical Characteristics       |    | 11.2 Layout Example                  | 40 |

|   | 6.6 Timing Requirements              | 12 | Device and Documentation Support     | 4  |

|   | 6.7 Typical Characteristics          |    | 12.1 Community Resources             | 4º |

| 7 | Parameter Measurement Information    |    | 12.2 Trademarks                      | 4  |

| - | 7.1 Bench Test Set-Ups               |    | 12.3 Electrostatic Discharge Caution | 4  |

| 8 | Detailed Description                 |    | 12.4 Glossary                        | 4  |

| J | 8.1 Overview                         | 13 | Mechanical, Packaging, and Orderable | 4. |

|   | 8.2 Functional Block Diagram         |    | Information                          | 4  |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

## Changes from Revision A (March 2013) to Revision B

Page

## Changes from Original (March 2013) to Revision A

Page

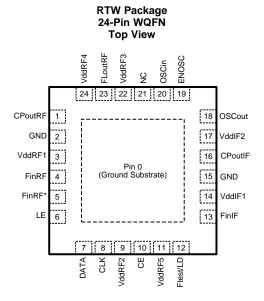

# 5 Pin Configuration and Functions

## **Pin Functions**

|     | PIN      | 1/0 | DESCRIPTION                                                                                                                                  |

|-----|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME     | I/O | DESCRIPTION                                                                                                                                  |

| 0   | GND      |     | Ground Substrate. This is on the bottom of the package and must be grounded.                                                                 |

| 1   | CPoutRF  | 0   | RF PLL charge pump output.                                                                                                                   |

| 2   | GND      |     | RF PLL analog ground.                                                                                                                        |

| 3   | VddRF1   |     | RF PLL analog power supply.                                                                                                                  |

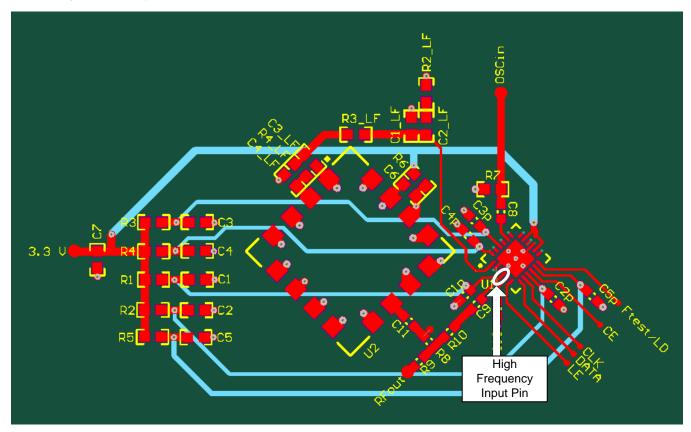

| 4   | FinRF    | I   | RF PLL high-frequency input pin.                                                                                                             |

| 5   | FinRF*   | -   | RF PLL complementary high-frequency input pin. Shunt to ground with a 100-pF capacitor.                                                      |

| 6   | LE       | 1   | MICROWIRE Load Enable. High-impedance CMOS input. Data stored in the shift registers is loaded into the internal latches when LE goes HIGH   |

| 7   | DATA     |     | MICROWIRE Data. High-impedance binary serial data input.                                                                                     |

| 8   | CLK      | 1   | MICROWIRE Clock. High-impedance CMOS Clock input. Data for the various counters is clocked into the 24-bit shift register on the rising edge |

| 9   | VddRF2   |     | Power supply for RF PLL digital circuitry.                                                                                                   |

| 10  | CE       | I   | Chip Enable control pin. Must be pulled high for normal operation.                                                                           |

| 11  | VddRF5   | I   | Power supply for RF PLL digital circuitry.                                                                                                   |

| 12  | Ftest/LD | 0   | Test frequency output / Lock Detect.                                                                                                         |

| 13  | FinIF    | I   | IF PLL high-frequency input pin.                                                                                                             |

| 14  | VddIF1   |     | IF PLL analog power supply.                                                                                                                  |

| 15  | GND      |     | IF PLL digital ground.                                                                                                                       |

| 16  | CPoutIF  | 0   | IF PLL charge pump output                                                                                                                    |

| 17  | VddIF2   |     | IF PLL power supply.                                                                                                                         |

| 18  | OSCout   | 0   | Buffered output of the OSCin signal.                                                                                                         |

| 19  | ENOSC    | 1   | Oscillator enable. When this is set to high, the OSCout pin is enabled regardless of the state of other pins or register bits.               |

| 20  | OSCin    | -   | Reference Input.                                                                                                                             |

| 21  | NC       | I   | This pin must be left open.                                                                                                                  |

| 22  | VddRF3   | _   | Power supply for RF PLL digital circuitry.                                                                                                   |

| 23  | FLoutRF  | 0   | RF PLL Fastlock Output. Also functions as Programmable TRI-STATE CMOS output.                                                                |

| 24  | VddRF4   | _   | RF PLL analog power supply.                                                                                                                  |

Copyright © 2007–2016, Texas Instruments Incorporated

## 6 Specifications

# 6.1 Absolute Maximum Ratings

See (1).

|                  |                                   | MIN  | MAX            | UNIT |

|------------------|-----------------------------------|------|----------------|------|

| $V_{CC}$         | Power supply voltage              | -0.3 | 4.25           | V    |

| Vi               | Voltage on any pin with GND = 0 V | -0.3 | $V_{CC} + 0.3$ | V    |

| TL               | Lead temperature (Solder 4 sec.)  |      | 260            | °C   |

| T <sub>stg</sub> | Storage temperature               | -65  | 150            | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                             |                            | VALUE | UNIT |

|--------------------|-----------------------------|----------------------------|-------|------|

|                    |                             | Human-body model (HBM)     | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge (1) | Charged-device model (CDM) | ±750  | V    |

|                    |                             | Machine model (MM)         | ±200  |      |

<sup>(1)</sup> This is a high performance RF device is ESD-sensitive. Handling and assembly of this device should be done at an ESD free workstation.

## 6.3 Recommended Operating Conditions

|                |                          | MIN | NOM | MAX | UNIT |

|----------------|--------------------------|-----|-----|-----|------|

| $V_{CC}$       | Power supply voltage (1) | 2.5 | 3   | 3.6 | V    |

| T <sub>A</sub> | Operating temperature    | -40 | 25  | 85  | °C   |

<sup>(1)</sup> Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Recommended Operating Conditions indicate conditions for which the device is intended to be functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see Electrical Characteristics. The ensured specifications apply only for the test conditions listed. The voltage at all the power supply pins of VddRF1, VddRF2, VddRF3, VddRF4, VddRF5, VddIF1 and VddIF2 must be the same. V<sub>CC</sub> will be used to refer to the voltage at these pins and I<sub>CC</sub> will be used to refer to the sum of all currents through all these power pins.

## 6.4 Thermal Information

|                      | (4)                                          | LMX2485,<br>LMX2485E |      |

|----------------------|----------------------------------------------|----------------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RTW (WQFN)           | UNIT |

|                      |                                              | 24 PINS              |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 47.2                 | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 43                   | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 24                   | °C/W |

| $\Psi_{JT}$          | Junction-to-top characterization parameter   | 0.8                  | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 24                   | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 7                    | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 6.5 Electrical Characteristics

$(V_{cc} = 3.0V: -40^{\circ}C \le T_{A} \le +85^{\circ}C$  unless otherwise specified)

|                            | PARAMETER                                     | TEST CO                                                       | ONDITIONS                | MIN         | TYP      | MAX             | UNIT      |

|----------------------------|-----------------------------------------------|---------------------------------------------------------------|--------------------------|-------------|----------|-----------------|-----------|

| I <sub>CC</sub> PARAMETERS |                                               |                                                               |                          |             |          |                 |           |

| I <sub>cc</sub> RF         | Power supply current, RF synthesizer          | IF PLL OFF<br>RF PLL ON<br>Charge pump TRI-STATE              |                          |             | 5.7      |                 | mA        |

| I <sub>cc</sub> IF         | Power supply current, IF synthesizer          | IF PLL ON<br>RF PLL OFF<br>Charge pump TRI-STATE              |                          |             | 2.5      |                 | mA        |

| <sub>CC</sub> TOTAL        | Power supply current, entire synthesizer      | IF PLL ON<br>RF PLL ON<br>Charge pump TRI-STATE               |                          |             | 8.5      |                 | mA        |

| l <sub>cc</sub> PD         | Power-down current                            | CE = ENOSC = 0 V<br>CLK, DATA, LE = 0 V                       |                          |             | < 1      |                 | μΑ        |

| RF SYNTHESIZER PA          | ARAMETERS                                     | 1                                                             |                          | <u> </u>    |          |                 |           |

| FinRF                      | Operating LMX2487E                            | RF_P = 16                                                     |                          | 3000        |          | 4000            | MHz       |

|                            |                                               | RF_P = 32<br>3-6 GHz                                          |                          | 3000<br>-10 |          | 7500            | dBm       |

| P <sub>FinRF</sub>         | Input sensitivity                             | 6-7.5 GHz                                                     |                          | -5          |          | 5               | abiii     |

| COMP                       | Phase detector frequency <sup>(1)</sup>       |                                                               |                          |             |          | 50              | MHz       |

|                            |                                               | $RF\_CPG = 0$ $V_{CPoutRF} = V_{CC}/2$                        |                          |             | 95       |                 | μΑ        |

| <sub>CPoutRF</sub> SRCE    | RF charge pump source current <sup>(2)</sup>  | $RF\_CPG = 1$ $V_{CPoutRF} = V_{CC}/2$                        |                          |             | 190      |                 | μΑ        |

|                            |                                               |                                                               |                          |             |          |                 | μΑ        |

|                            |                                               | $RF\_CPG = 15$ $V_{CPoutRF} = V_{CC}/2$                       |                          |             | 1520     |                 | μΑ        |

|                            |                                               | $RF\_CPG = 0$ $V_{CPoutRF} = V_{CC}/2$                        |                          |             | -95      |                 | μА        |

| <sub>CPoutRF</sub> SINK    | RF charge pump sink current <sup>(2)</sup>    | $RF\_CPG = 1$ $V_{CPoutRF} = V_{CC}/2$                        |                          |             | -190     |                 | μА        |

|                            |                                               |                                                               |                          |             |          |                 | μΑ        |

|                            |                                               | $RF\_CPG = 15$ $V_{CPoutRF} = V_{CC}/2$                       |                          |             | -1520    |                 | μΑ        |

| <sub>CPoutRF</sub> TRI     | RF charge pump TRI-STATE current magnitude    | $0.5 \le V_{CPoutRF} \le V_{CC}$ -0.5                         |                          |             | 2        | 10              | nA        |

| I <sub>CPoutRF</sub> %MIS  | Magnitude of RF CP sink vs CP source mismatch | $V_{CPoutRF} = V_{CC}/2$<br>$T_A = 25^{\circ}C$               | RF_CPG > 2<br>RF_CPG ≤ 2 |             | 3%<br>3% | 10%<br>13%      |           |

| I <sub>CPoutRF</sub> %V    | Magnitude of RF CP current vs CP voltage      | $0.5 \le V_{CPoutRF} \le V_{CC}$ -0.5<br>$T_A = 25^{\circ}C$  | 111_01012                |             | 2%       | 8%              |           |

| I <sub>CPoutRF</sub> %T    | Magnitude of RF CP current vs temperature     | $V_{CPoutRF} = V_{CC}/2$                                      |                          |             | 4%       |                 |           |

| F SYNTHESIZER PAR          | ·                                             |                                                               |                          |             |          |                 |           |

|                            |                                               | IF_P = 8                                                      |                          | 250         |          | 2000            |           |

| FinIF                      | Operating frequency                           | IF_P = 16                                                     |                          | 250         |          | 3000            | MHz       |

| P <sub>FinIF</sub>         | IF input sensitivity                          |                                                               |                          | -10         |          | 5               | dBm       |

| COMP                       | Phase detector frequency                      |                                                               |                          |             |          | 10              | MHz       |

| CPoutIFSRCE                | IF charge pump source current                 | $V_{CPoutlF} = V_{CC}/2$                                      |                          |             | 3.5      |                 | mA        |

| <sub>CPoutIF</sub> SINK    | IF charge pump sink current                   | V <sub>CPoutIF</sub> = V <sub>CC</sub> /2                     |                          |             | -3.5     |                 | mA        |

| <sub>CPoutIF</sub> TRI     | IF charge pump TRI-STATE current magnitude    | $0.5 \le V_{CPoutlF} \le V_{CC} RF - 0$                       | .5                       |             | 2        | 10              | nA        |

| I <sub>CPoutIF</sub> %MIS  | Magnitude of IF CP sink vs CP source mismatch | $V_{CPoutIF} = V_{CC}/2$<br>$T_A = 25$ °C                     |                          |             | 1%       | 8%              |           |

| I <sub>CPoutIF</sub> %V    | Magnitude of IF CP current vs CP voltage      | $0.5 \le V_{CPoutlF} \le V_{CC} - 0.5$<br>$T_A = 25^{\circ}C$ |                          |             | 4%       | 10%             |           |

| I <sub>CPoutlF</sub> %TEMP | Magnitude of IF CP current vs temperature     | V <sub>CPoutIF</sub> = V <sub>CC</sub> /2                     |                          |             | 4%       |                 |           |

| OSCILLATOR PARAM           | METERS                                        | ı                                                             |                          |             |          | I               |           |

|                            |                                               | OSC2X = 0                                                     |                          | 5           |          | 110             | MHz       |

| f <sub>oscin</sub>         | Oscillator operating frequency                | OSC2X = 1                                                     |                          | 5           |          | 20              | MH        |

|                            |                                               |                                                               |                          |             |          |                 |           |

| V <sub>OSCin</sub>         | Oscillator input sensitivity                  |                                                               |                          | 0.5         |          | V <sub>cc</sub> | $V_{P-P}$ |

<sup>(1)</sup> For Phase Detector Frequencies above 20 MHz, Cycle Slip Reduction (CSR) may be required. Legal divide ratios are also required.

(2) Refer to table in *RF\_CPG - RF PLL Charge Pump Gain* for complete listing of charge pump currents.

## **Electrical Characteristics (continued)**

$(V_{CC} = 3.0V; -40^{\circ}C \le T_{A} \le +85^{\circ}C$  unless otherwise specified)

|                      | PARAMETER                                                         | TEST CONDITIONS           | MIN                                          | TYP MAX         | UNIT   |

|----------------------|-------------------------------------------------------------------|---------------------------|----------------------------------------------|-----------------|--------|

| SPURS                |                                                                   |                           |                                              |                 |        |

|                      | Spurs in band <sup>(3)</sup>                                      |                           |                                              | -55             | dBc    |

| PHASE NOISE          |                                                                   |                           | •                                            |                 |        |

|                      |                                                                   | RF_CPG = 0                |                                              | -202            |        |

|                      |                                                                   | RF_CPG = 1                |                                              | -204            | •      |

| $L_{F1Hz}RF$         | RF synthesizer normalized phase noise contribution <sup>(4)</sup> | RF_CPG = 3                |                                              | -206            | dBc/Hz |

|                      | noise continuation                                                | RF_CPG = 7                |                                              | -210            | •      |

|                      |                                                                   | RF_CPG = 15               |                                              | -210            | •      |

| L <sub>F1Hz</sub> IF | IF synthesizer normalized phase noise contribution                |                           |                                              | -209            | dBc/Hz |

| DIGITAL INTERF       | FACE (DATA, CLK, LE, ENOSC, CE, Ftest/LD, FL                      | outRF)                    | <u>,                                    </u> |                 |        |

| V <sub>IH</sub>      | High-level input voltage                                          |                           | 1.6                                          | V <sub>cc</sub> | V      |

| V <sub>IL</sub>      | Low-level input voltage                                           |                           |                                              | 0.4             | V      |

| I <sub>IH</sub>      | High-level input current                                          | $V_{IH} = V_{CC}$         | -1                                           | 1               | μA     |

| I <sub>IL</sub>      | Low-level input current                                           | V <sub>IL</sub> = 0 V     | -1                                           | 1               | μA     |

| V <sub>OH</sub>      | High-level output voltage                                         | I <sub>OH</sub> = -500 μA | V <sub>CC</sub> - 0.4                        |                 | V      |

| V <sub>OL</sub>      | Low-level output voltage                                          | I <sub>OL</sub> = 500 μA  |                                              | 0.4             | V      |

- (3) In order to measure the in-band spur, the fractional word is chosen such that when reduced to lowest terms, the fractional numerator is one. The spur offset frequency is chosen to be the comparison frequency divided by the reduced fractional denominator. The loop bandwidth must be sufficiently wide to negate the impact of the loop filter. Measurement conditions are: Spur Offset Frequency = 10 kHz, Loop Bandwidth = 100 kHz, Fraction = 1/2000, Comparison Frequency = 20 MHz, RF\_CPG = 7, DITH = 0, VCO Frequency = 3 GHz, and a 4th Order Modulator (FM = 0). These are relatively consistent over tuning range.

- (4) Normalized Phase Noise Contribution is defined as: L<sub>N</sub>(f) = L(f) 20log(N) 10log(f<sub>COMP</sub>) where L(f) is defined as the single side band phase noise measured at an offset frequency, f, in a 1-Hz Bandwidth. The offset frequency, f, must be chosen sufficiently smaller than the PLL loop bandwidth, yet large enough to avoid substantial phase noise contribution from the reference source. Measurement conditions are: Offset Frequency = 11 kHz, Loop Bandwidth = 100 kHz for RF\_CPG = 7, Fraction = 1/2000, Comparison Frequency = 20 MHz, FM = 0, DITH = 0, VCO Frequency = 3 GHz.

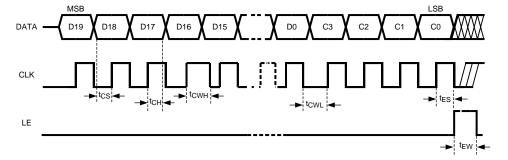

## 6.6 Timing Requirements

|                  |                                  |              | MIN | NOM | MAX | UNIT |

|------------------|----------------------------------|--------------|-----|-----|-----|------|

| MICRO            | WIRE INTERFACE TIMING            |              |     |     |     |      |

| t <sub>CS</sub>  | Data to clock set-up time        | See Figure 1 | 25  |     |     | ns   |

| t <sub>CH</sub>  | Data to clock hold time          | See Figure 1 | 8   |     |     | ns   |

| t <sub>CWH</sub> | Clock pulse width high           | See Figure 1 | 25  |     |     | ns   |

| $t_{\text{CWL}}$ | Clock pulse width low            | See Figure 1 | 25  |     |     | ns   |

| t <sub>ES</sub>  | Clock to load enable set-up time | See Figure 1 | 25  |     |     | ns   |

| t <sub>EW</sub>  | Load enable pulse width          | See Figure 1 | 25  |     |     | ns   |

Figure 1. MICROWIRE Input Timing Diagram

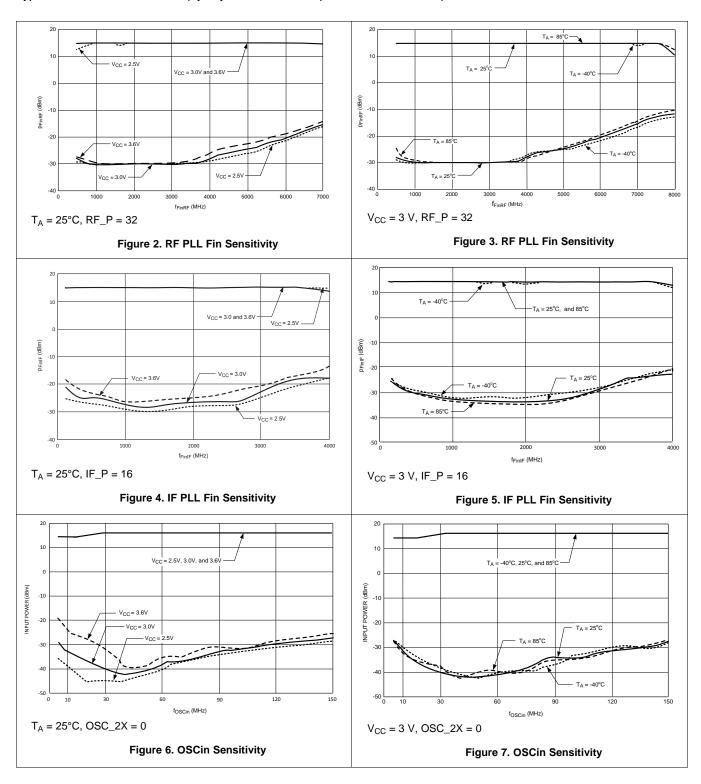

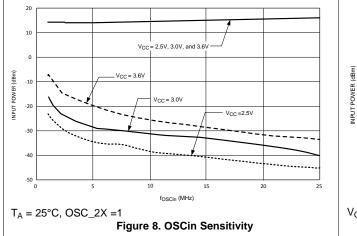

## 6.7 Typical Characteristics

## 6.7.1 Sensitivity

Typical characteristics do not imply any sort of ensured specification. Ensured specifications are in *Electrical Characteristics*.

# STRUMENTS

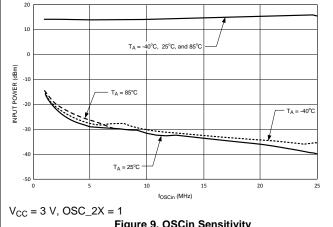

# Sensitivity (continued)

Typical characteristics do not imply any sort of ensured specification. Ensured specifications are in *Electrical Characteristics*.

Figure 9. OSCin Sensitivity

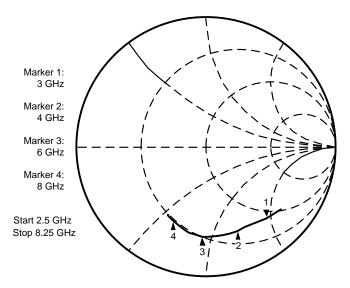

## 6.7.2 FinRF Input Impedance

Typical characteristics do not imply any sort of ensured specification. Ensured specifications are in *Electrical Characteristics*.

Figure 10. FinRF Input Impedance

Table 1. RF PLL Input Impedance

|                 | FinRF INPUT IMPEDANCE |               |

|-----------------|-----------------------|---------------|

| FREQUENCY (MHz) | REAL (Ω)              | IMAGINARY (Ω) |

| 3000            | 39                    | -94           |

| 3200            | 37                    | -86           |

| 3400            | 33                    | -78           |

| 3600            | 30                    | -72           |

| 3800            | 28                    | -69           |

| 4000            | 26                    | -66           |

| 4250            | 24                    | -63           |

| 4500            | 23                    | -60           |

| 4750            | 22                    | -57           |

| 5000            | 20                    | -54           |

| 5250            | 19                    | -50           |

| 5500            | 18                    | -49           |

| 5750            | 17                    | -47           |

| 6000            | 17                    | -45           |

| 6250            | 16                    | -44           |

| 6500            | 16                    | -42           |

| 6750            | 16                    | -40           |

| 7000            | 16                    | -39           |

| 7250            | 16                    | -37           |

| 7500            | 16                    | -35           |

| 7750            | 17                    | -33           |

| 8000            | 17                    | -30           |

| 8250            | 16                    | -27           |

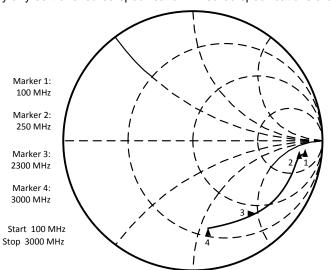

## 6.7.3 FinIF Input Impedance

Typical characteristics do not imply any sort of ensured specification. Ensured specifications are in *Electrical Characteristics*.

Figure 11. FinIF Input Impedance

Table 2. IF PLL Input Impedance

| FinIF INPUT IMPEDANCE |          |               |  |  |  |  |  |  |  |  |  |

|-----------------------|----------|---------------|--|--|--|--|--|--|--|--|--|

| FREQUENCY (MHz)       | REAL (Ω) | IMAGINARY (Ω) |  |  |  |  |  |  |  |  |  |

| 100                   | 508      | -233          |  |  |  |  |  |  |  |  |  |

| 150                   | 456      | -215          |  |  |  |  |  |  |  |  |  |

| 200                   | 420      | -206          |  |  |  |  |  |  |  |  |  |

| 250                   | 403      | -205          |  |  |  |  |  |  |  |  |  |

| 300                   | 370      | -207          |  |  |  |  |  |  |  |  |  |

| 400                   | 344      | -215          |  |  |  |  |  |  |  |  |  |

| 500                   | 207      | -223          |  |  |  |  |  |  |  |  |  |

| 600                   | 274      | -225          |  |  |  |  |  |  |  |  |  |

| 700                   | 242      | -225          |  |  |  |  |  |  |  |  |  |

| 800                   | 242      | -225          |  |  |  |  |  |  |  |  |  |

| 900                   | 214      | -222          |  |  |  |  |  |  |  |  |  |

| 1000                  | 171      | -208          |  |  |  |  |  |  |  |  |  |

| 1200                  | 137      | -191          |  |  |  |  |  |  |  |  |  |

| 1400                  | 112      | -176          |  |  |  |  |  |  |  |  |  |

| 1600                  | 91       | -158          |  |  |  |  |  |  |  |  |  |

| 1800                  | 76       | -139          |  |  |  |  |  |  |  |  |  |

| 2000                  | 62       | -122          |  |  |  |  |  |  |  |  |  |

| 2200                  | 51       | -105          |  |  |  |  |  |  |  |  |  |

| 2300                  | 46       | -96           |  |  |  |  |  |  |  |  |  |

| 2400                  | 42       | -88           |  |  |  |  |  |  |  |  |  |

| 2600                  | 37       | -74           |  |  |  |  |  |  |  |  |  |

| 2800                  | 29       | -63           |  |  |  |  |  |  |  |  |  |

| 3000                  | 25       | -54           |  |  |  |  |  |  |  |  |  |

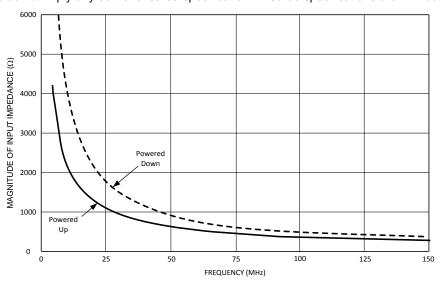

## 6.7.4 OSCin Input Impedance

Typical characteristics do not imply any sort of ensured specification. Ensured specifications are in *Electrical Characteristics*.

Figure 12. OSCin Input Impedance

Table 3. OSCin Input Impedance

| FREQUENCY |      | POWERED UP |           |      | POWERED DOWN |           |  |  |  |  |

|-----------|------|------------|-----------|------|--------------|-----------|--|--|--|--|

| (MHz)     | REAL | IMAGINARY  | MAGNITUDE | REAL | IMAGINARY    | MAGNITUDE |  |  |  |  |

| 5         | 1730 | -3779      | 4157      | 392  | -8137        | 8146      |  |  |  |  |

| 10        | 846  | -2236      | 2391      | 155  | -4487        | 4490      |  |  |  |  |

| 20        | 466  | -1196      | 1284      | 107  | -2215        | 2217      |  |  |  |  |

| 30        | 351  | -863       | 932       | 166  | -1495        | -1504     |  |  |  |  |

| 40        | 316  | -672       | 742       | 182  | -1144        | 1158      |  |  |  |  |

| 50        | 278  | -566       | 631       | 155  | -912         | 925       |  |  |  |  |

| 60        | 261  | -481       | 547       | 153  | -758         | 774       |  |  |  |  |

| 70        | 252  | -425       | 494       | 154  | -652         | 669       |  |  |  |  |

| 80        | 239  | -388       | 456       | 147  | -576         | 595       |  |  |  |  |

| 90        | 234  | -358       | 428       | 145  | -518         | 538       |  |  |  |  |

| 100       | 230  | -337       | 407       | 140  | -471         | 492       |  |  |  |  |

| 110       | 225  | -321       | 392       | 138  | -436         | 458       |  |  |  |  |

| 120       | 219  | -309       | 379       | 133  | -402         | 123       |  |  |  |  |

| 130       | 214  | -295       | 364       | 133  | -374         | 397       |  |  |  |  |

| 140       | 208  | -285       | 353       | 132  | -349         | 373       |  |  |  |  |

| 150       | 207  | -279       | 348       | 133  | -329         | 355       |  |  |  |  |

# TEXAS INSTRUMENTS

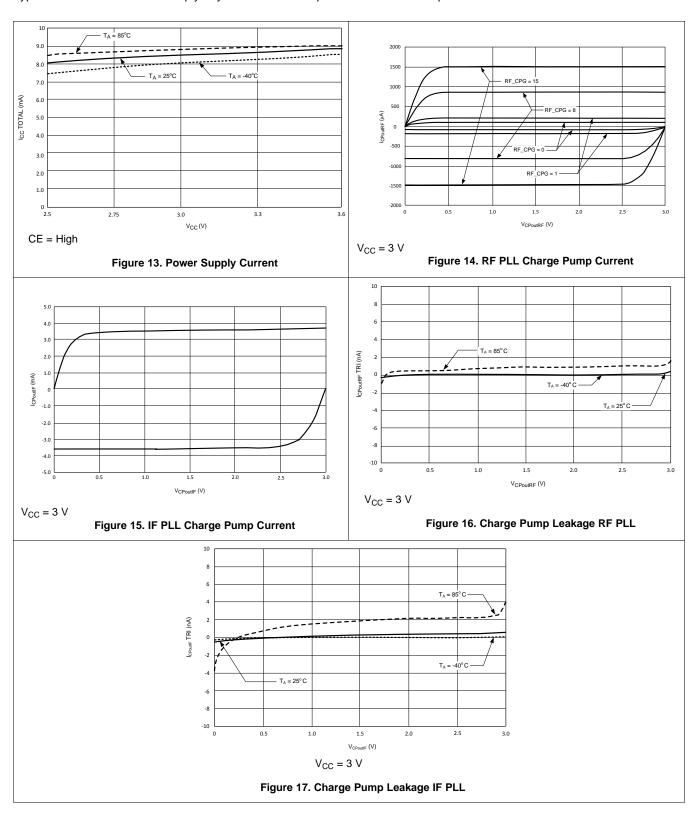

#### 6.7.5 Currents

Typical characteristics do not imply any sort of ensured specification. Ensured specifications are in *Electrical Characteristics*.

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

## 7 Parameter Measurement Information

#### 7.1 Bench Test Set-Ups

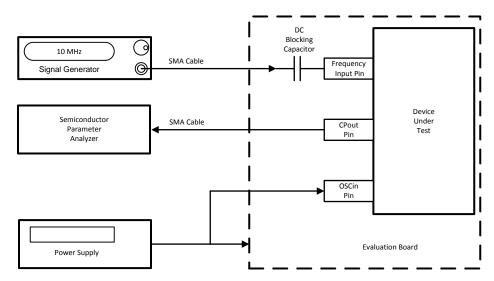

### 7.1.1 Charge Pump Current Measurement

Figure 18. Charge Pump Current Measurement

Figure 18 shows the test procedure for testing the RF and IF charge pumps. These tests include absolute current level, mismatch, and leakage measurement. In order to measure the charge pump currents, a signal is applied to the high frequency input pins. The reason for this is to ensure that the phase detector gets enough transitions in order to be able to change states. If no signal is applied, it is possible that the charge pump current reading will be low due to the fact that the duty cycle is not 100%. The OSCin Pin is tied to the supply. The charge pump currents can be measured by simply programming the phase detector to the necessary polarity. For instance, in order to measure the RF charge pump, a 10-MHz signal is applied to the FinRF pin. The source current can be measured by setting the RF PLL phase detector to a positive polarity, and the sink current can be measured by setting the phase detector to a negative polarity. The IF PLL currents can be measured in a similar way.

## **NOTE**

The magnitude of the RF PLL charge pump current is controlled by the RF\_CPG bit. Once the charge pump currents are known, the mismatch can be calculated as well. In order to measure leakage, the charge pump is set to a TRI-STATE mode by enabling the RF\_CPT and IF\_CPT bits. The table below shows a summary of the various charge pump tests.

**Table 4. Charge Pump Test Programming**

| CURRENT TEST | RF_CPG  | RF_CPP | RF_CPT | IF_CPP | IF_CPT |

|--------------|---------|--------|--------|--------|--------|

| RF Source    | 0 to 15 | 0      | 0      | X      | X      |

| RF Sink      | 0 to 15 | 1      | 0      | X      | X      |

| RF TRI-STATE | X       | X      | 1      | X      | X      |

| IF Source    | X       | X      | X      | 0      | 0      |

| IF Sink      | X       | X      | X      | 1      | 0      |

| IF TRI-STATE | X       | Х      | Х      | Х      | 1      |

# TEXAS INSTRUMENTS

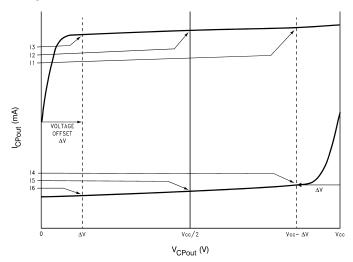

## 7.1.2 Charge Pump Current Specification Definitions

Figure 19. Charge Pump Definitions

I1 = Charge Pump Sink Current at  $V_{CPout} = Vcc - \Delta V$

I2 = Charge Pump Sink Current at V<sub>CPout</sub> = Vcc/2

I3 = Charge Pump Sink Current at  $V_{CPout} = \Delta V$

I4 = Charge Pump Source Current at  $V_{CPout} = Vcc - \Delta V$

I5 = Charge Pump Source Current at V<sub>CPout</sub> = Vcc/2

I6 = Charge Pump Source Current at  $V_{CPout} = \Delta V$

$\Delta V$  = Voltage offset from the positive and negative supply rails. Defined to be 0.5 V for this part.

$v_{\text{CPout}}$  refers to either  $V_{\text{CPoutRF}}$  or  $V_{\text{CPoutIF}}$

$I_{CPout}$  refers to either  $I_{CPoutRF}$  or  $I_{CPoutIF}$

### 7.1.2.1 Charge Pump Output Current Variation vs Charge Pump Output Voltage

$$I_{CPout} \ V_{S} \ V_{CPout} = \frac{(|11| - |13|)}{(|11| + |13|)} \times 100\%$$

$$= \frac{(|14| - |16|)}{(|14| + |16|)} \times 100\%$$

(1)

## 7.1.2.2 Charge Pump Sink Current vs Charge Pump Output Source Current Mismatch

$$I_{CPout}$$

Sink Vs  $I_{CPout}$  Source =  $\frac{|12| - |15|}{\frac{1}{2}(|12| + |15|)} \times 100\%$  (2)

## 7.1.2.3 Charge Pump Output Current Variation vs Temperature

$$I_{CPout} \ Vs \ T_{A} = \frac{|I_{2}||_{T_{A}} - |I_{2}||_{T_{A} = 25 \circ C}}{|I_{2}||_{T_{A} = 25 \circ C}} \times 100\%$$

$$= \frac{|I_{5}||_{T_{A}} - |I_{5}||_{T_{A} = 25 \circ C}}{|I_{5}||_{T_{A} = 25 \circ C}} \times 100\%$$

(3)

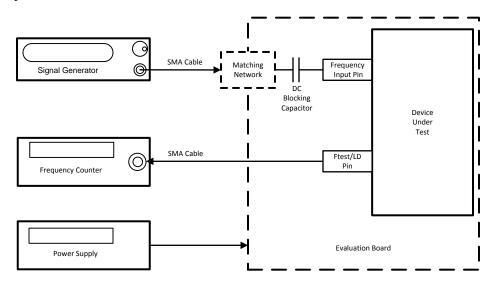

## 7.1.3 Sensitivity Measurement

Figure 20. Setup for Sensitivity Measurement

**Table 5. Settings for Sensitivity Measurement**

| FREQUENCY INPUT PIN | DC-BLOCKING<br>CAPACITOR | CORRESPONDING<br>COUNTER | DEFAULT COUNTER<br>VALUE | MUX VALUE |

|---------------------|--------------------------|--------------------------|--------------------------|-----------|

| OSCin               | 1000 pF                  | RF_R / 2                 | 50                       | 14        |

| FinRF               | 100 pF// 1000 pF         | RF_N / 2                 | 502 + 2097150 / 4194301  | 15        |

| FinIF               | 100 pF                   | IF_N / 2                 | 534                      | 13        |

| OSCin               | 1000 pF                  | IF_R / 2                 | 50                       | 12        |

Sensitivity is defined as the power level limits beyond which the output of the counter being tested is off by 1 Hz or more of its expected value. It is typically measured over frequency, voltage, and temperature. In order to test sensitivity, the MUX[3:0] word is programmed to the appropriate value. The counter value is then programmed to a fixed value and a frequency counter is set to monitor the frequency of this pin. The expected frequency at the Ftest/LD pin should be the signal generator frequency divided by twice the corresponding counter value. The factor of two comes in because the LMX2487E has a flip-flop which divides this frequency by two to make the duty cycle 50% in order to make it easier to read with the frequency counter. The frequency counter input impedance should be set to high impedance. In order to perform the measurement, the temperature, frequency, and voltage is set to a fixed value and the power level of the signal is varied.

## NOTE

The power level at the part is assumed to be 4 dB less than the signal generator power level. This accounts for 1 dB for cable losses and 3 dB for the pad.

The power level range where the frequency is correct at the Ftest/LD pin to within 1 Hz accuracy is recorded for the sensitivity limits. The temperature, frequency, and voltage can be varied in order to produce a family of sensitivity curves. Because this is an open-loop test, the charge pump is set to TRI-STATE and the unused side of the PLL (RF or IF) is powered down when not being tested. For this part, there are actually four frequency input pins, although there is only one frequency test pin (Ftest/LD). The conditions specific to each pin are shown in the table in the *Charge Pump Current Specification Definitions* section.

#### **NOTE**

That for the RF N counter, a fourth order fractional modulator is used in 22-bit mode with a fraction of 2097150 / 4194301 is used. The reason for this long fraction is to test the RF N counter and supporting fractional circuitry as completely as possible.

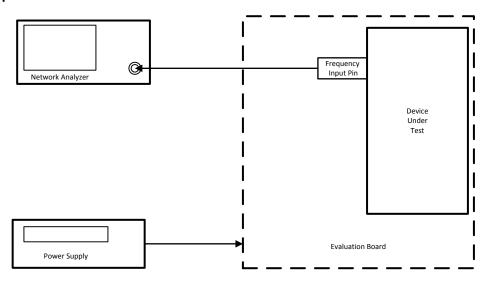

#### 7.1.4 Input Impedance Measurement

Figure 21. Input Impedance Measurement

Figure 21 shows the test set-up used for measuring the input impedance for the LMX2487E. The DC-blocking capacitor used between the input SMA connector and the pin being measured must be changed to a 0-Ω resistor. This procedure applies to the FinRF, FinIF, and OSCin pins. The basic test procedure is to calibrate the network analyzer, ensure that the part is powered up, and then measure the input impedance. The network analyzer can be calibrated by using either calibration standards or by soldering resistors directly to the evaluation board. An open can be implemented by putting no resistor, a short can be implemented by soldering a 0-Ω resistor as close as possible to the pin being measured, and a short can be implemented by soldering two 100-Ω resistors in parallel as close as possible to the pin being measured. Calibration is done with the PLL removed from the PCB. This requires the use of a clamp down fixture that may not always be generally available. If no clamp down fixture is available, then this procedure can be done by calibrating up to the point where the DCblocking capacitor usually is, and then implementing port extensions with the network analyzer. The  $0-\Omega$  resistor is added back for the actual measurement. Once the set-up is calibrated, it is necessary to ensure that the PLL is powered up. This can be done by toggling the power down bits (RF\_PD and IF\_PD) and observing that the current consumption indeed increases when the bit is disabled. Sometimes it may be necessary to apply a signal to the OSCin pin in order to program the part. If this is necessary, disconnect the signal once it is established that the part is powered up. It is useful to know the input impedance of the PLL for the purposes of debugging RF problems and designing matching networks. Another use of knowing this parameter is make the trace width on the PCB such that the input impedance of this trace matches the real part of the input impedance of the PLL frequency of operation. In general, it is good practice to keep trace lengths short and make designs that are relatively resistant to variations in the input impedance of the PLL.

## 8 Detailed Description

#### 8.1 Overview

The LMX2487E consists of integrated N counters, R counters, and charge pumps. The TCXO, VCO and loop filter are supplied external to the chip.

## 8.2 Functional Block Diagram

Figure 22. Block Diagram

#### 8.3 Feature Description

#### 8.3.1 TCXO, Oscillator Buffer, and R Counter

The oscillator buffer must be driven single-ended by a signal source, such as a TCXO. The OSCout pin is included to provide a buffered output of this input signal and is active when the OSC\_OUT bit is set to one. The ENOSC pin can be also pulled high to ensure that the OSCout pin is active, regardless of the status of the registers in the LMX2487E.

The R counter divides this TCXO frequency down to the comparison frequency.

#### 8.3.2 Phase Detector

The maximum phase detector operating frequency for the IF PLL is straightforward, but it is a little more involved for the RF PLL because it is fractional. The maximum phase detector frequency for the LMX2487E RF PLL is 50 MHz. However, this is not possible in all circumstances due to illegal divide ratios of the N counter. The crystal reference frequency also limits the phase detector frequency, although the doubler helps with this limitation. There are trade-offs in choosing the phase detector frequency. If this frequency is run higher, then phase noise will be lower, but lock time may be increased due to cycle slipping and the capacitors in the loop filter may become rather large.

#### 8.3.3 Charge Pump

For the majority of the time, the charge pump output is high impedance, and the only current through this pin is the Tri-State leakage. However, it does put out fast correction pulses that have a width that is proportional to the phase error presented at the phase detector.

## **Feature Description (continued)**

The charge pump converts the phase error presented at the phase detector into a correction current. The magnitude of this current is theoretically constant, but the duty cycle is proportional to the phase error. For the IF PLL, this current is not programmable, but for the RF PLL it is programmable in 16 steps. Also, the RF PLL allows for a higher charge pump current to be used when the PLL is locking in order to reduce the lock time.

#### 8.3.4 Loop Filter

The loop filter design can be rather involved. In addition to the regular constraints and design parameters, delta-sigma PLLs have the additional constraint that the order of the loop filter should be one greater than the order of the delta sigma modulator. This rule of thumb comes from the requirement that the loop filter must roll off the delta sigma noise at 20 dB/decade faster than it rises. However, because the noise can not have infinite power, it must eventually roll off. If the loop bandwidth is narrow, this requirement may not be necessary. For the purposes of discussion in this datasheet, the pole of the loop filter at 0 Hz is not counted. So a second order filter has 3 components, a 3rd order loop filter has 5 components, and the 4th order loop filter has 7 components. Although a 5th order loop filter is theoretically necessary for use with a 4th order modulator, typically a 4th order filter is used in this case. The loop filter design, especially for higher orders can be rather involved, but there are many simulation tools and references available, such as the one given at the end of the functional description block.

#### 8.3.5 N Counters and High Frequency Input Pins

The N counter divides the VCO frequency down to the comparison frequency. Because prescalers are used, there are limitations on how small the N value can be. Because the input pins to these counters (FinRF and FinIF) are high frequency, layout considerations are important.

#### 8.3.5.1 High Frequency Input Pins, FinRF and FinIF

It is generally recommended that the VCO output go through a resistive pad and then through a DC-blocking capacitor before it gets to these high frequency input pins. If the trace length is sufficiently short ( < 1/10th of a wavelength ), then the pad may not be necessary, but a series resistor of about 39  $\Omega$  is still recommended to isolate the PLL from the VCO. The DC-blocking capacitor should be chosen at least to be 27 pF. It may turn out that the frequency is above the self-resonant frequency of the capacitor, but because the input impedance of the PLL tends to be capacitive, it actually is a benefit to exceed the tune frequency. The pad and the DC-blocking capacitor should be placed as close to the PLL as possible

## 8.3.5.2 Complementary High Frequency Pin, FinRF\*

These inputs may be used to drive the PLL differentially, but it is very common to drive the PLL in a single ended fashion. A shunt capacitor should be placed at the FinRF\* pin. The value of this capacitor should be chosen such that the impedance, including the ESR of the capacitor, is as close to an AC short as possible at the operating frequency of the PLL. 100 pF is a typical value.

## **Feature Description (continued)**

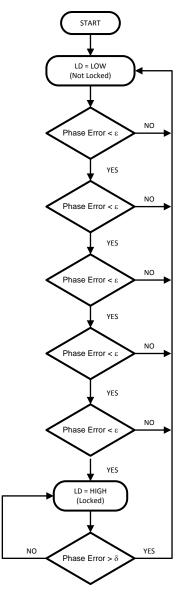

#### 8.3.6 Digital Lock Detect Operation

The RF PLL digital lock detect circuitry compares the difference between the phase of the inputs of the phase detector to a RC-generated delay of  $\epsilon$ . To indicate a locked state (Lock = HIGH) the phase error must be less than the  $\epsilon$  RC delay for 5 consecutive reference cycles. Once in lock (Lock = HIGH), the RC delay is changed to approximately  $\delta$ . To indicate an out of lock state (Lock = LOW), the phase error must become greater  $\delta$ . The values of  $\epsilon$  and  $\delta$  are dependent on which PLL is used and are shown in the table below:

**Table 6. Digital Lock Detect Settings**

| PLL | 3     | δ     |

|-----|-------|-------|

| RF  | 10 ns | 20 ns |

| IF  | 15 ns | 30 ns |

When the PLL is in the power-down mode and the Ftest/LD pin is programmed for the lock detect function, it is forced LOW. The accuracy of this circuit degrades at higher comparison frequencies. To compensate for this, the DIV4 word should be set to one if the comparison frequency exceeds 20 MHz. The function of this word is to divide the comparison frequency presented to the lock detect circuit by 4.

#### **NOTE**

If the MUX[3:0] word is set such as to view lock detect for both PLLs, an unlocked (LOW) condition is shown whenever either one of the PLLs is determined to be out of lock.

Figure 23. Digital Lock Detect Flowchart

#### 8.3.7 Cycle Slip Reduction and Fastlock

The LMX2487E offers both cycle slip reduction (CSR) and Fastlock with timeout counter support. This means that it requires no additional programming overhead to use them. It is generally recommended that the charge pump current in the steady-state be 8X or less in order to use cycle slip reduction, and 4X or less in steady-state in order to use Fastlock. The next step is to decide between using Fastlock or CSR. This determination can be made based on the ratio of the comparison frequency (f<sub>COMP</sub>) to loop bandwidth (BW).

Table 7. Cycle Slip Reduction and Fastlock

| COMPARISON FREQUENCY<br>(f <sub>COMP</sub> ) | FASTLOCK                   | CYCLE SLIP REDUCTION ( CSR )               |

|----------------------------------------------|----------------------------|--------------------------------------------|

| f <sub>COMP</sub> ≤ 1.25 MHz                 | Noticeable better than CSR | Likely to provide a benefit, provided that |

| 1.25 MHz < f <sub>COMP</sub> ≤ 2 MHz         | Marginally better than CSR | f <sub>COMP</sub> > 100 X BW               |

| f <sub>COMP</sub> > 2 MHz                    | Same or worse than CSR     |                                            |

#### 8.3.7.1 Cycle Slip Reduction (CSR)

Cycle slip reduction works by reducing the comparison frequency during frequency acquisition while keeping the same loop bandwidth, thereby reducing the ratio of the comparison frequency to the loop bandwidth. In cases where the ratio of the comparison frequency exceeds about 100 times the loop bandwidth, cycle slipping can occur and significantly degrade lock times. The greater this ratio, the greater the benefit of CSR. This is typically the case of high comparison frequencies. In circumstances where there is not a problem with cycle slipping, CSR provides no benefit. There is a glitch when CSR is disengaged, but because CSR should be disengaged long before the PLL is actually in lock, this glitch is not an issue. A good rule of thumb for CSR disengagement is to do this at the peak time of the transient response. Because this time is typically much sooner than Fastlock should be disengaged, it does not make sense to use CSR and Fastlock in combination.

#### 8.3.7.2 Fastlock

Fastlock works by increasing the loop bandwidth only during frequency acquisition. In circumstances where the comparison frequency is less than or equal to 2 MHz, Fastlock may provide a benefit beyond what CSR can offer. Because Fastlock also reduces the ratio of the comparison frequency to the loop bandwidth, it may provide a significant benefit in cases where the comparison frequency is above 2 MHz. However, CSR can usually provide an equal or larger benefit in these cases, and can be implemented without using an additional resistor. The reason for this restriction on frequency is that Fastlock has a glitch when it is disengaged. As the time of engagement for Fastlock decreases and becomes on the order of the fast lock time, this glitch grows and limits the benefits of Fastlock. This effect becomes worse at higher comparison frequencies. There is always the option of reducing the comparison frequency at the expense of phase noise in order to satisfy this constraint on comparison frequency. Despite this glitch, there is still a net improvement in lock time using Fastlock in these circumstances. When using Fastlock, it is also recommended that the steady-state charge pump state be 4X or less. Also, Fastlock was originally intended only for second order filters, so when implementing it with higher order filters, the third and fourth poles can not be too close in, or it will not be possible to keep the loop filter well optimized when the higher charge pump current and Fastlock resistor are engaged.

#### 8.3.7.3 Using Cycle Slip Reduction (CSR) to Avoid Cycle Slipping

Once it is decided that CSR is to be used, the cycle slip reduction factor needs to be chosen. The available factors are 1/2, 1/4, and 1/16. In order to preserve the same loop characteristics, TI recommends that Equation 4 be satisfied:

In order to satisfy this constraint, the maximum charge pump current in steady-state is 8X for a CSR of 1/2, 4X for a CSR of 1/4, and 1X for a CSR of 1/16. Because the PLL phase noise is better for higher charge pump currents, it makes sense to choose CSR only as large as necessary to prevent cycle slipping. Choosing it larger than this will not improve lock time, and will result in worse phase noise.

Consider an example where the desired loop bandwidth in steady-state is 100 kHz and the comparison frequency is 20 MHz. This yields a ratio of 200. Cycle slipping may be present, but would not be too severe if it was there. If a CSR factor of 1/2 is used, this would reduce the ratio to 100 during frequency acquisition, which is probably sufficient. A charge pump current of 8X could be used in steady-state, and a factor of 16X could be used during frequency acquisition. This yields a ratio of 1/2, which is equal to the CSR factor and this satisfies the above constraint. In this circumstance, it could also be decided to just use 16X charge pump current all the time, because it would probably have better phase noise, and the degradation in lock time would not be too severe.

## 8.3.7.4 Using Fastlock to Improve Lock Times

Figure 24. Loop Filter with Fastlock Resistor

Once it is decided that Fastlock is to be used, the loop bandwidth multiplier, K, is needed in order to determine the theoretical impact of Fastlock on the loop bandwidth and the resistor value, R2p, that is switched in parallel during Fastlock. This ratio is calculated in Equation 5:

K = ( Fastlock Charge Pump Current ) / ( Steady-State Charge Pump Current )

(5)

Table 8. Fastlock Usage

| К  | LOOP BANDWIDTH | R2P VALUE | LOCK TIME |

|----|----------------|-----------|-----------|

| 1  | 1.00 X         | Open      | 100%      |

| 2  | 1.41 X         | R2/0.41   | 71%       |

| 3  | 1.73 X         | R2/0.73   | 58%       |

| 4  | 2.00 X         | R2        | 50%       |

| 8  | 2.83 X         | R2/1.83   | 35%       |

| 9  | 3.00 X         | R2/2      | 33%       |

| 16 | 4.00 X         | R2/3      | 25%       |

The above table shows how to calculate the fastlock resistor and theoretical lock time improvement, once the ratio, K, is known. This all assumes a second order filter (not counting the pole at 0 Hz). However, it is generally recommended that the loop filter order be one greater than the order of the delta sigma modulator, which means that a second order filter is never recommended. In this case, the value for R2p is typically about 80% of what it would be for a second order filter. Because the fastlock disengagement glitch gets larger and it is harder to keep the loop filter optimized as the K value becomes larger, designing for the largest possible value for K usually, but not always yields the best improvement in lock time. To get a more accurate estimate requires more simulation tools, or trial and error.

## 8.3.7.5 Capacitor Dielectric Considerations for Lock Time

The LMX2487E has a high fractional modulus and high charge pump gain for the lowest possible phase noise. One consideration is that the reduced N value and higher charge pump may cause the capacitors in the loop filter to become larger in value. For larger capacitor values, it is common to have a trade-off between capacitor dielectric quality and physical size. Using film capacitors or NPO/COG capacitors yields the best possible lock times, where as using X7R or Z5R capacitors can increase lock time by 0-500%. However, it is a general tendency that designs that use a higher compare frequency tend to be less sensitive to the effects of capacitor dielectrics. Although the use of lesser quality dielectric capacitors may be unavoidable in many circumstances, allowing a larger footprint for the loop filter capacitors, using a lower charge pump current, and reducing the fractional modulus are all ways to reduce capacitor values. Capacitor dielectrics have very little impact on phase noise and spurs.

#### 8.3.8 Fractional Spur and Phase Noise Controls

Control of the fractional spurs is more of an art than an exact science. The first differentiation that needs to be made is between primary fractional and sub-fractional spurs. The primary fractional spurs are those that occur at increments of the channel spacing only. The sub-fractional spurs are those that occur at a smaller resolution than the channel spacing, usually one-half or one-fourth. There are trade-offs between fractional spurs, sub-fractional spurs, and phase noise. The rules of thumb presented in this section are just that. There will be exceptions. The bits that impact the fractional spurs are FM and DITH, and these bits should be set in this order.

The first step to do is choose FM, for the delta sigma modulator order. TI recommends to start with FM = 3 for a third order modulator and use strong dithering. In general, there is a trade-off between primary and sub-fractional spurs. Choosing the highest order modulator (FM = 0 for 4th order) typically provides the best primary fractional spurs, but the worst sub-fractional spurs. Choosing the lowest modulator order (FM = 2 for 2nd order), typically gives the worst primary fractional spurs, but the best sub-fractional spurs. Choosing FM = 3, for a 3rd order modulator is a compromise.

The second step is to choose DITH, for dithering. Dithering has a very small impact on primary fractional spurs, but a much larger impact on sub-fractional spurs. The only problem is that it can add a few dB of phase noise, or even more if the loop bandwidth is very wide. Disabling dithering (DITH = 0), provides the best phase noise, but the sub-fractional spurs are worst (except when the fractional numerator is 0, and in this case, they are the best). Choosing strong dithering (DITH = 2) significantly reduces sub-fractional spurs, if not eliminating them completely, but adds the most phase noise. Weak dithering (DITH = 1) is a compromise.

The third step is to tinker with the fractional word. Although 1/10 and 400/4000 are mathematically the same, expressing fractions with much larger fractional numerators often improve the fractional spurs. Increasing the fractional denominator only improves spurs to a point. A good practical limit could be to keep the fractional denominator as large as possible, but not to exceed 4095, so it is not necessary to use the extended fractional numerator or denominator.

#### NOTE

For more information concerning delta-sigma PLLs, loop filter design, cycle slip reduction, Fastlock, and many other topics, visit <a href="http://www.ti.com">http://www.ti.com</a>. Here there is the EasyPLL simulation tool and an online reference called *PLL Performance*, *Simulation*, and *Design*.

#### 8.4 Device Functional Modes

## 8.4.1 Power Pins, Power-Down, and Power-Up Modes

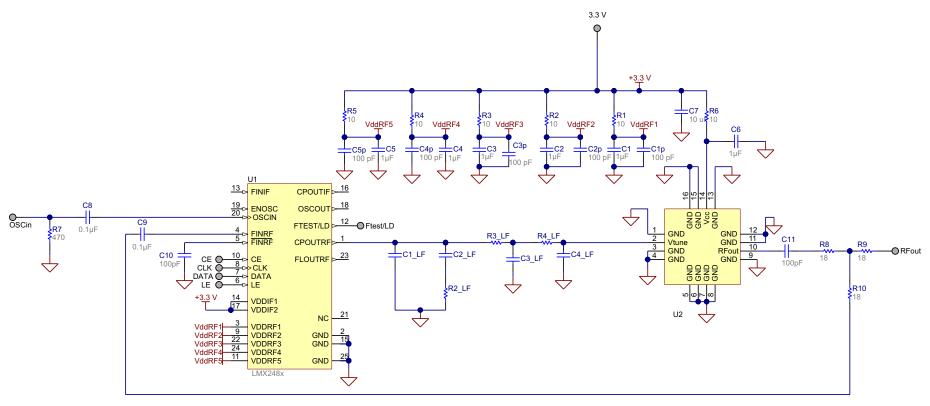

TI recommends that all of the power pins be filtered with a series  $18-\Omega$  resistor and then placing two capacitors shunt to ground, thus creating a low pass filter. Although it makes sense to use large capacitor values in theory, the ESR ( Equivalent Series Resistance ) is greater for larger capacitors. For optimal filtering minimize the sum of the ESR and theoretical impedance of the capacitor. It is therefore recommended to provide two capacitors of very different sizes for the best filtering. 1  $\mu$ F and 100 pF are typical values. The small capacitor should be placed as close as possible to the pin.

The power down state of the LMX2487E is controlled by many factors. The one factor that overrides all other factors is the CE pin. If this pin is low, the part will be powered down. Asserting a high logic level on this pin is necessary to power up the chip, however, there are other bits in the programming registers that can override this and put the PLL back in a power down state. Provided that the voltage on the CE pin is high, programming the RF\_PD and IF\_PD bits to zero ensures that the part will be powered up. Programming either one of these bits to one will power down the appropriate section of the synthesizer, provided that the ATPU bit does not override this.

**Table 9. Device Powerdown Programming**

| CE PIN | RF_PD | ATPU<br>BIT ENABLED +<br>WRITE TO RF<br>N COUNTER | PLL STATE                     |

|--------|-------|---------------------------------------------------|-------------------------------|

| Low    | X     | X                                                 | Powered Down (Asynchronous)   |

| High   | X     | Yes                                               | Powered Up                    |

| High   | 0     | No                                                | Powered Up                    |

| High   | 1     | No                                                | Powered Down ( Asynchronous ) |

#### 8.5 Programming

## 8.5.1 General Programming Information

The 24-bit data registers are loaded through a MICROWIRE Interface. These data registers are used to program the R counter, the N counter, and the internal mode control latches. The data format of a typical 24-bit data register is shown below. The control bits CTL [3:0] decode the register address. On the rising edge of LE, data stored in the shift register is loaded into one of the appropriate latches (selected by address bits). Data is shifted in MSB first.

#### **NOTE**

It is best to program the N counter last, because doing so initializes the digital lock detector and Fastlock circuitry. *Initialize* means it resets the counters, but it does NOT program values into these registers. The exception is when 22-bit is not being used. In this case, it is not necessary to program the R7 register.

Table 10. Register Structure

| MSB  |        |   |           |   |   | LSB |

|------|--------|---|-----------|---|---|-----|

| DATA | [21:0] |   | CTL [3:0] |   |   |     |

| 23   | 4      | 3 |           | 2 | 1 | 0   |

## 8.5.1.1 Register Location Truth Table

The control bits CTL [3:0] decode the internal register address. The table below shows how the control bits are mapped to the target control register.

**DATA Location** C3 C2 C1 C<sub>0</sub> 0 R0 Х Х 0 0 1 1 R1 0 1 0 1 R2 0 1 1 1 R3 1 0 0 1 R4 0 1 1 1 R5 1 1 0 1 R6 1 1 1 1 R7

**Table 11. Programmable Registers**

## 8.5.1.2 Control Register Content Map

Because the LMX2487E registers are complicated, they are organized into two groups, basic and advanced. The first four registers are basic registers that contain critical information necessary for the PLL to achieve lock. The last 5 registers are for features that optimize spur, phase noise, and lock time performance. The next page shows these registers.

Although it is highly recommended that the user eventually take advantage of all the modes of the LMX2487E, the quick start register map is shown in order for the user to get the part up and running quickly using only those bits critical for basic functionality. The following default conditions for this programming state are a third order delta-sigma modulator in 12-bit mode with no dithering and no Fastlock.

## Table 12. Quick Start Register Map

| REG | 23        | 22                     | 21 | 20 | 19 | 18    | 17      | 16      | 15                                        | 14        | 13     | 12      | 11      | 10        | 9     | 8 | 7 | 6 | 5 | 4 | 3  | 2  | 1  | 0  |

|-----|-----------|------------------------|----|----|----|-------|---------|---------|-------------------------------------------|-----------|--------|---------|---------|-----------|-------|---|---|---|---|---|----|----|----|----|

|     |           |                        |    |    |    |       | DA      | TA[19:0 | ] ( Exce                                  | ept for t | he RF_ | N Regis | ter, wh | ich is [2 | 2:0]) |   |   |   |   |   | СЗ | C2 | C1 | C0 |

| R0  |           | RF_N[10:0] RF_FN[11:0] |    |    |    |       |         |         |                                           |           |        |         |         |           |       |   | 0 |   |   |   |    |    |    |    |

| R1  | RF_<br>PD | RF P                   |    |    |    |       |         |         |                                           |           |        |         |         |           | 0     | 1 | 1 |   |   |   |    |    |    |    |

| R2  | IF_<br>PD |                        |    |    |    |       |         |         |                                           |           | IF_N   | N[18:0] |         |           |       |   |   |   |   |   | 0  | 1  | 0  | 1  |

| R3  |           | 000                    | )1 |    |    | RF_CF | PG[3:0] |         | IF_R[11:0] 0 1                            |           |        |         |         |           |       |   |   |   |   |   | 1  | 1  |    |    |

| R4  | 0         | 0                      | 1  | 0  | 0  | 0     | 0       | 0       | )   1   1   0   0   0   1   1   1   0   0 |           |        |         |         |           |       |   |   |   | 0 | 1 |    |    |    |    |

The complete register map shows all the functionality of all registers, including the last five.

## Table 13. Complete Register Map

| REG | 23           | 22       | 21    | 20   | 19      | 18      | 17              | 16        | 15                | 14  | 13      | 12             | 11         | 10         | 9          | 8    | 7          | 6          | 5          | 4          | 3  | 2  | 1  | 0  |

|-----|--------------|----------|-------|------|---------|---------|-----------------|-----------|-------------------|-----|---------|----------------|------------|------------|------------|------|------------|------------|------------|------------|----|----|----|----|

|     |              |          |       |      |         |         |                 |           | -                 |     | he RF_N |                |            | -          | ])         |      | -          |            |            |            | C3 | C2 | C1 | CO |

| R0  |              |          |       |      |         | RF_I    | N[10:0]         |           | RF_FN[11:0]       |     |         |                |            |            |            |      |            |            |            |            |    | 0  |    |    |

| R1  | RF_<br>PD    | RF<br>_P |       |      | RF_     | _R[5:0] |                 |           | RF_FD[11:0] 0 0 1 |     |         |                |            |            |            |      |            |            | 1          | 1          |    |    |    |    |

| R2  | IF_P<br>D    |          |       |      |         |         |                 |           |                   |     | IF_N[   | 18:0]          |            |            |            |      |            |            |            |            | 0  | 1  | 0  | 1  |

| R3  | A            | CCES     | S[3:0 | ]    |         | RF_C    | PG[3:0]         |           |                   |     |         | IF_R[11:0]     |            |            |            |      |            |            | 0          | 1          | 1  | 1  |    |    |

| R4  | ATP<br>U     | 0        | 1     | 0    | 0       | 0       | DI <sup>*</sup> | TH<br>:0] | F<br>[1           |     | 0       | OSC<br>-<br>2X | OSC<br>OUT | IF_<br>CPP | RF_<br>CPP | IF_P |            |            | JX<br>:0]  |            | 1  | 0  | 0  | 1  |

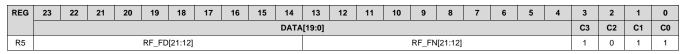

| R5  | RF_FD[21:12] |          |       |      |         | 1       |                 |           |                   |     |         |                |            |            |            |      |            |            |            |            |    |    |    |    |

| R6  | CSR          | 1:0]     |       | RF_C | PF[3:0] |         |                 |           |                   |     |         | ı              | RF_TO      | C[13:0]    |            |      |            |            |            |            | 1  | 1  | 0  | 1  |

| R7  | 0            | 0        | 0     | 0    | 0       | 0       | 0               | 0         | 0                 | 0 0 |         | 0              | 1          | 0          | 0          | 1    | IF_<br>RST | RF_<br>RST | IF_<br>CPT | RF_<br>CPT | 1  | 1  | 1  | 1  |

## 8.6 Register Maps

## 8.6.1 R0 Register

#### **NOTE**

This register has only one control bit, so the N counter value to be changed with a single write statement to the PLL.

#### Table 14. R0 REGISTER

| REGISTER | 23         | 22         | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7     | 6      | 5  | 4 | 3 | 2 | 1 | 0 |

|----------|------------|------------|----|----|----|----|----|----|----|----|----|----|----|----|---|---|-------|--------|----|---|---|---|---|---|

|          |            | DATA[22:0] |    |    |    |    |    |    |    |    |    |    |    |    |   |   | C0    |        |    |   |   |   |   |   |

| R0       | RF_N[10:0] |            |    |    |    |    |    |    |    |    |    |    |    |    |   | F | RF_FI | N[11:0 | 0] |   |   |   |   | 0 |

### 8.6.1.1 RF\_FN[11:0] - Fractional Numerator for RF PLL

Refer to *Fractional Numerator Determination* { *RF\_FN[21:12], RF\_FN[11:0], Access[1]* } for a more detailed description of this control word.

### 8.6.1.2 RF\_N[10:0] - RF N Counter Value

The RF N counter contains an 16/17/20/21 and a 32/33/36/37 prescaler. The N counter value can be calculated in Equation 6:

$$N = RF_P \times RF_C + 4 \times RF_B + RF_A \tag{6}$$

RF\_C  $\geq$ Max{RF\_A, RF\_B}, for N-2<sup>FM</sup>-1 ... N+2<sup>FM</sup> is a necessary condition. This rule is slightly modified in the case where the RF\_B counter has an unused bit, where this extra bit is used by the delta-sigma modulator for the purposes of modulation. Consult Table 15 and Table 16 for valid operating ranges for each prescaler.

Table 15. Operation with the 16/17/20/21 Prescaler (RF\_P=0)

| RF_N  |   |   |      |       |                    | RF_N [10:0                                              | )]                     |           |   |      |       |

|-------|---|---|------|-------|--------------------|---------------------------------------------------------|------------------------|-----------|---|------|-------|

| KF_IN |   |   | RF_C | [5:0] |                    |                                                         |                        | RF_B [2:0 | ] | RF_A | [1:0] |

| <49   |   |   |      |       | N Values           | Below 49                                                | are Illegal.           |           |   |      |       |

| 49-63 |   |   |      |       | 2nd Ord<br>3rd Ord | Divide Rati<br>ler Modulat<br>er Modulat<br>rder Modula | or: 49-61<br>or: 51-59 |           |   |      |       |

| 64-79 |   |   |      |       | 2nd and 3          | Divide Rati<br>rd Order Mo<br>er Modulato               | odulator: All          | I         |   |      |       |

| 80    | 0 | 0 | 0    | 1     | 0                  | 1                                                       | 0                      | 0         | 0 | 0    | 0     |

|       |   |   |      |       |                    |                                                         | 0                      |           |   |      |       |

| 1023  | 1 | 1 | 1    | 1     | 1                  | 1                                                       | 0                      | 1         | 1 | 1    | 1     |

| >1023 |   |   |      | N     | l values ab        | ove 1023 a                                              | re prohibite           | d.        |   |      | •     |

Table 16. Operation with the 32/33/36/37 Prescaler (RF\_P=1)

| DE N    |   |   |                                                                                                                                                                                                              |       | ı           | RF_N [10:0                                 | ]            |            |   |      |       |  |  |  |

|---------|---|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------|--------------------------------------------|--------------|------------|---|------|-------|--|--|--|

| RF_N    |   |   | RF_C                                                                                                                                                                                                         | [5:0] |             |                                            |              | RF_B [2:0] |   | RF_A | [1:0] |  |  |  |

| <97     |   |   |                                                                                                                                                                                                              | ΝV    | alues Belov | v 97 are Ille                              | egal.        |            |   |      |       |  |  |  |

| 97-226  |   |   | Legal Divide Ratios are:<br>2nd Order Modulator: 97-109, 129-145, 161-181, 193-217, 225-226<br>3rd Order Modulator: 99-107, 131-143, 163-179, 195-215<br>4th Order Modulator: 103, 135-139, 167-175, 199-211 |       |             |                                            |              |            |   |      |       |  |  |  |

| 227–230 |   |   |                                                                                                                                                                                                              |       | 2nd and 3r  | Divide Ration<br>d Order Mo<br>er Modulato | dulator: All |            |   |      |       |  |  |  |

| 231     | 0 | 0 | 0                                                                                                                                                                                                            | 1     | 1           | 1                                          | 0            | 0          | 1 | 1    | 1     |  |  |  |

## Table 16. Operation with the 32/33/36/37 Prescaler (RF\_P=1) (continued)

| DE N      |   |   |      |              | ı             | RF_N [10:0  | )]           |            |    |      |         |

|-----------|---|---|------|--------------|---------------|-------------|--------------|------------|----|------|---------|

| RF_N      |   |   | RF_C | [5:0]        |               |             |              | RF_B [2:0] |    | RF_A | \ [1:0] |

|           |   |   |      |              |               |             |              |            |    |      |         |

| 2039      | 1 | 1 | 1    | 1            | 1             | 1           | 1            | 0          | 1  | 1    | 1       |