# **Microwire**

# **2K Bits**

# Serial EEPROM

Copyright © 2011 Giantec Semiconductor Inc. (Giantec). All rights reserved. Giantec reserves the right to make changes to this specification and its products at any time without notice. Giantec products are not designed, intended, authorized or warranted for use as components in systems or equipment intended for critical medical or surgical equipment, aerospace or military, or other applications planned to support or sustain life. It is the customer's obligation to optimize the design in their own products for the best performance and optimization on the functionality and etc. Giantec assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and prior placing orders for products.

### **Table of Contents**

| 1. | . Features                       | 3  |

|----|----------------------------------|----|

| 2. | . General Description            | 3  |

| 3. | . Functional Block Diagram       | 2  |

| 4. | . Pin Configuration              | 5  |

|    | 4.1 8-Pin SOIC and TSSOP         | 5  |

|    | 4.2 Pin Definition               | 5  |

| 5. | . Device Operation               | 6  |

|    | 5.1 Read                         | 6  |

|    | 5.2 Write Enable                 | 6  |

|    | 5.3 Write Disable                | 6  |

|    | 5.4 Write                        | 6  |

|    | 5.5 Write All Memory             | 6  |

|    | 5.6 Erase                        | 6  |

|    | 5.7 Erase All Memory             | 7  |

|    | 5.8 Power-On Reset               | 7  |

|    | 5.9 Instruction Set              | 7  |

|    | 5.10 Diagrams                    | 8  |

| 6. | . Electrical Characteristics     | 11 |

|    | 6.1 Absolute Maximum Ratings     | 11 |

|    | 6.2 Operating Range              | 11 |

|    | 6.3 Capacitance                  | 11 |

|    | 6.4 DC Electrical Characteristic | 12 |

|    | 6.5 AC Electrical Characteristic | 13 |

| 7. | . Ordering Information           | 14 |

| 8. | . Top Markings                   | 15 |

|    | 8.1 SOIC Package                 | 15 |

|    | 8.2 TSSOP Package                | 15 |

| 9. | Package Information              | 16 |

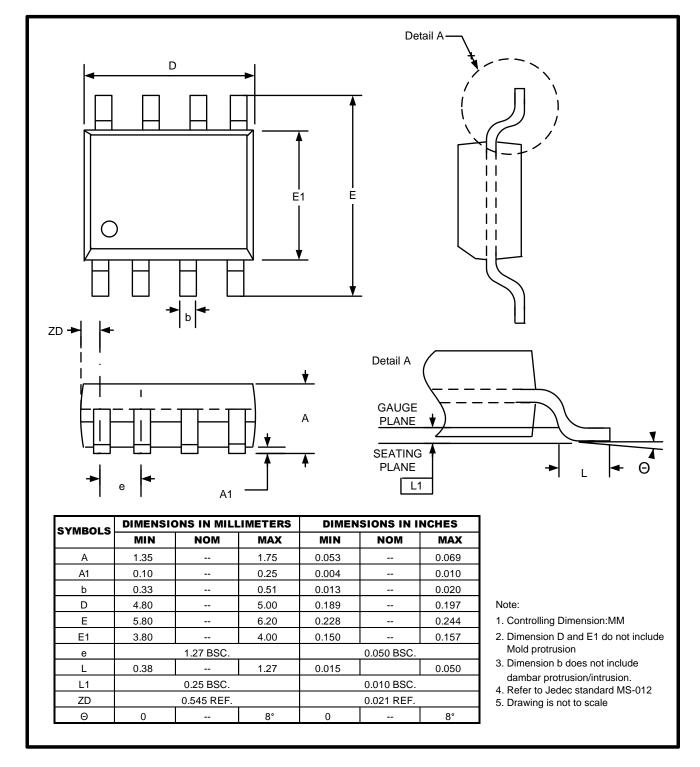

|    | 9.1 SOIC                         | 16 |

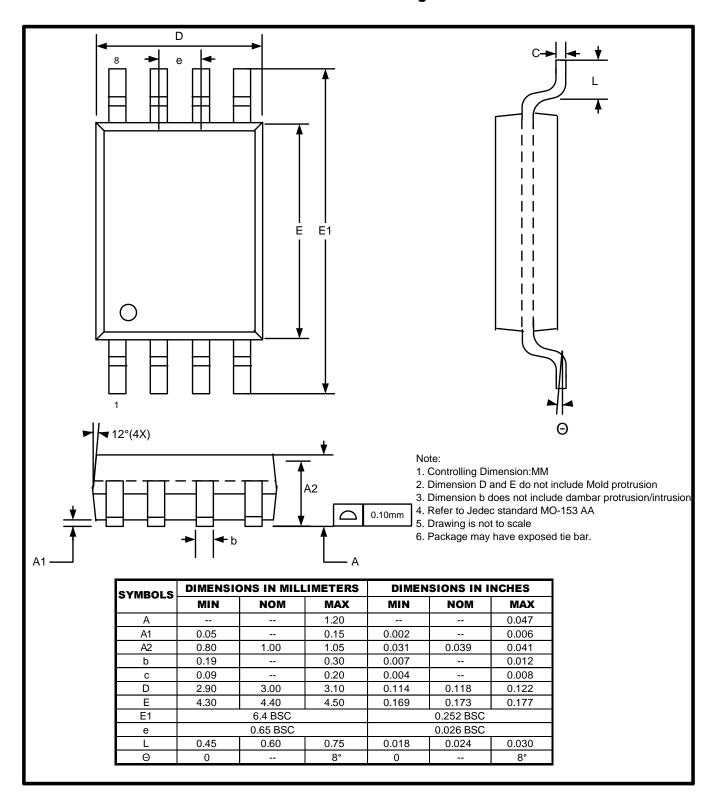

|    | 9.2 TSSOP                        | 17 |

| 10 | 0. Revision History              | 18 |

#### 1. Features

- Industry-standard Microwire Interface

- Wide-voltage Operation

- V<sub>CC</sub> = 1.8V to 5.5V

- Speed

- 1 MHz (1.8V), 2 MHz (2.5V), 3 MHz (5.5V)

- Standby current

- 1uA (max.) 1.8V

- Operating current

- 1mA (max.) 1.8V

- **User Configured Memory Organization**

- 128x16-bit (ORG =  $V_{CC}$  or Floating)

- or 256x8-bit (ORG = 0V)

- Self timed write cycle: 5 ms (max.)

- Hardware and software write protection

- Defaults to write-disabled state at power-up

- Software instructions for write-enable/disable

- CMOS technology

- Versatile, easy-to-use interface

- Automatic erase-before-write

- Programming status indicator

- Byte, Word and chip single erasable

- Chip select enables power savings

- Noise immunity on inputs, besides Schmitt trigger

- High-reliability

- Endurance: 1 million cycles

- Data retention: 100 years

- Packages: SOIC and TSSOP

- Lead-free, RoHS, Halogen free, Green

### 2. General Description

The GT93C56A is 2kb non-volatile serial EEPROM with memory array of 2,048 bits. The array can be organized as either 256 bytes of 8 bits or 128 words of 16 bits via the ORG control. Utilizing the CMOS design and process, these products provide low standby current and low power operations. The devices can operate in a wide supply voltage range from 1.8V to 5.5V, with frequency up to 3MHz.

When the ORG pin is connected to V<sub>CC</sub> or floating, x16 is selected. Conversely, when it is connected to ground, x8 is

An instruction Op-code defines the various operations of

the devices, including read, write, and mode-enable functions. To protect against inadvertent data modification, all write and erase instructions are merely accepted while the device is in write enable mode. A selected x8 byte or x16 word can be modified with a single WRITE or ERASE instruction. Additionally, the WRITE ALL or ERASE ALL instruction can program or erase the entire array, respectively. Once a device begins its self-timed program procedure, the data out pin (DOUT) can indicate the READY/BUSY status by raising chip select (CS). The devices can output any number of consecutive bytes/words using a single READ instruction.

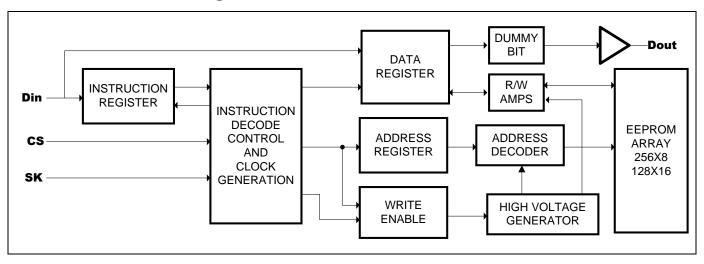

### 3. Functional Block Diagram

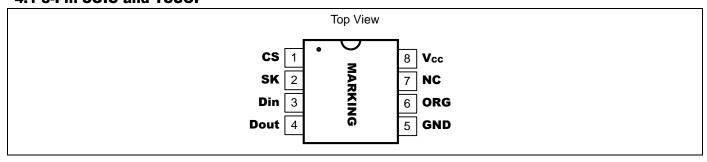

### 4. Pin Configuration

### 4.1 8-Pin SOIC and TSSOP

#### 4.2 Pin Definition

| Pin No. | Pin Name         | I/O              | Definition          |

|---------|------------------|------------------|---------------------|

| 1       | CS               | I                | Chip Select         |

| 2       | SK               | I                | Serial Data Clock   |

| 3       | D <sub>IN</sub>  | I                | Serial Data Input   |

| 4       | D <sub>OUT</sub> | 0                | Serial Data Output  |

| 5       | GND              | - Ground         |                     |

| 6       | ORG              | I                | Organization Select |

| 7       | NC               | -                | Not Connect         |

| 8       | Vcc              | - Supply Voltage |                     |

### 5. Device Operation

The GT93C56A is controlled by a set of instructions which are clocked-in serially on the  $D_{IN}$  pin. Before each low-to-high transition of the clock (SK), the CS pin must have already been raised to HIGH, and the  $D_{IN}$  value must be stable at either LOW or HIGH. Each instruction begins with a start bit of the logical "1" or HIGH. Following this are the Op-code, address field, and data, if appropriate. The clock signal may be held stable at any moment to suspend the device at its last state, allowing clock speed flexibility. Upon completion of bus communication, CS would be pulled LOW. The device then would enter Standby mode if no internal programming is underway.

#### 5.1 Read

The READ instruction is the only instruction that outputs serial data on the  $D_{OUT}$  pin. After the read instruction and address have been decoded, data is transferred from the selected memory array into a serial shift register. (Please note that one logical "0" bit precedes the actual 8 or 16-bit output data string.) The output on  $D_{OUT}$  changes during the low-to-high transitions of SK (see Figure 5.10-2).

The GT93C56A is designed to output a continuous stream of memory content in response to a single read operation instruction. To utilize this function, the system asserts a read instruction specifying a start location address. Once the 8 or 16 bits of the addressed register have been clocked out, the data in consecutively higher address locations is output. The address will wrap around continuously with CS HIGH until the chip select (CS) control pin is brought LOW. This allows for single instruction data dumps to be executed with a minimum of firmware overhead.

#### 5.2 Write Enable

The write enable (WEN) instruction must be executed before any device programming (WRITE, WRALL, ERASE, and ERAL) can be done. When  $V_{CC}$  is applied, this device powers up in the write disabled state. The device then remains in a write disabled state until a WEN instruction is executed. Thereafter, the device remains enabled until a WDS instruction is executed or until  $V_{CC}$  is removed. (See Figure 5.10-3) (Note: Chip select must remain LOW until

V<sub>CC</sub> reaches its operational value.)

#### **5.3 Write Disable**

The write disable (WDS) instruction disables all programming capabilities. This protects the entire device against accidental modification of data until a WEN instruction is executed. (When  $V_{\text{CC}}$  is applied, this part powers up in the write disabled state.) To protect data, a WDS instruction should be executed upon completion of each programming operation.

#### 5.4 Write

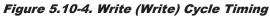

The WRITE instruction writes 8 or 16 bits of data into the specified memory location. After the last data bit has been applied to D<sub>IN</sub>, and before the next rising edge of SK, CS must be brought LOW. If the device is write-enabled, then the falling edge of CS initiates the self-timed programming cycle (see WEN). If CS is brought HIGH, after a minimum wait of 200 ns after the falling edge of CS (T<sub>CS</sub>) D<sub>OUT</sub> will indicate the READY/BUSY status of the chip. Logical "0" means programming is still in progress; logical "1" means the selected memory array has been written, and the part is ready for another instruction (see Figure 5.10-4). The READY/BUSY status will not be available if the CS input goes HIGH after the end of the self-timed programming cycle (Twp).

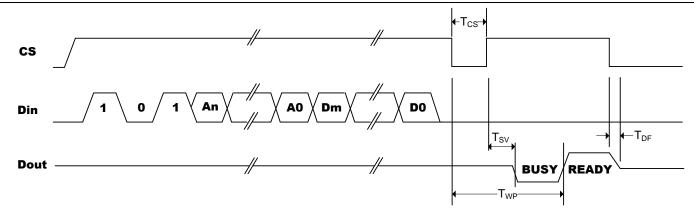

#### 5.5 Write All Memory

The write all (WRALL) instruction programs entire memory with the data pattern specified in the instruction. As with the WRITE instruction, the falling edge of CS must occur to initiate the self-timed programming cycle. If CS is then brought HIGH after a minimum wait of 200 ns ( $T_{CS}$ ), the  $D_{OUT}$  pin indicates the READY/BUSY status of the chip (see Figure 5.10-5).

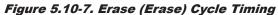

#### 5.6 Erase

After the erase instruction is entered, CS must be brought LOW. The falling edge of CS initiates the self-timed internal programming cycle. Bringing CS HIGH after a minimum of  $T_{CS}$ , will cause  $D_{OUT}$  to indicate the READ/BUSY status of the chip: a logical "0" indicates programming is still in progress; a logical "1" indicates the erase cycle is complete

and the part is ready for another instruction (see Figure 5.10-7).

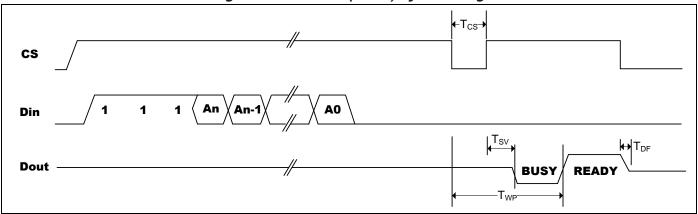

#### 5.7 Erase All Memory

Full chip erase (ERAL) is provided for ease of programming. Erasing the entire chip involves setting all bits in the entire memory array to a logical "1" (see Figure 5.10-8).

#### 5.8 Power-On Reset

The device incorporates a Power-On Reset (POR) circuitry which protects the internal logic against powering up into a wrong state. The device will power up into Standby mode after  $V_{\rm CC}$  exceeds the POR trigger level and will power down into Reset mode when  $V_{\rm CC}$  drops below the POR trigger level. This POR feature protects the device being 'brown-out' due to a sudden power loss or power cycling.

In order to refrain the state machine entering into a wrong state during power-up sequence or a power toggle off-on condition, a power on reset (POR) circuit is embedded. During power-up, the device does not respond to any instruction until  $V_{CC}$  has reached a minimum stable level above the reset threshold voltage. Once  $V_{CC}$  passes the POR threshold, the device is reset and enters in Standby mode. This can also avoid any inadvertent Write operations during power-up stage. During power-down process, the device must enter into standby mode, once  $V_{CC}$  drops below the power on reset threshold voltage. In addition, the device will enter standby mode after current operation completes, provided that no internal write operation is in progress.

#### **5.9 Instruction Set**

|                            | 944          |            | 8-bit Organization<br>(ORG = GND)  |                                   |                             | 16-bit Organization<br>(ORG = Vcc or Floating) |                                    |                             |  |

|----------------------------|--------------|------------|------------------------------------|-----------------------------------|-----------------------------|------------------------------------------------|------------------------------------|-----------------------------|--|

| Instruction <sup>[2]</sup> | Start<br>Bit | OP<br>Code | Address[1]                         | Data <sup>[1]</sup>               | Required<br>Clock<br>Cycles | Address <sup>[1]</sup>                         | Data <sup>[1]</sup>                | Required<br>Clock<br>Cycles |  |

| WDS (Write Disable)        | 1            | 00         | 0 0xxx xxxx                        | _                                 | 12                          | 00xx xxxx                                      | _                                  | 11                          |  |

| WEN (Write Enable)         | 1            | 00         | 1 1xxx xxxx                        | _                                 | 12                          | 11xx xxxx                                      | _                                  | 11                          |  |

| ERAL (Erase All Memory)    | 1            | 00         | 1 0xxx xxxx                        | _                                 | 12                          | 10xx xxxx                                      | _                                  | 11                          |  |

| WRAL (Write All Memory)    | 1            | 00         | 0 1xxx xxxx                        | (D <sub>7</sub> -D <sub>0</sub> ) | 20                          | 01xx xxxx                                      | (D <sub>15</sub> -D <sub>0</sub> ) | 27                          |  |

| WRITE                      | 1            | 01         | x(A <sub>7</sub> -A <sub>0</sub> ) | (D <sub>7</sub> -D <sub>0</sub> ) | 20                          | x(A <sub>6</sub> -A <sub>0</sub> )             | (D <sub>15</sub> -D <sub>0</sub> ) | 27                          |  |

| READ                       | 1            | 10         | x(A <sub>7</sub> -A <sub>0</sub> ) | _                                 |                             | x(A <sub>6</sub> -A <sub>0</sub> )             | _                                  |                             |  |

| ERASE                      | 1            | 11         | x(A <sub>7</sub> -A <sub>0</sub> ) | _                                 | 12                          | x(A <sub>6</sub> -A <sub>0</sub> )             | _                                  | 11                          |  |

Notes: [1] x = Don't care bit.

<sup>[2]</sup> Exact number of clock cycles is required for each Op-code instruction.

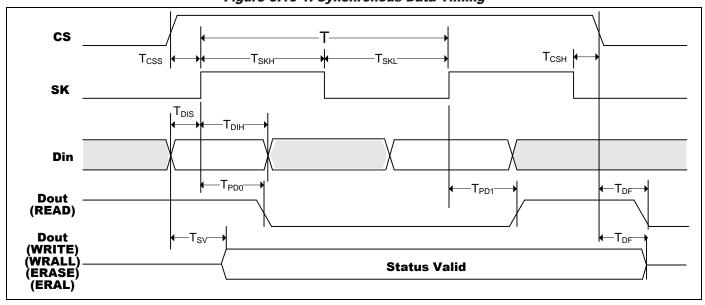

#### 5.10 Diagrams

Figure 5.10-1. Synchronous Data Timing

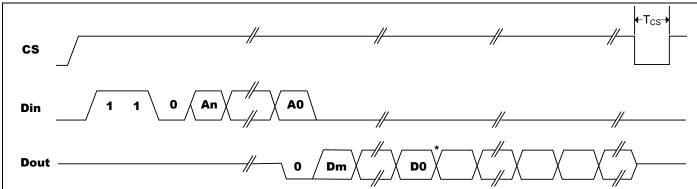

Figure 5.10-2. Read Cycle Timing

Notes: \*Address Pointer Cycles to the Next Register

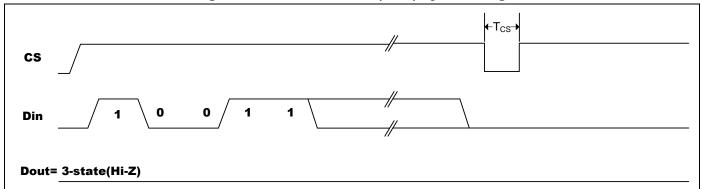

Figure 5.10-3. Write Enable (WEN) Cycle Timing

Notes: <sup>[1]</sup> After the completion of the instruction (D<sub>OUT</sub> is in READY status) then it may perform another instruction. If device is in BUSY status (D<sub>OUT</sub> indicates BUSY status) then attempting to perform another instruction could cause device malfunction.

<sup>[2]</sup> To determine data bits An - A0 and data bits Dm-D0, see Instruction Set for the appropriate device.

Figure 5.10-5. Write All (WRALL) Cycle Timing

Notes: [1] After the completion of the instruction (D<sub>OUT</sub> is in READY status) then it may perform another instruction. If device is in BUSY status (D<sub>OUT</sub> indicates BUSY status) then attempting to perform another instruction could cause device malfunction.

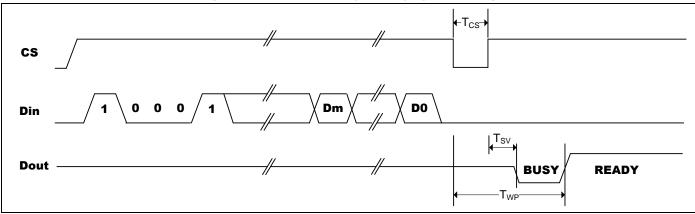

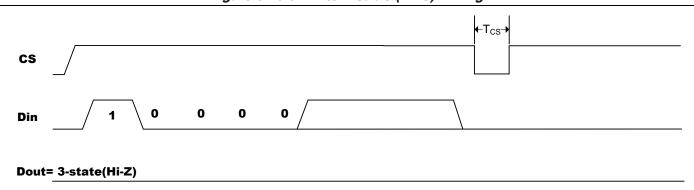

#### Figure 5.10-6. Write Disable (WDS) Timing

<sup>&</sup>lt;sup>[2]</sup> To determine data bits Dm-D0, see Instruction Set for the appropriate device.

Notes: [1] After the completion of the instruction (D<sub>OUT</sub> is in READY status) then it may perform another instruction. If device is in BUSY status (D<sub>OUT</sub> indicates BUSY status) then attempting to perform another instruction could cause device malfunction.

Figure 5.10-8. Erase All (ERAL) Cycle Timing

Notes: [1] After the completion of the instruction (D<sub>OUT</sub> is in READY status) then it may perform another instruction. If device is in BUSY status (D<sub>OUT</sub> indicates BUSY status) then attempting to perform another instruction could cause device malfunction.

$<sup>^{\</sup>mbox{\scriptsize [2]}}$  To determine data bits An - A0, see Instruction Set for the appropriate device.

<sup>&</sup>lt;sup>[2]</sup> To determine data bits An - A0, see Instruction Set for the appropriate device.

#### 6. Electrical Characteristics

#### **6.1 Absolute Maximum Ratings**

| Symbol            | Parameter              | Value                         | Unit |

|-------------------|------------------------|-------------------------------|------|

| Vs                | Supply Voltage         | -0.5 to + 6.5                 | V    |

| $V_P$             | Voltage on Any Pin     | -0.5 to V <sub>CC</sub> + 0.5 | V    |

| T <sub>BIAS</sub> | Temperature Under Bias | -55 to +125                   | °C   |

| T <sub>STG</sub>  | Storage Temperature    | -65 to +150                   | °C   |

| l <sub>OUT</sub>  | Output Current         | 5                             | mA   |

Note: Stress greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition outside those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **6.2 Operating Range**

| Range      | Ambient Temperature (T <sub>A</sub> ) | Vcc          |

|------------|---------------------------------------|--------------|

| Industrial | -40°C to +85°C                        | 1.8V to 5.5V |

Note: Giantec offers Industrial grade for Commercial applications (0°C to +70°C).

#### 6.3 Capacitance

| Symbol           | Parameter <sup>[1, 2]</sup> | Conditions     | Max. | Unit |

|------------------|-----------------------------|----------------|------|------|

| C <sub>IN</sub>  | Input Capacitance           | $V_{IN} = 0V$  | 6    | pF   |

| C <sub>I/O</sub> | Input / Output Capacitance  | $V_{I/O} = 0V$ | 8    | pF   |

Notes: [1] Tested initially and after any design or process changes that may affect these parameters and not 100% tested.

Test conditions:  $T_A = 25^{\circ}C$ , f = 1 MHz,  $V_{CC} = 5.0V$ .

#### **6.4 DC Electrical Characteristic**

Industrial:  $T_A = -40$ °C to +85°C,  $V_{cc} = 1.8V \sim 5.5V$

| Symbol           | Parameter <sup>[1]</sup> | Test Conditions                                       | Min.                  | Max.                | Unit |

|------------------|--------------------------|-------------------------------------------------------|-----------------------|---------------------|------|

| Vcc              | Supply Voltage           |                                                       | 1.8                   | 5.5                 | V    |

| V <sub>OL1</sub> | Output LOW Voltage       | V <sub>CC</sub> = 1.8V~5.5V, I <sub>OL</sub> = 100 uA | _                     | 0.2                 | V    |

| V <sub>OL2</sub> | Output LOW Voltage       | V <sub>CC</sub> = 2.5V~5.5V, I <sub>OL</sub> = 2.1 mA | _                     | 0.4                 | V    |

| V <sub>OH1</sub> | Output HIGH Voltage      | V <sub>CC</sub> = 1.8V~5.5V, I <sub>OH</sub> = -0.1mA | V <sub>CC</sub> - 0.2 | _                   | V    |

| V <sub>OH2</sub> | Output HIGH Voltage      | V <sub>CC</sub> = 2.5V~5.5V, I <sub>OH</sub> = -0.4mA | 2.4                   | _                   | V    |

| V <sub>IH1</sub> | Input HIGH Voltage       | 1.8V to 5.5V                                          | 0.7*V <sub>CC</sub>   | V <sub>CC</sub> +1  | V    |

| V <sub>IH2</sub> | Input HIGH Voltage       | 2.5V to 5.5V                                          | 2                     | V <sub>CC</sub> +1  | V    |

| V <sub>IL1</sub> | Input LOW Voltage        | 1.8V to 5.5V                                          | -0.3                  | 0.3*V <sub>CC</sub> | V    |

| $V_{IL2}$        | Input LOW Voltage        | 2.5V to 5.5V                                          | -0.3                  | 0.8                 | V    |

| ILI              | Input Leakage Current    | $V_{IN} = 0V$ to $V_{CC}$ (CS, SK, $D_{IN}$ , ORG)    | 0                     | 2.5                 | μA   |

| I <sub>LO</sub>  | Output Leakage Current   | V <sub>OUT</sub> = 0V to V <sub>CC</sub> , CS = 0V    | 0                     | 2.5                 | μA   |

#### **Power Supply Characteristics**

Industrial:  $T_A = -40$ °C to +85°C,  $V_{cc} = 1.8V \sim 5.5V$

| Symbol                | Parameter <sup>[1]</sup> | Vcc | Test Conditions                   | Min. | Тур. | Max. | Unit |

|-----------------------|--------------------------|-----|-----------------------------------|------|------|------|------|

| $V_{CC}$              | Supply Voltage           |     |                                   | 1.8  |      | 5.5  | V    |

|                       |                          | 1.8 | CS = GND, SK = GND,               | _    | 0.1  | 1    | μΑ   |

| I <sub>SB1</sub>      | Standby current          | 2.5 | ORG = V <sub>CC</sub> or Floating | _    | 0.3  | 1    | μΑ   |

|                       |                          | 5.5 | (x16), $D_{IN} = V_{CC}$ or GND   | _    | 0.5  | 1    | μΑ   |

|                       |                          | 1.8 | CS = GND, SK = GND,               | _    | 0.4  | 1    | μΑ   |

| I <sub>SB2</sub>      | Standby current          | 2.5 | ORG = GND (x8), $D_{IN} = V_{CC}$ | _    | 6    | 10   | μΑ   |

|                       |                          | 5.5 | or GND                            | _    | 10   | 15   | μΑ   |

|                       |                          | 1.8 | CS = V <sub>IH</sub> , SK = 1 MHz | _    |      | 0.5  | mA   |

| I <sub>CC-Read</sub>  | Read current             | 2.5 | CS = V <sub>IH</sub> , SK = 2 MHz | _    |      | 0.5  | mA   |

|                       |                          | 5.5 | CS = V <sub>IH</sub> , SK = 3 MHz | _    |      | 1    | mA   |

|                       |                          | 1.8 | CS = V <sub>IH</sub> , SK = 1 MHz | _    |      | 1    | mA   |

| I <sub>CC-Write</sub> | Write current            | 2.5 | CS = V <sub>IH</sub> , SK = 2 MHz | _    |      | 1    | mA   |

|                       |                          | 5.5 | CS = V <sub>IH</sub> , SK = 3 MHz | _    |      | 2    | mA   |

#### **6.5 AC Electrical Characteristic**

Industrial:  $T_A = -40$ °C to +85°C, Supply voltage = 1.8V to 5.5V

| Symbol           | Parameter <sup>[1]</sup> <sup>[2]</sup> | 1.8V≤V | /cc<2.5V 2.5V≤Vcc<4.5V 4.5V≤Vcc≤5.5V |      | Unit |      |      |      |

|------------------|-----------------------------------------|--------|--------------------------------------|------|------|------|------|------|

| Symbol           | Parameter. 1-1                          | Min.   | Max.                                 | Min. | Max. | Min. | Max. | Onit |

| F <sub>SCK</sub> | SCK Clock Frequency                     | 0      | 1                                    | 0    | 2    | 0    | 3    | MHz  |

| T <sub>R</sub>   | Input Rise Time                         | _      | 10                                   | _    | 10   | _    | 10   | ns   |

| $T_F$            | Input Fall Time                         | _      | 10                                   | _    | 10   | _    | 10   | ns   |

| T <sub>SKH</sub> | SK High Time                            | 250    | _                                    | 200  | _    | 200  | _    | ns   |

| T <sub>SKL</sub> | SK Low Time                             | 250    | _                                    | 200  | _    | 100  | _    | ns   |

| T <sub>CS</sub>  | Minimum CS LOW Time                     | 250    | _                                    | 200  | _    | 200  | _    | ns   |

| T <sub>CSS</sub> | CS Setup Time                           | 200    | _                                    | 100  | _    | 50   | _    | ns   |

| T <sub>CSH</sub> | CS Hold Time                            | 0      | _                                    | 0    | _    | 0    | _    | ns   |

| T <sub>DIS</sub> | D <sub>IN</sub> Setup Time              | 100    | _                                    | 50   | _    | 50   | _    | ns   |

| T <sub>DIH</sub> | D <sub>IN</sub> Hold Time               | 50     | _                                    | 50   | _    | 50   | _    | ns   |

| T <sub>PD1</sub> | Output Delay to "1"                     | _      | 400                                  | _    | 200  | _    | 100  | ns   |

| T <sub>PD0</sub> | Output Delay to "0"                     | _      | 400                                  | _    | 200  | _    | 100  | ns   |

| Tsv              | CS to Status Valid                      | _      | 400                                  | _    | 200  | _    | 200  | ns   |

| $T_{DF}$         | CS to D <sub>OUT</sub> in 3-state       | _      | 200                                  | _    | 100  | _    | 100  | ns   |

| T <sub>WP</sub>  | Write Cycle Time                        | _      | 10                                   | _    | 5    | _    | 5    | ms   |

Notes: [1] The parameters are characterized but not 100% tested.

[2] AC measurement conditions:

$C_L = 100 pF$

Input pulse voltages: Per  $V_{\text{IL}}$  and  $V_{\text{IH}}$  spec

Input rise and fall times: ≤ 10 ns

Timing reference voltages: half  $V_{\text{CC}}$  level

### 7. Ordering Information

#### Industrial Grade: -40°C to +85°C, Lead-free

| Voltage Range | Part Number*     | Package (8-pin)* |

|---------------|------------------|------------------|

| 1.8V to 5.5V  | GT93C56A-2GLI-TR | 150-mil SOIC     |

|               | GT93C56A-2ZLI-TR | 3 x 4.4 mm TSSOP |

1. Contact Giantec Sales Representatives for availability and other package information.

- 2. The listed part numbers are packed in tape and reel "-TR" (4K per reel). UDFN is 5K per reel.

- 3. Refer to Giantec website for related declaration document on lead free, RoHS, halogen free or Green, whichever is applicable.

- 4. Giantec offers Industrial grade for Commercial applications (0°C to +70°C).

### 8. Top Markings

### 8.1 SOIC Package

GT: Giantec Logo

356A-2GLI: Part Number GT93C56A-2GLI-TR YWW: Date Code, Y=year, WW=week

#### 8.2 TSSOP Package

GT: Giantec Logo

356A-2ZLI: Part Number, GT93C56A-2ZLI-TR

YWW: Date Code, Y=year, WW=week

#### 9. Package Information

#### 9.1 **SOIC**

### **8L 150mil SOIC Package Outline**

**9.2 TSSOP**

#### **8L 3x4.4mm TSSOP Package Outline**

### 10. Revision History

| Revision | Date      | Descriptions            |

|----------|-----------|-------------------------|

| A0       | Nov. 2010 | Initial version         |

| A1       | Jun. 2011 | New datasheet format    |

| A2       | Oct. 2013 | Revise SOIC/SOP to SOIC |