June 1991 Revised December 1998

# 74ACTQ16373 16-Bit Transparent Latch with 3-STATE Outputs

## **General Description**

The ACTQ16373 contains sixteen non-inverting latches with 3-STATE outputs and is intended for bus oriented applications. The device is byte controlled. The flip-flops appear transparent to the data when the Latch Enable (LE) is HIGH. When LE is low, the data that meets the setup time is latched. Data appears on the bus when the Output Enable (OE) is LOW. When OE is HIGH, the outputs are in high Z state. The ACTQ16373 utilizes Fairchild's Quiet Series™ technology to guarantee quiet output switching and improved dynamic threshold performance. FACT Quiet Series™ features GTO™ output control for superior performance.

#### **Features**

- Utilizes Fairchild FACT Quiet Series technology

- Guaranteed simultaneous switching noise level and dynamic threshold performance

- Guaranteed pin-to-pin output skew

- Separate control logic for each byte

- 16-bit version of the ACTQ373

- Outputs source/sink 24 mA

- Additional specs for Multiple Output Switching

- Output Loading specs for both 50 pF and 250 pF loads

## **Ordering Code:**

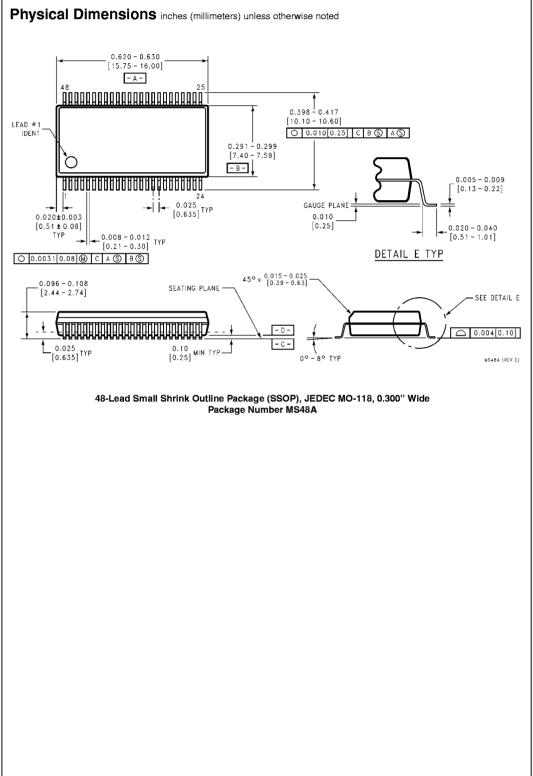

| Order Number   | Package Number | Package Description                                                         |

|----------------|----------------|-----------------------------------------------------------------------------|

| 74ACTQ16373MEA | MS48A          | 48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300" Wide      |

| 74ACTQ16373MTD | MTD48          | 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide |

Device also available in Tape and Reel. Specify by appending suffix letter "X" to the ordering code.

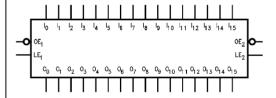

# **Logic Symbol**

#### **Pin Descriptions**

| Pin Names                       | Description                      |  |  |  |

|---------------------------------|----------------------------------|--|--|--|

| ŌĒn                             | Output Enable Input (Active Low) |  |  |  |

| LEn                             | Latch Enable Input               |  |  |  |

| I <sub>0</sub> —I <sub>15</sub> | Inputs                           |  |  |  |

| O <sub>0</sub> -O <sub>15</sub> | Outputs                          |  |  |  |

# **Connection Diagram**

FACT™, Quiet Series™, FACT Quiet Series™, and GTO™ are trademarks of Fairchild Semiconductor Corporation.

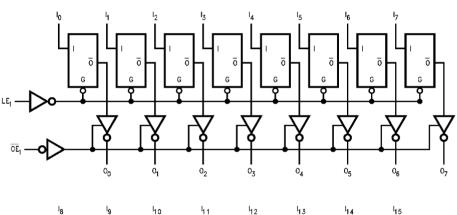

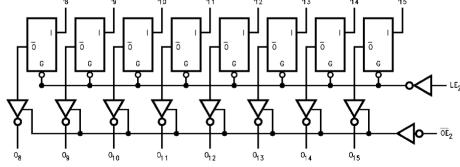

# **Functional Description**

The ACTQ16373 contains sixteen D-type latches with 3-STATE standard outputs. The device is byte controlled with each byte functioning identically, but independent of the other. Control pins can be shorted together to obtain full 16-bit operation. The following description applies to each byte. When the Latch Enable (LEn) input is HIGH, data on the  $D_n$  enters the latches. In this condition the latches are transparent, i.e., a latch output will change states each time its D input changes. When LEn is LOW, the latches store information that was present on the D inputs a setup time preceding the HIGH-to-LOW transition of  $LE_n$ . The 3-STATE standard outputs are controlled by the Output Enable  $(\overline{\sf OE}_n)$  input. When  $\overline{\sf OE}_n$  is LOW, the standard outputs are in the 2-state mode. When  $\overline{\text{OE}}_n$  is HIGH, the standard outputs are in the high impedance mode but this does not interfere with entering new data into the latches.

#### **Truth Tables**

|                 | Inputs          | Outputs                        |                                |

|-----------------|-----------------|--------------------------------|--------------------------------|

| LE <sub>1</sub> | ŌE <sub>1</sub> | I <sub>0</sub> —I <sub>7</sub> | 0 <sub>0</sub> –0 <sub>7</sub> |

| Х               | Н               | Х                              | Z                              |

| Н               | L               | L                              | L                              |

| Н               | L               | Н                              | Н                              |

| L               | L               | Χ                              | (Previous)                     |

|                 | Inputs            | Outputs                         |                                 |

|-----------------|-------------------|---------------------------------|---------------------------------|

| LE <sub>2</sub> | $\overline{OE}_2$ | I <sub>8</sub> —I <sub>15</sub> | O <sub>8</sub> -O <sub>15</sub> |

| Х               | Н                 | Х                               | Z                               |

| Н               | L                 | L                               | L                               |

| Н               | L                 | Н                               | Н                               |

| L               | L                 | Χ                               | (Previous)                      |

- H = HIGH Voltage Level

- L = LOW Voltage Level X = Immaterial

- Z = High Impedance

Previous = previous output prior to HIGH to LOW transition of LE

# **Logic Diagrams**

125 mV/ns

## **Absolute Maximum Ratings**(Note 1)

Supply Voltage (V<sub>CC</sub>) -0.5V to +7.0V

DC Input Diode Current (I<sub>IK</sub>)

$V_1 = -0.5V$ -20 mA  $V_I = V_{CC} + 0.5V$ +20 mA

DC Output Diode Current (I<sub>OK</sub>)

$V_{O} = -0.5V$ -20 mA  $V_O = V_{CC} + 0.5V$ +20 mA DC Output Voltage (V<sub>O</sub>) -0.5V to  $V_{CC} + 0.5$ V

DC Output Source/Sink Current (I<sub>O</sub>) +50 m**A** DC V<sub>CC</sub> or Ground Current +50 mA

per Output Pin

Junction Temperature +140°C Storage Temperature -65°C to+150°C

# Supply Voltage (V<sub>CC</sub>)

**Recommended Operating**

4.5V to 5.5V Input Voltage (V<sub>I</sub>) 0V to  $V_{CC}$ 0V to V<sub>CC</sub> Output Voltage (V<sub>O</sub>) -40°C to +85°C Operating Temperature (TA)

Minimum Input Edge Rate (ΔV/Δt)  $V_{\text{IN}}$  from 0.8V to 2.0V

V<sub>CC</sub> @ 4.5V, 5.5V

**Conditions**

Note 1: Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, without exception to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. Fairchild does not recommend operation of FACT™ circuits outside databook specifications.

## **DC Electrical Characteristics**

| Symbol           | Parameter                       | $v_{cc}$ | T <sub>A</sub> = -    | + <b>25°C</b>         | T <sub>A</sub> = -40°C to +85°C | Units | Conditions                               |  |

|------------------|---------------------------------|----------|-----------------------|-----------------------|---------------------------------|-------|------------------------------------------|--|

| -                |                                 | (V)      | Тур                   | Gua                   | aranteed Limits                 |       |                                          |  |

| V <sub>IH</sub>  | Minimum HIGH                    | 4.5      | 1.5                   | 2.0                   | 2.0                             | V     | V <sub>OUT</sub> = 0.1V                  |  |

|                  | Input Voltage                   | 5.5      | 1.5                   | 2.0                   | 2.0                             |       | or V <sub>CC</sub> – 0.1V                |  |

| V <sub>IL</sub>  | Maximum LOW                     | 4.5      | 1.5                   | 0.8                   | 0.8                             | V     | V <sub>OUT</sub> = 0.1V                  |  |

|                  | Input Voltage                   | 5.5      | 1.5                   | 0.8                   | 0.8                             |       | or V <sub>CC</sub> – 0.1V                |  |

| V <sub>OH</sub>  | Minimum HIGH                    | 4.5      | 4.49                  | 4.4                   | 4.4                             | V     | I <sub>OUT</sub> = -50 μA                |  |

| = ***            | Output Voltage                  | 5.5      | 5.49                  | 5.4                   | 5.4                             |       |                                          |  |

|                  |                                 |          |                       |                       |                                 |       | $V_{IN} = V_{IL}$ or $V_{IH}$            |  |

|                  |                                 | 4.5      |                       | 3.86                  | 3.76                            | V     | I <sub>OH</sub> = -24 mA                 |  |

|                  |                                 | 5.5      |                       | 4.86                  | 4.76                            |       | I <sub>OH</sub> = -24 mA (Note 2)        |  |

| V <sub>OL</sub>  | Maximum LOW                     | 4.5      | 0.001                 | 0.1                   | 0.1                             | ٧     | I <sub>OUT</sub> = 50 μA                 |  |

|                  | Output Voltage                  | 5.5      | 0.001                 | 0.1                   | 0.1                             |       |                                          |  |

|                  |                                 |          |                       |                       |                                 |       | $V_{IN} = V_{IL}$ or $V_{IH}$            |  |

|                  |                                 | 4.5      |                       | 0.36                  | 0.44                            | ٧     | I <sub>OL</sub> = 24 mA                  |  |

|                  |                                 | 5.5      |                       | 0.36                  | 0.44                            |       | I <sub>OL</sub> = 24 mA (Note 2)         |  |

| loz              | Maximum 3-STATE                 | 5.5      | +                     | ± 0.5                 | ± 5.0                           | μΑ    | $V_I = V_{IL}, V_{IH}$                   |  |

|                  | Leakage Current                 |          |                       |                       |                                 |       | $V_O = V_{CC}$ , GND                     |  |

| I <sub>IN</sub>  | Maximum Input                   | 5.5      |                       | ± 0.1                 | ± 1.0                           | μΑ    | V <sub>I</sub> = V <sub>CC</sub> , GND   |  |

|                  | Leakage Current                 |          |                       |                       |                                 |       |                                          |  |

| Гсст             | Maximum I <sub>CC</sub> /Input  | 5.5      | 0.6                   |                       | 1.5                             | mA    | V <sub>I</sub> = V <sub>CC</sub> - 2.1V  |  |

| lcc              | Max Quiescent Supply Current    | 5.5      |                       | 8.0                   | 80.0                            | μΑ    | V <sub>IN</sub> = V <sub>CC</sub> or GND |  |

| lold             | Minimum Dynamic                 | 5.5      |                       |                       | 75                              | mA    | V <sub>OLD</sub> = 1.65V Max             |  |

| I <sub>OHD</sub> | Output Current (Note 3)         |          |                       |                       | -75                             | mA    | V <sub>OHD</sub> = 3.85V Min             |  |

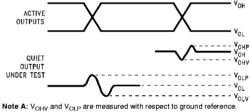

| V <sub>OLP</sub> | Quiet Output                    | 5.0      | 0.5                   | 0.8                   |                                 | V     | Figure 1, Figure 2                       |  |

|                  | Maximum Dynamic V <sub>OL</sub> |          |                       |                       |                                 |       | (Note 5)(Note 6)                         |  |

| V <sub>OLV</sub> | Quiet Output                    | 5.0      | -0.5                  | -1.0                  |                                 | V     | Figure 1, Figure 2                       |  |

|                  | Minimum Dynamic V <sub>OL</sub> |          |                       |                       |                                 |       | (Note 5)(Note 6)                         |  |

| V <sub>OHP</sub> | Maximum Overshoot               | 5.0      | V <sub>OH</sub> + 1.0 | V <sub>OH</sub> + 1.5 |                                 | ٧     | Figure 1, Figure 2                       |  |

| _                |                                 |          |                       |                       |                                 |       | (Note 4)(Note 6)                         |  |

| V <sub>OHV</sub> | Minimum V <sub>CC</sub> Droop   | 5.0      | V <sub>OH</sub> – 1.0 | V <sub>OH</sub> – 1.8 |                                 | ٧     | Figure 1, Figure 2                       |  |

|                  |                                 |          |                       |                       |                                 |       | (Note 4)(Note 6)                         |  |

| V <sub>IHD</sub> | Minimum HIGH Dynamic            | 5.0      | 1.7                   | 2.0                   |                                 | V     | (Note 4)(Note 7)                         |  |

|                  | Input Voltage Level             |          |                       |                       |                                 |       |                                          |  |

| V <sub>ILD</sub> | Maximum LOW Dynamic             | 5.0      | 1.2                   | 0.8                   |                                 | ٧     | (Note 4)(Note 7)                         |  |

|                  | Input Voltage Level             |          |                       |                       |                                 |       |                                          |  |

## DC Electrical Characteristics (Continued)

Note 3: Maximum test duration 2.0 ms; one output loaded at a time.

Note 4: Worst case package

Note 5: Maximum number of outputs that can switch simultaneously is n. (n-1) outputs are switched LOW and one output held LOW.

Note 6: Maximum number of outputs that can switch simultaneously is n. (n - 1) outputs are switched HIGH and one output held HIGH.

Note 7: Max number of data inputs (n) switching, (n - 1) input switching 0V to 3V. Input under test switching 3V to threshold (V<sub>ILD</sub>)

#### **AC Electrical Characteristics**

|                  |                                  | V <sub>cc</sub> |     | T <sub>A</sub> = +25°C |     | T <sub>A</sub> = -40° | C to +85°C |       |

|------------------|----------------------------------|-----------------|-----|------------------------|-----|-----------------------|------------|-------|

| Symbol           | Parameter                        | (V)             |     | $C_L = 50 \ pF$        |     | C <sub>L</sub> =      | 50 pF      | Units |

|                  |                                  | (Note 8)        | Min | Тур                    | Max | Min                   | Max        |       |

| t <sub>PLH</sub> | Propagation Delay                | 5.0             | 3.1 | 5.3                    | 7.9 | 3.1                   | 8.4        | ns    |

| t <sub>PHL</sub> | D <sub>n</sub> to O <sub>n</sub> |                 | 2.6 | 4.6                    | 7.3 | 2.6                   | 7.8        |       |

| t <sub>PLH</sub> | Propagation Delay                | 5.0             | 3.1 | 5.4                    | 7.9 | 3.2                   | 8.4        | ns    |

| t <sub>PHL</sub> | LE to O <sub>n</sub>             |                 | 2.8 | 4.9                    | 7.3 | 2.8                   | 7.8        |       |

| t <sub>PZH</sub> | Output Enable                    | 5.0             | 2.5 | 4.7                    | 7.4 | 2.5                   | 7.9        | ns    |

| t <sub>PZL</sub> | Delay                            |                 | 2.7 | 4.8                    | 7.5 | 2.7                   | 8.0        |       |

| t <sub>PHZ</sub> | Output Disable                   | 5.0             | 2.1 | 5.1                    | 7.9 | 2.1                   | 8.2        | ns    |

| t <sub>PLZ</sub> | Delay                            |                 | 2.0 | 4.5                    | 7.4 | 2.0                   | 7.9        |       |

Note 8: Voltage Range 5.0 is 5.0V ± 0.5V.

## **Extended AC Electrical Characteristics**

|                  |                      | TA   | =-40°C to +8                     | 5°C  |                       |                         |    |

|------------------|----------------------|------|----------------------------------|------|-----------------------|-------------------------|----|

|                  |                      |      | $\mathbf{V_{CC}} = \mathbf{Com}$ |      | T <sub>A</sub> = -40° | C to +85°C              |    |

|                  |                      |      | $C_L = 50 \ pF$                  |      | V <sub>CC</sub> = Com |                         |    |

| Symbol           | Parameter            | 16 ( | 16 Outputs Switching             |      |                       | C <sub>L</sub> = 250 pF |    |

|                  |                      |      | (Note 10)                        |      | (Note 11)             |                         |    |

|                  |                      | Min  | Тур                              | Max  | Min                   | Max                     |    |

| t <sub>PLH</sub> | Propagation Delay    | 4.7  |                                  | 12.7 | 6.6                   | 15.7                    | ns |

| t <sub>PHL</sub> | Data to Output       | 4.6  |                                  | 10.6 | 6.4                   | 14.5                    |    |

| t <sub>PLH</sub> | Propagation Delay    | 4.6  |                                  | 13.3 | 6.3                   | 15.3                    | ns |

| t <sub>PHL</sub> | Latch Enable to      | 4.1  |                                  | 10.4 | 5.8                   | 13.6                    |    |

|                  | Output               |      |                                  |      |                       |                         |    |

| t <sub>PZH</sub> | Output Enable        | 3.5  |                                  | 10.4 | (Not                  | e 12)                   | ns |

| $t_{PZL}$        | Time                 | 3.6  |                                  | 10.9 |                       |                         |    |

| t <sub>PHZ</sub> | Output Disable       | 3.4  |                                  | 8.5  | (Not                  | e 13)                   | ns |

| $t_{PLZ}$        | Time                 | 3.1  |                                  | 8.1  |                       |                         |    |

| toshl            | Pin to Pin Skew      |      |                                  |      |                       |                         |    |

| (Note 9)         | HL Data to           |      |                                  | 1.3  |                       |                         | ns |

|                  | Output               |      |                                  |      |                       |                         |    |

| toslh            | Pin to Pin Skew      |      |                                  | 2.1  |                       |                         | ns |

| (Note 9)         | LH Data to Output    |      |                                  |      |                       |                         |    |

| tost             | Pin to Pin Skew      |      |                                  |      |                       |                         |    |

| (Note 9)         | LH/HL Data to Output |      |                                  | 4.0  |                       |                         | ns |

Note 9: Skew is defined as the absolute value of the difference between the actual propagation delays for any two separate outputs of the same device. The specification applies to any outputs switching HIGH to LOW (toshL), LOW to HIGH (toshL), or any combination switching LOW to HIGH and/or HIGH to LOW (tosh).

Note 10: This specification is guaranteed but not tested. The limits apply to propagation delays for all paths described switching in phase (i.e., all low-to-high, high-to-low, etc.).

Note 11: This specification is guaranteed but not tested. The limits represent propagation delays with 250 pF load capacitors in place of the 50 pF load capacitors in the standard AC load. This specification pertains to single output switching only.

Note 12: 3-STATE delays are load dominated and have been excluded from the datasheet.

$\textbf{Note 13:} \ \text{The Output Disable Time is dominated by the RC Network (500$\Omega$, 250 pF) on the output and has been excluded from the datasheet.}$

# **AC Operating Requirements**

|                |                     | V <sub>CC</sub> |                  | +25°C | T <sub>A</sub> = -40°C to +85°C |       |

|----------------|---------------------|-----------------|------------------|-------|---------------------------------|-------|

| Symbol         | Parameter           | (V)             | C <sub>L</sub> = | 50 pF | C <sub>L</sub> = 50 pF          | Units |

|                |                     | (Note 14)       | Тур              | Guai  | ranteed Minimum                 |       |

| t <sub>S</sub> | Setup Time, HIGH or | 5.0             |                  | 3.0   | 3.0                             | ns    |

|                | LOW, Input to Clock |                 |                  |       |                                 |       |

| t <sub>H</sub> | Hold time, High or  | 5.0             |                  | 1.5   | 1.5                             | ns    |

|                | LOW, Input to Clock |                 |                  |       |                                 |       |

| t <sub>W</sub> | CS Pulse Width,     | 5.0             |                  | 4.0   | 4.0                             | ns    |

|                | HIGH or LOW         |                 |                  |       |                                 |       |

Note 14: Voltage Range 5.0 is 5.0V ± 0.5V

# Capacitance

| Symbol          | Parameter                     | Тур | Units | Conditions      |

|-----------------|-------------------------------|-----|-------|-----------------|

| C <sub>IN</sub> | Input Capacitance             | 4.5 | pF    | $V_{CC} = 5.0V$ |

| C <sub>PD</sub> | Power Dissipation Capacitance | 30  | рF    | $V_{CC} = 5.0V$ |

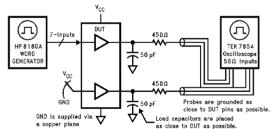

#### **FACT Noise Characteristics**

The setup of a noise characteristics measurement is critical to the accuracy and repeatability of the tests. The following is a brief description of the setup used to measure the noise characteristics of FACT.

#### Equipment:

Hewlett Packard Model 8180A Word Generator PC-163A Test Fixture

Tektronics Model 7854 Oscilloscope

#### Procedure:

- 1. Verify Test Fixture Loading: Standard Load 50 pF,  $500\Omega$ .

- Deskew the HFS generator so that no two channels have greater than 150 ps skew between them. This requires that the oscilloscope be deskewed first. It is important to deskew the HFS generator channels before testing. This will ensure that the outputs switch simultaneously.

- Terminate all inputs and outputs to ensure proper loading of the outputs and that the input levels are at the correct voltage.

- Set the HFS generator to toggle all but one output at a frequency of 1 MHz. Greater frequencies will increase DUT heating and effect the results of the measurement.

- Set the HFS generator input levels at 0V LOW and 3V HIGH for ACT devices and 0V LOW and 5V HIGH for AC devices. Verify levels with an oscilloscope.

**Note B:** Input pulses have the following characteristics: f = 1 MHz,  $t_r = 3$  ns,  $t_f = 3$  ns, skew < 150 ps.

#### FIGURE 1. Quiet Output Noise Voltage Waveforms

#### V<sub>OLP</sub>/V<sub>OLV</sub> and V<sub>OHP</sub>/V<sub>OHV</sub>:

- Determine the quiet output pin that demonstrates the greatest noise levels. The worst case pin will usually be the furthest from the ground pin. Monitor the output voltages using a 50Ω coaxial cable plugged into a standard SMB type connector on the test fixture. Do not use an active FET probe.

- Measure V<sub>OLP</sub> and V<sub>OLV</sub>on the quiet output during the worst case transition for active and enable. Measure V<sub>OHP</sub> and V<sub>OHV</sub> on the quiet output during the worst case active and enable transition.

- Verify that the GND reference recorded on the oscilloscope has not drifted to ensure the accuracy and repeatability of the measurements.

#### VILD and VIHD:

- Monitor one of the switching outputs using a  $50\Omega$  coaxial cable plugged into a standard SMB type connector on the test fixture. Do not use an active FET probe.

- First increase the input LOW voltage level, V<sub>IL</sub>, until the output begins to oscillate or steps out a min of 2 ns. Oscillation is defined as noise on the output LOW level that exceeds V<sub>IL</sub> limits, or on output HIGH levels that exceed V<sub>IH</sub> limits. The input LOW voltage level at which oscillation occurs is defined as V<sub>II.D</sub>.

- Next decrease the input HIGH voltage level, V<sub>IH</sub> until the output begins to oscillate or steps out a min of 2 ns. Oscillation is defined as noise on the output LOW level that exceeds V<sub>IL</sub> limits, or on output HIGH levels that exceed V<sub>IH</sub> limits. The input HIGH voltage level at which oscillation occurs is defined as V<sub>IHD</sub>.

- Verify that the GND reference recorded on the oscilloscope has not drifted to ensure the accuracy and repeatability of the measurements.

FIGURE 2. Simultaneous Switching Test Circuit

#### Physical Dimensions inches (millimeters) unless otherwise noted (Continued) -A-GAGE PLANE 8.1 $6.1 \pm 0.1$ -B-SEATING PLANE 4.05 0.60 +0.15 DETAIL A △ 0.2 C B A TYPICAL ALL LEAD TIPS □ 0.1 C SEE DETAIL A (0.90)ALL LEAD TIPS 1.1 MAX -C-0.09-0.20 TYP 0.17 - 0.27 TYP 0.10 ± 0.05 TYP ⊕ 0.13 M A B S C S MTD48 (REV A)

48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide Package Number MTD48

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com