Data sheet acquired from Harris Semiconductor SCHS070A – Revised March 2002

# CMOS Dual 4-Bit Latch

High-Voltage Types (20-Volt Rating)

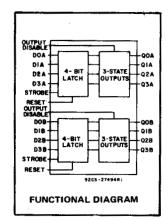

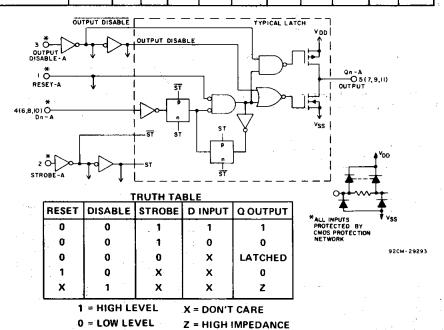

■ CD4508B dual 4-bit latch contains two identical 4-bit latches with separate STROBE, RESET, and OUTPUT DISABLE controls. With the STROBE line in the high state, the data on the "D" inputs appear at the corresponding "Q" outputs provided the DISABLE line is in the low state. Changing the STROBE line to the low state locks the data into the latch. A high on the reset line forces the outputs to a low level regardless of the state of the STROBE input. The outputs are forced to the high-impedance state for bus line applications by a high level on the DISABLE input.

The CD4508B types are supplied in the 24-lead dual-in-line ceramic packages (D and F suffixes), 24-lead dual-in-line plastic packages (E suffix), 24-lead small-outline package (NSR suffix), and in chip form (H suffix).

The CD4508B is similar to industry type MC14508.

## Features:

- Two independent 4-bit latches

- Individual master reset for each 4-bit latch

- 3-state outputs with high-impedance state for bus line applications

- Medium-speed operation: tpHL = tpLH = 70 ns (typ.) at VDD = 10 V and CL = 50 pF

- 100% tested for quiescent current at 20 V

- 5-V, 10-V, and 15-V parametric ratings

- Standardized, symmetrical output characteristics

- Maximum input current of 1 μA at 18 V over full package-temperature range; 100 nA at 18 V and 25°C

- Noise margin (full package-temperature range) =

1 V at VDD = 5 V

2 V at V<sub>DD</sub> = 10 V

2.5 V at VDD = 15 V

Meets all requirements of JEDEC Tentative Standard No. 13B,"Standard Specifications for Description of 'B' Series CMOS Devices"

#### Applications:

- Buffer storage

- Holding registers

- Data storage and multiplexing

### MAXIMUM RATINGS, Absolute-Maximum Values:

DC SUPPLY-VOLTAGE RANGE, (VDD)

| ,                                     | 20 201 21 10211102 1 1 1 1 1 1 1 1 1 1 1    |

|---------------------------------------|---------------------------------------------|

| -0.5V to +20V                         | Voltages referenced to VSS Terminal) .      |

| 0.5V to V <sub>DD</sub> +0.5V         | INPUT VOLTAGE RANGE, ALL INPUTS .           |

| ±10mA                                 | DC INPUT CURRENT, ANY ONE INPUT .           |

| (P <sub>D</sub> ):                    | POWER DISSIPATION PER PACKAGE (I            |

| 500mW                                 | For $T_A = -55^{\circ}C$ to $+100^{\circ}C$ |

| Derate Linearity at 12mW/°C to 200mW  | For TA = +100°C to +125°C                   |

| RANSISTOR                             | DEVICE DISSIPATION PER OUTPUT TRA           |

| ATURE RANGE (All Package Types) 100mW | FOR TA = FULL PACKAGE-TEMPERAT              |

| (T <sub>A</sub> )55°C to +125°C       | <b>OPERATING-TEMPERATURE RANGE (T.</b>      |

| ta)65°C to +150°C                     |                                             |

|                                       | LEAD TEMPERATURE (DURING SOLDE              |

| 0.79mm) from case for 10s max +265°C  | At distance 1/16 ± 1/32 inch (1.59 ± 0.7    |

RECOMMENDED OPERATING CONDITIONS at  $T_A = 25^{\circ}$ C, Except as Noted. For maximum reliability, nominal operating conditions should be selected so that operation is always within the following ranges:

|                                                                    | V <sub>DD</sub> | LIM  | IITS |       |

|--------------------------------------------------------------------|-----------------|------|------|-------|

| CHARACTERISTIC                                                     | (V)             | Min. | Max. | UNITS |

| Supply-Voltage Range (For TA = Full Package-<br>Temperature Range) |                 | 3    | 18   | ٧     |

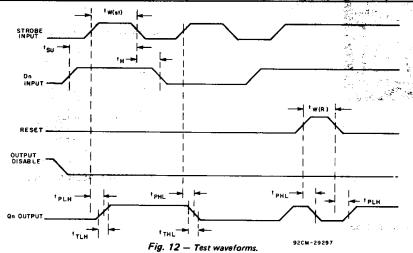

|                                                                    | 5               | 200  | _    |       |

| Reset Pulse Width, tW(R)                                           | 10              | 140  | -    |       |

|                                                                    | 15              | 100  | _    | j     |

|                                                                    | 5               | 140  | _    | 1     |

| Strobe Pulse Width, tW(st)                                         | 10              | 80   | -    |       |

|                                                                    | 15              | 70   | _    |       |

|                                                                    | 5               | 50   | _    | ns    |

| Setup Time, t <sub>SU</sub>                                        | 10              | 30   | l –  | 1     |

|                                                                    | 15              | 20   | _    |       |

|                                                                    | 5               | 0    | -    | ] .   |

| Hold Time, tH                                                      | 10              | 0    | -    |       |

|                                                                    | 15              | 0    | _    |       |

CD4508B Types

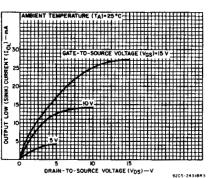

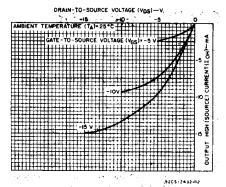

ig.2 - Typical output low (sink) current characteristics.

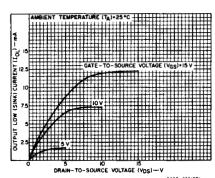

Fig.3 - Minimum output low (sink) current characteristics.

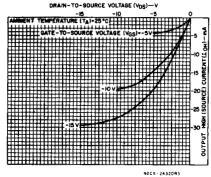

Fig.4 — Typical output high (source) current characteristics.

Copyright © 2002, Texas Instruments Incorporated

### STATIC ELECTRICAL CHARACTERISTICS

| CHARACTER-                                     | CONE     | HOITIC | IS . | LIMIT      | S AT II    |       | ERATURES (°C) |                   |                   |                    |            |

|------------------------------------------------|----------|--------|------|------------|------------|-------|---------------|-------------------|-------------------|--------------------|------------|

| ISTIC                                          | Vo :     | VIN    | VDD  |            |            |       |               |                   | +25               |                    | UNITS      |

|                                                | (V)      | (V)    | :(V) | <b>–55</b> | <b>-40</b> | +85   | +125          | Min.              | Тур.              | Max.               | 0.010      |

| Quiescent Device                               | _        | 0,5    | 5    | <b>.</b> 5 | 5          | 150   | 150           | 4                 | 0.04              | . 5                |            |

| Current,                                       | _        | 0,10   | 10   | 10         | 10         | 300   | 300           | . <del>-</del> .: | 0.04              | 10                 | μА         |

|                                                |          | 0,15   | 15   | 20         | 20         | 600   | 600           | s <del></del> - ; | 0.04              | 20                 | "          |

| × .                                            |          | .0,20  | 20   | 100        | 100        | 3000  | 3000          | — · ,             | 0.08              | 100                | 100        |

| Output Low                                     | 0.4      | 0,5    | - 5  | 0.64       | 0.61       | 0.42  | 0.36          | 0.51              | 1 1               |                    | 1 2 2 2 3  |

| (Sink) Current                                 | 0.5      | 0,10   | 10   | 1.6        | 1.5        | 1.1   | 0.9           | 1.3               | 2.6               | -                  |            |

| IOL Min.                                       | 1.5      | 0,15   | 15   | 4.2        | 4          | 2.8   | 2.4           | 34                | 6.8               | _                  |            |

| Output High                                    | 4.6      | 0,5    | 5    | -0.64      | -0.61      | -0.42 | -0.36         | -0.51             | -1                | -                  | mA         |

| (Source)                                       | 2.5      | 0,5    | - 5  | -2         | -1.8       | -1.3  | -1.15         | -1.6              | -3.2              | ., -               |            |

| Current,                                       | 9.5      | 0,10   | 10   | -1.6       | -1.5       | -1.1  | -0.9          | -1.3              | -2.6              | -                  |            |

| 10H MILL.                                      | 13.5     | 0,15   | 15   | -4.2       | -4         | -2.8  | -2.4          | <b>-3.4</b> ∵     | -6.8              |                    |            |

| Output Voltage:                                | -        | 0,5    | 5    |            | 0          | .05   | 75.1          | 1 22 11           | 0                 | 0.05               | S - 196    |

| Low-Level,<br>VOL Max.                         | _        | 0,10   | 10   |            | 0          | .05   |               | -                 | 0                 | 0.05               | ا کو انجوا |

| AOF Max.                                       | - , , ,  | 0,15   | 15   |            | 0          | .05   |               | _                 | 0                 | 0.05               | v          |

| Output Voltage:                                | _        | 0,5    | 5    |            | 4          | 4.95  | 5             | _                 |                   |                    |            |

| High-Level,                                    | _        | 0,10   | 10   |            | 9          | 95    |               | 9.95              | 10                | -                  |            |

| VOH Min.                                       | _        | 0,15   | 15   |            | 14         | .95   |               | 14.95             | 15                | ±( <del>**</del> . |            |

| Input Low                                      | 0.5, 4.5 | _      | 5    |            |            | .5    |               | _                 | _                 | 1.5                | *** . **   |

| Voltage,                                       | 1, 9     | _      | 10   |            |            | 3     |               |                   | - 12              | 3                  | 4 - 44     |

| VIL Max.                                       | 1.5,13.5 | _      | 15   | 7.         |            | 4     |               | _                 |                   | 4                  |            |

| Input High                                     | 0.5, 4.5 | _      | 5    |            | 3          | 1.5   |               | 3.5               | -                 | _                  | ٧          |

| Voltage,                                       | 1, 9     | -      | 10   |            |            | 7     |               | 7                 |                   | _                  |            |

| VIH Min.                                       | 1.5,13.5 |        | 15   |            | •          | 1     |               | 11                | -                 | -                  |            |

| Input Current IIN Max.                         | _        | 0,18   | 18   | ±0.1       | ±0.1       | ±1    | ±1            | _                 | ±10 <sup>-5</sup> | ±0.1               | μΑ         |

| 3-State Output<br>Leakage Current<br>IOUT Max. | 0,18     | 0,18   | 18   | ±0.4       | ±0.4       | ±12   | ±12           |                   | ±10-4             | ±0.4               | μΑ         |

Fig. 7 — Logic diagram (A-Section), 1 of 4 identical latches with common output disable, reset, and strobe.

Fig. 4 — Minimum output high (source) current characteristics.

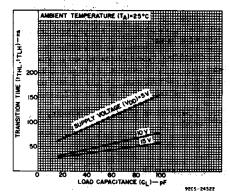

Fig. 5 — Typical transition time as a function of load capacitance.

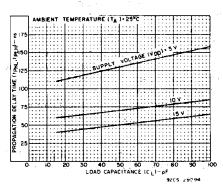

Fig. 6 — Typical propagation delay time as a function of load capacitance (strobe to data out).

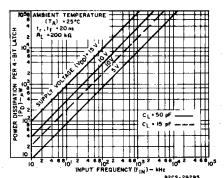

Fig. 8 — Typical power dissipation as a function of frequency.

# CD4508B Types

DYNAMIC ELECTRICAL CHARACTERISTICS at T<sub>A</sub> = 25°C; Input t<sub>f</sub>, t<sub>f</sub> = 20 ns, C<sub>L</sub> = 50 pF, R<sub>L</sub> = 200 k $\Omega$ , unless otherwise specified.

|                                     | TEST       |     | Lif  | MITS |       |

|-------------------------------------|------------|-----|------|------|-------|

| CHARACTERISTIC                      | CONDITIONS | VDD | Тур. | Max. | UNITS |

|                                     |            | 5   | 100  | 200  |       |

| Transition Time, tTHL, tTLH         |            | 10  | 50   | 100  | **:   |

|                                     |            | 15  | 40   | 80   |       |

|                                     |            | 5   | 100  | 200  | İ     |

| Minimum Reset Pulse Width, tW(R)    |            | 10  | 70   | 140  |       |

|                                     |            | 15  | 50   | 100  |       |

|                                     |            | 5   | 70   | 140  |       |

| Minimum Strobe Pulse Width, tW(st)  |            | 10  | . 40 | 80   |       |

|                                     | İ          | 15  | 35   | 70   |       |

|                                     |            | 5   | 25   | 50   |       |

| Minimum Setup Time, t <sub>SU</sub> |            | 10  | 15   | 30   |       |

|                                     |            | 15  | 10   | 20   |       |

|                                     |            | 5   | 0    | 0    |       |

| Minimum Hold Time, tH               |            | 10  | 0    | 0    |       |

|                                     |            | 15  | 0    | 0    |       |

| Propagation Delay Times: tpHL,tpLH  |            | 5   | 130  | 260  |       |

| Strobe to Data Out                  | 1 1 1      | 10  | . 70 | 140  |       |

| ,                                   |            | 15  | 50   | 100  | ns    |

|                                     |            | 5   | 105  | 210  |       |

| Data In to Data Out                 |            | 10  | 60   | 120  |       |

|                                     |            | 15  | 45   | 90   |       |

|                                     |            | 5   | 90   | 180  |       |

| Reset to Data Out                   |            | 10  | 50   | 100  |       |

|                                     |            | 15  | 40   | 80   |       |

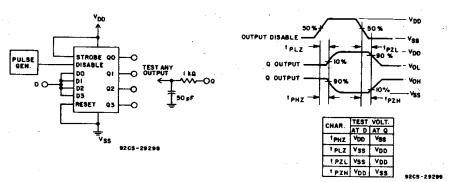

| O Control Discounting D. L. T.      |            | 5   | 90   | 180  |       |

| 3-State Propagation Delay Times:    |            | 10  | 50   | 100  |       |

| Output High to High Impedance,tpHZ  |            | 15  | 35   | 70   |       |

|                                     |            | 5   | 90   | 180  |       |

| High Impedance to Output High, tpZH |            | 10  | 50   | 100  |       |

|                                     |            | 15  | 35   | - 70 | ÷     |

|                                     |            | 5   | 90   | -180 |       |

| Output Low to High Impedance, tpLZ  |            | 10  | 50   | 100  |       |

|                                     |            | 15  | 35   | 70   |       |

|                                     |            | 5   | 90   | 180  |       |

| High Impedance to Output Low, tpZL  |            | 10  | 50   | 100  |       |

|                                     |            | 15  | 35   | 70   |       |

| Input Capacitance, CIN              | Any Input  |     | 5    | 7.5  | pF    |

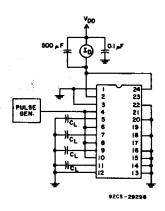

Fig.9 - Power dissipation test circuit.

Fig. 10 — Quiescent device current test circuit.

Fig. 14 -Input voltage test circuit.

Fig. 13 - Input current test circuit.

## CD4508B Types

Fig. 14 - Output disable test circuit and waveforms.

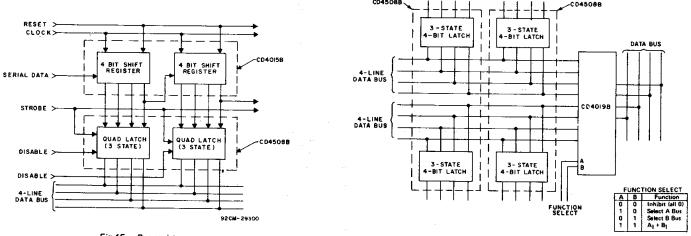

Fig. 15 - Bus register.

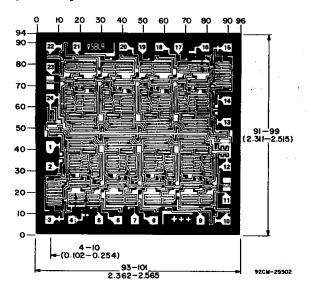

Dimensions in parentheses are in millimeters and are derived from the basic inch dimensions as indicated. Grid graduations are in mils (10<sup>-3</sup> inch).

Chip dimensions and pad layout for CD4508B.

Fig.16 — Dual multiplexed bus register with function select.

92CM - 29301

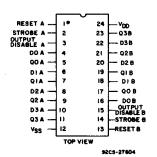

TERMINAL ASSIGNMENT

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated

Product Folder: CD4508B, CMOS Dual 4-Bit Latch

| Contact Us | Buy ⊿ | About TI 🗸 | TI Worldwide | my.TI |                |           | Search      | : Advanced Search |

|------------|-------|------------|--------------|-------|----------------|-----------|-------------|-------------------|

|            |       |            | Products 4   | P     | Applications 4 | Support 4 | Keyword     |                   |

|            |       |            |              |       |                |           | Part Number |                   |

PRODUCT FOLDER | PRODUCT INFO: FEATURES | DESCRIPTION | DATASHEETS | PRICING/AVAILABILITY/PKG | SAMPLES | APPLICATION NOTES | USER GUIDES | MORE LITERATURE

PRODUCT SUPPORT: TRAINING

#### CD4508B, CMOS Dual 4-Bit Latch

DEVICE STATUS: ACTIVE

PARAMETER NAME CD4508B

Voltage Nodes (V) 5, 10, 15

FEATURES ▲Back to Top

- · Two independent 4-bit latches

- · Individual master reset for each 4-bit latch

- · 3-state outputs with high-impedance state for bus line applications

- Medium-speed operation:  $t_{PHL} = t_{PLH} = 70$  ns (typ.) at  $V_{DD} = 10$  V and  $C_L = 50$  pF

- . 100% tested for quiescent current at 20 V

- 5-V, 10-V, and 15-V parametric ratings

- Standardized, symmetrical output characteristics

- Maximum input current of 1 uA at 18 V over full package-temperature range; 100 nA at 18 V and 25°C

- Noise margin (full package-temperature range) =

- 1 V at  $V_{DD} = 5 \text{ V}$

- 2 V at  $V_{DD} = 10 \text{ V}$

- $2.5 \text{ V at V}_{DD} = 15 \text{ V}$

- Meets all requirements of JEDEC Tentative Standard No. 13B, "Standard Specifications for Description of 'B' Series CMOS Devices"

- Applications:

- Buffer storage

- Holding registers

- Data storage and multiplexing

**DESCRIPTION** ▲Back to Top

CD4508B dual 4-bit latch contains two identical 4-bit latches with separate STROBE, RESET, and OUTPUT DISABLE control. With the STROBE line in the high state, the data on the "D" inputs appear at the corresponding "Q" outputs provided the DISABLE line is in the low state. Changing the STROBE line to the low state locks the data into the latch. A high on the reset line forces the outputs to a low level regardless of the state of the STROBE input. The outputs are forced to the high-impedance state for bus line applications by a high level on the DISABLE input.

The CD4508B types are supplied in the 24-lead dual-in-line ceramic packages (D and F suffixes), 24-lead dual-in-line plastic packages (E suffix), 24-lead small-outline package (NSR suffix), and in chip form (H suffix).

TECHNICAL DOCUMENTS

▲Back to Top

To view the following documents, Acrobat Reader 4.0 is required.

To download a document to your hard drive, right-click on the link and choose 'Save'.

DATASHEET ■ Back to Top

Full datasheet in Acrobat PDF: cd4508b.pdf (216 KB,Rev.A) (Updated: 03/18/2002)

APPLICATION NOTES

▲Back to Top

View Application Notes for Digital Logic

- Evaluation of Nickel/Palladium/Gold-Finished Surface-Mount Integrated Circuits (SZZA026 Updated: 06/20/2001)

- Understanding Buffered and Unbuffered CD4xxxB Series Device Characteristics (SCHA004 Updated: 12/03/2001)

Product Folder: CD4508B, CMOS Dual 4-Bit Latch

• Understanding and Interpreting Texas Instruments Standard-Logic Products Data Sh (Rev. A) (SZZA036A - Updated: 02/27/2003)

MORE LITERATURE

- Enhanced Plastic Portfolio Brochure (SGZB004, 387 KB Updated: 08/19/2002)

- Logic Reference Guide (SCYB004, 1032 KB Updated: 10/23/2001)

- MicroStar Junior BGA Design Summary (SCET004, 167 KB Updated: 07/28/2000)

- Military Brief (SGYN138, 803 KB Updated: 10/10/2000)

- Overview of IEEE Std 91-1984, Explanation of Logic Symbols Training Booklet (Rev. A) (SDYZ001A, 138 KB Updated: 07/01/1996)

- Palladium Lead Finish User's Manual (SDYV001, 2041 KB Updated: 11/01/1996)

- QML Class V Space Products Military Brief (Rev. A) (SGZN001A, 257 KB Updated: 10/07/2002)

USER GUIDES ▲Back to Top

- LOGIC Pocket Data Book (SCYD013, 4837 KB Updated: 12/05/2002)

- Signal Switch Data Book (SCDD003, 10259 KB Updated: 03/19/2001)

| SAMPLES          | ▲Back to Top                           |             |            |               |             |                             |                        |  |  |  |  |

|------------------|----------------------------------------|-------------|------------|---------------|-------------|-----------------------------|------------------------|--|--|--|--|

| ORDERABLE DEVICE | <u>PACKAGE</u><br><u>INDUSTRY (TI)</u> | <u>PINS</u> | TEMP (°C)  | <u>STATUS</u> | DSCC NUMBER | PRODUCT CONTENT             | SAMPLES                |  |  |  |  |

| CD4508BE         | PDIP<br>(N)<br>PDIP<br>(N)             | 24          | -55 TO 125 | ACTIVE        |             | <u>View Product Content</u> | <u>Request Samples</u> |  |  |  |  |

| PRICING/                         | PRICING/AVAILABILITY/PKG  ▲Back to Top |                                         |            |                |                    |                                                        |                    |              |                                                                |           |                                                   |          |          |

|----------------------------------|----------------------------------------|-----------------------------------------|------------|----------------|--------------------|--------------------------------------------------------|--------------------|--------------|----------------------------------------------------------------|-----------|---------------------------------------------------|----------|----------|

| <b>DEVICE INFO</b> Updated Daily |                                        |                                         |            |                |                    | TI INVENTORY STATUS<br>As Of 08:00 AM GMT, 17 Apr 2003 |                    |              | REPORTED DISTRIBUTOR INVENTORY As Of 08:00 AM GMT, 17 Apr 2003 |           |                                                   |          |          |

| ORDERABLE<br>DEVICE              | <u>STATUS</u>                          | PACKAGE<br>TYPE   PINS                  | TEMP (°C)  | DSCC<br>NUMBER | PRODUCT<br>CONTENT | BUDGETARY PRICING QTY   \$US                           | STD<br>PACK<br>QTY | IN STOCK     | IN PROGRESS<br>QTY   DATE                                      | LEAD TIME | DISTRIBUTOR<br>COMPANY   REGION                   | IN STOCK | PURCHASE |

| CD4508BD3                        | ACTIVE                                 | CDIP SB<br>(JD)<br>CDIP SB<br>(JD)   24 | -55 TO 125 |                | View Contents      | 1KU   20.92                                            | 1                  | <u>320</u> * | >10k   27 May                                                  | 8 WKS     | None Reported<br><u>View Distributors</u>         |          |          |

| CD4508BE                         | ACTIVE                                 | PDIP<br>(N)<br>PDIP<br>(N)              | -55 TO 125 |                | View Contents      | 1KU   1.36                                             | 15                 | <u>0</u> *   | 3000   15 May                                                  | 7 WKS     | <u>EBV</u>   Europe<br><u>Electronik</u>   Europe | >1k      | BUY NOW  |

|                                  |                                        |                                         |            |                |                    |                                                        |                    |              | >10k   16 May                                                  |           | <u>Avnet</u>   Americas                           | >1k      | BUY NOW  |

|                                  |                                        |                                         |            |                |                    |                                                        |                    |              |                                                                |           | Avnet-SILICA   Europe                             | 765      | BUY NOW  |

|                                  |                                        |                                         |            |                |                    |                                                        |                    |              |                                                                |           | <u>DigiKey</u>   Americas                         | 43       | BUY NOW  |

| CD4508BF3A                       | ACTIVE                                 | <u>CDIP</u><br>(J)   24                 | -55 TO 125 |                | View Contents      | 1KU   6.69                                             | 1                  | <u>304</u> * | 241   19 May                                                   | 8 WKS     | <u>Avnet</u>   Americas                           | 10       | BUY NOW  |

|                                  |                                        |                                         |            |                |                    |                                                        |                    |              | >10k   27 May                                                  |           | Avnet-SILICA   Europe                             | 2        | BUY NOW  |

| CD4508BNSR                       | ACTIVE                                 | <u>SOP</u><br>(NS)   24                 | -55 TO 125 |                | View Contents      | 1KU   1.40                                             | 2000               | <u>0</u> *   | 1422   05 May                                                  | 6 WKS     | None Reported<br>View Distributors                |          |          |

|                                  |                                        |                                         |            |                |                    |                                                        |                    |              | >10k   12 May                                                  |           |                                                   |          |          |

|                                  |                                        |                                         |            |                |                    |                                                        |                    |              |                                                                |           |                                                   |          |          |

Product Folder: CD4508B, CMOS Dual 4-Bit Latch

| CD4508BPW  | ACTIVE | <u>TSSOP</u>   2  | -55 TO 125 | View Contents | 1KU   1.40 | 60   | <u>0</u> * | 1441   01 May | 5 WKS | None Reported<br><u>View Distributors</u> |  |

|------------|--------|-------------------|------------|---------------|------------|------|------------|---------------|-------|-------------------------------------------|--|

|            |        |                   |            |               |            |      |            | >10k   08 May |       |                                           |  |

| CD4508BPWR | ACTIVE | TSSOP<br>(PW)   2 | Į.         | View Contents | 1KU   1.40 | 2000 | <u>0</u> * | >10k   08 May | 5 WKS | None Reported<br><u>View Distributors</u> |  |

Table Data Updated on: 4/17/2003

**Products** | **Applications** | **Support** | **my.TI**

© Copyright 1995-2002 Texas Instruments Incorporated. All rights reserved.

Trademarks | Privacy Policy | Terms of Use