# First-in First-out (FIFO) 2048 x 9 CMOS Memory

#### **FEATURES**

- First-in, First-out dual port memory

- 2048 x 9 organization

- Very high speed independent of depth/width 20ns cycle times

- · Asynchronous and simultaneous read and write

- · Fully expandable by both word depth and/or width

- Low power consumption

- Active: 150mA (max)

- Power Down: 15mA (max)

- · Half-full flag capability in standalone mode

- Empty and full warning flags

- · Auto retransmit capability in standalone mode

- High performance 1.2 micron CMOS technology

- Available in 300 mil and 600 mil Plastic DIP and 32 pin PLCC

#### DESCRIPTION

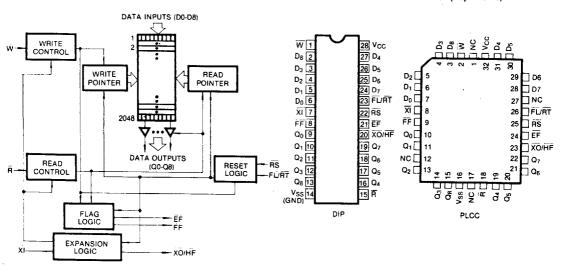

The KM75C03A is dual port memory that implements a special First-In, First-Out algorithm that loads and empties data on a first-in, first-out basis. Full and empty flags are provided to prevent data overflow. Expansion logic allows unlimited expansion capability in both word size and depth without any loss in speed.

No address information is required for KM75C03A. Ring counters automatically generate the addresses required for every read and write operations. Data is toggled in and out of the device through the use of  $WRITE(\overline{W})$  and  $READ(\overline{R})$  pins. The device has a read/write cycle time of 20nsec (50MHz).

The device consists of a 9-bit wide array which is very useful in applications such as data communications where it is necessary to use parity bit. The RETRANSMIT (RT) feature allows to re-read the previously read data. A half-full flag is available in the single device and width expansion modes.

The KM75C03A is fabricated using proprietary high speed CMOS 1.2 micron technology. It is designed for those applications requiring asynchronous and simultaneous read/writes in multiprocessing and rate buffer applications.

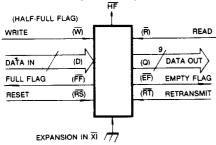

# FUNCTIONAL BLOCK DIAGRAM

# PIN CONFIGURATIONS (Top Views)

## ABSOLUTE MAXIMUM RATINGS

| Item                                                                                                                                                | Symbol                                    | Rating                                                            | Unit                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------|--------------------------|

| Voltage On Any Pin Relative to V <sub>ss</sub> Operating Temperature Temperature Under Bias Storage Temperature Power Dissipation DC Output Current | VIN<br>TA<br>Totas<br>Totag<br>PD<br>Jout | -0.5 to 7.0<br>0 to +70<br>-55 to +125<br>-65 to 150<br>1.0<br>50 | V<br>°C<br>°C<br>W<br>mA |

Note: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may effect device reliability.

# RECOMMENDED OPERATING CONDITIONS (Voltage referenced to Vss, TA = 0 to 70°C)

| Item               | Symbol            | Min | Тур | Max | Unit |

|--------------------|-------------------|-----|-----|-----|------|

| Supply Voltage     | , V <sub>cc</sub> | 4.5 | 5.0 | 5.5 | ٧    |

| Input High Voltage | V <sub>iH</sub>   | 2.0 |     |     | ٧    |

| Input Low Voltage  | V <sub>1L</sub>   |     |     | 0.8 | V    |

#### DC AND OPERATING CHARACTERISTICS (Vcc=5V ± 10%)

| er e e                                                                                        |                  |      |     |     |      | T <sub>A</sub> = 25ns |     | Unit  |

|-----------------------------------------------------------------------------------------------|------------------|------|-----|-----|------|-----------------------|-----|-------|

| Parameter                                                                                     | Symbol           | Min  | Тур | Max | Min  | Тур                   | Max | Junit |

| V <sub>cc</sub> Active Current                                                                | Icc              |      |     | 150 |      |                       | 120 | mA    |

| V <sub>CC</sub> Standby Current-TTL <sup>(1)</sup><br>(R = W = RS = FL/RT = V <sub>IH</sub> ) | I <sub>SB1</sub> |      |     | 15  |      |                       | 15  | mA    |

| V <sub>cc</sub> Standby Current-CMOS <sup>(1)</sup> (all inputs = V <sub>cc</sub> -0.2V)      | I <sub>SB2</sub> |      |     | 5   |      |                       | 5   | mA    |

| Input Leakage Current(2)                                                                      | lu               | -1   |     | 1   | -1   |                       | 1   | μА    |

| Output Leakage Current(3)                                                                     | ILO              | - 10 |     | 10  | - 10 |                       | 10  | μΑ    |

| Output High Voltage Level (I <sub>OH</sub> = -2mA)                                            | V <sub>OH</sub>  | 2.4  | ,   |     | 2.4  |                       |     | V     |

| Output Low Voltage Level (IoL = 8mA)                                                          | Vol              |      |     | 0.4 |      |                       | 0.4 | ٧     |

# DC AND OPERATING CHARACTERISTICS (Vcc = 5V ± 10%)

|                                                                                               | ,                |      | T <sub>A</sub> = 35ns | )   |      | T <sub>A</sub> = 50ns | 10/15/ | Unit |

|-----------------------------------------------------------------------------------------------|------------------|------|-----------------------|-----|------|-----------------------|--------|------|

| Parameter                                                                                     | Symbol           | Min  | Тур                   | Max | Min  | Тур                   | Max    |      |

| V <sub>CC</sub> Active Current                                                                | Icc              |      |                       | 100 |      |                       | 60     | mA   |

| V <sub>CC</sub> Standby Current-TTL <sup>(1)</sup><br>(R = W = RS = FL/RT = V <sub>IH</sub> ) | I <sub>SB1</sub> |      |                       | 15  |      |                       | 15     | mA   |

| V <sub>CC</sub> Standby Current-CMOS <sup>(1)</sup> (all inputs = V <sub>CC</sub> -0.2V)      | I <sub>SB2</sub> |      |                       | 5   |      |                       | 5      | mA   |

| input Leakage Current <sup>(2)</sup>                                                          | l <sub>Li</sub>  | -1   |                       | 1   | _1_  |                       | 1      | μΑ   |

| Output Leakage Current(3)                                                                     | ILO              | - 10 |                       | 10  | - 10 |                       | 10     | μΑ   |

| Output High Voltage Level (I <sub>OH</sub> = -2mA)                                            | V <sub>OH</sub>  | 2.4  |                       |     | 2.4  |                       |        | ٧    |

| Output Low Voltage Level (IoL = 8mA)                                                          | V <sub>OL</sub>  |      |                       | 0.4 |      |                       | 0.4    | V    |

Notes: 1. Icc and IsB measurements are made with outputs open.

- 2. Measurements with V<sub>SS</sub>≤V<sub>IN</sub>≤V<sub>CC</sub>.

- 3. R≥V<sub>IH</sub>, V<sub>SS</sub>≤V<sub>OUT</sub>≤V<sub>CC</sub>.

# AC ELECTRICAL CHARACTERISTICS (V<sub>CC</sub>=5V±10%, T<sub>A</sub>=0°C to + 70°C)

| B                                        | Combal               | KM750 | 03A-12 | KM750 | 03A-15 | KM750 | 03A-20 |      |

|------------------------------------------|----------------------|-------|--------|-------|--------|-------|--------|------|

| Parameter                                | Symbol               | Min   | Max    | Min   | Max    | Min   | Max    | Unit |

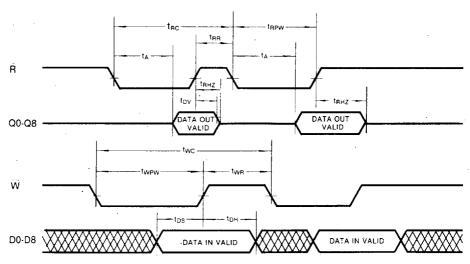

| Read Cycle Time                          | tRC                  | 20    |        | 25    |        | 30    |        | ns   |

| Access Time                              | tA                   |       | 12     |       | 15     | -     | 20     | ns   |

| Read Recovery Time                       | t <sub>RR</sub>      | 8     |        | 10    |        | 10    |        | ns   |

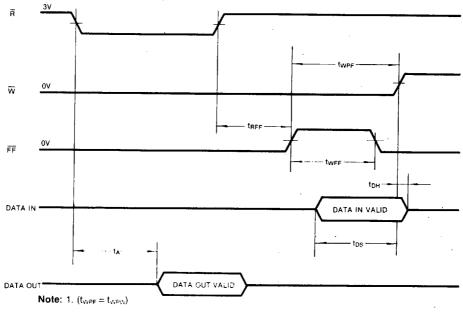

| Read Pulse Width(2)                      | tRPW                 | 12    |        | 15    |        | 20    |        | ns   |

| Data Valid from Read Pulse High          | t <sub>DV</sub>      | 5     |        | 5     |        | 5     |        | ns   |

| Read Pulse High to Data Bus at High-Z(3) | t <sub>RHZ</sub>     |       | 15     |       | 15     |       | 15     | ns   |

| Write Cycle Time                         | twc                  | 20    |        | 25    |        | 30    |        | ns   |

| Write Pulse Width(2)                     | twpw                 | 12    |        | 15    |        | 20    |        | ns   |

| Write Recovery Time                      | twR                  | 8     |        | 10    |        | 10    |        | ns   |

| Data Setup Time                          | tos                  | 8     |        | 10    |        | 12    |        | ns   |

| Data Hold Time                           | tрн                  | 0     |        | 0     |        | 0     |        | ns   |

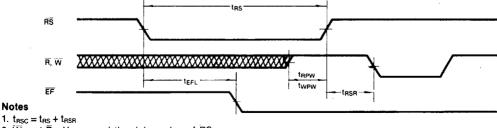

| Reset Cycle Time                         | trsc                 | 20    |        | 25    |        | 30    |        | ns   |

| Reset Pulse Width(2)                     | trs                  | 12    |        | 15    |        | 20    |        | ns   |

| Reset Recovery Time                      | trsr                 | 8     |        | 10    |        | 10    |        | ns   |

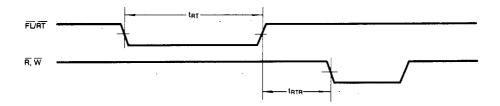

| Retransmit Cycle Time                    | tatc                 | 25    |        | 25    |        | 30    |        | ns   |

| Retransmit Pulse Width(2)                | t <sub>RT</sub>      | 15    |        | 15    |        | 20    |        | ns   |

| Retransmit Recovery Time                 | tere                 | 10    |        | 10    |        | 10    |        | ns   |

| Reset to Empty Flag Low                  | t <sub>EFL</sub>     |       | 20     |       | 25     |       | -30    | ns   |

| Reset to Half & Full Flag High           | then, teen           |       | 20     |       | 25     |       | 30     | ns   |

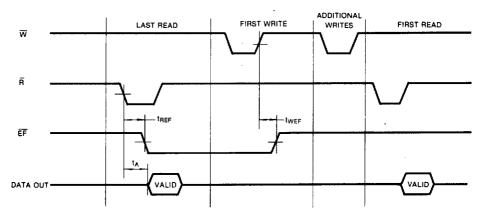

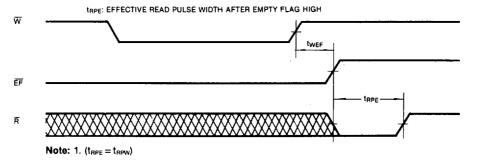

| Read Low to Empty Flag High              | t <sub>REF</sub>     |       | 20     |       | 20     |       | 20     | ns   |

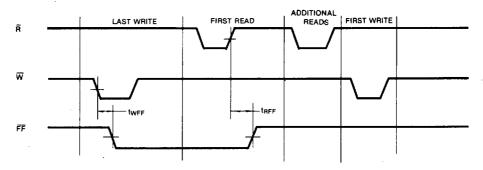

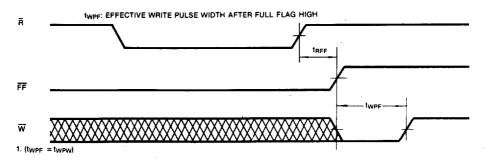

| Read High to Full Flag High              | tRFF                 |       | 20     |       | 20     |       | 20     | ns   |

| Write High to Empty Flag High            | twer                 |       | 20     |       | 20     |       | 20     | ns   |

| Write Low to Full Flag Low               | twee                 |       | 20     |       | 20     |       | 20     | ns   |

| Write Low to Half-Full Flag Low          | twhe                 |       |        |       | 25     |       | 30     | ns   |

| Read High to Half-Full Flag High         | tRHF                 |       |        |       | 25     |       | 30     | пѕ   |

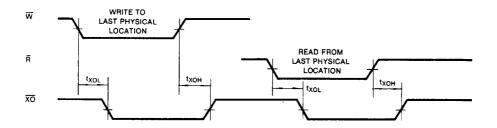

| Expansion Out Low Delay from Clock       | t xoL                |       | 16     |       | 20     |       | 20     | ns   |

| Expansion Out High Delay from Clock      | t <sub>XOH</sub> (4) |       | 16     |       | 20     |       | 20     | ns   |

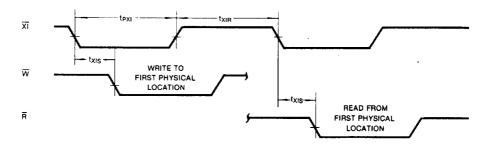

| XI Pulse Width                           | t <sub>PXI</sub>     | 12    |        | 15    |        | 20    |        | ns   |

| XI Recovery Time                         | txiR                 | 8     |        | 10    |        | 10    |        | ns   |

| XI Set-Up to Write or Clock              | txis                 | 8     |        | 10    |        | 12    |        | ns   |

# AC ELECTRICAL CHARACTERISTICS ( $V_{CC} = 5V \pm 10\%$ , $T_A = 0$ °C to +70°C)

|                                          |                                     | KM750 | 03A-25 | KM750 | 03A-35 | timie |  |

|------------------------------------------|-------------------------------------|-------|--------|-------|--------|-------|--|

| Parameter                                | Symbol                              | Min   | Max    | Min   | Max    | Unit  |  |

| Read Cycle Time                          | t <sub>RC</sub>                     | 35    |        | 45    |        | ns    |  |

| Access Time                              | tA                                  |       | - 25   |       | 35     | ns    |  |

| Read Recovery Time                       | tes                                 | 10    |        | 10    |        | ns    |  |

| Read Pulse Width <sup>(2)</sup>          | t <sub>RPW</sub>                    | 25    |        | 35    |        | ns    |  |

| Data Valid from Read Pulse High          | t <sub>DV</sub>                     | 5     |        | 5     |        | ns    |  |

| Read Pulse High to Data Bus at High-Z(1) | t <sub>RHZ</sub>                    |       | 20     |       | 20     | ns    |  |

| Write Cycle Time                         | twc                                 | 35    |        | 45    |        | ns    |  |

| Write Pulse Width <sup>(2)</sup>         | twpw                                | 25    |        | 35    |        | ns    |  |

| Write Recovery Time                      | twe                                 | 10    |        | 10    |        | ns    |  |

| Data Setup Time                          | tos                                 | 15    |        | 18    |        | ns    |  |

| Data Hold Time                           | t <sub>DH</sub>                     | 0     |        | 0.    |        | ns    |  |

| Reset Cycle Time                         | t <sub>RSC</sub>                    | 35    |        | 45    |        | ns    |  |

| Reset Pulse Width <sup>(2)</sup>         | t <sub>RS</sub>                     | 25    |        | 35    |        | ns    |  |

| Reset Recovery Time                      | t <sub>RSR</sub>                    | 10    |        | 10    |        | ns    |  |

| Retransmit Cycle Time                    | terro                               | 35    |        | 45    |        | ns    |  |

| Retransmit Pulse Width <sup>(2)</sup>    | t <sub>RT</sub>                     | 25    |        | 35    |        | ns    |  |

| Retransmit Recovery Time                 | t <sub>ATR</sub>                    | 10    |        | 10    |        | ns    |  |

| Reset to Empty Flag Low                  | terl                                |       | 35     |       | 45     | ns    |  |

| Reset to Half & Full Flag High           | t <sub>HFH</sub> , t <sub>FFH</sub> |       | 35     |       | 45     | ns    |  |

| Read Low to Empty Flag High              | t <sub>REF</sub>                    |       | 25     |       | 30     | ns    |  |

| Read High to Full Flag High              | t <sub>RFF</sub>                    |       | 25     |       | 30     | ns    |  |

| Write High to Empty Flag High            | t <sub>WEF</sub>                    |       | 25     |       | 30     | ns    |  |

| Write Low to Full Flag Low               | t <sub>WFF</sub>                    |       | 25     | ,     | 30     | ns    |  |

| Write Low to Half-Full Flag Low          | t <sub>WHF</sub>                    |       | 35     |       | 45     | ns    |  |

| Read High to Half-Full Flag High         | tene                                |       | 35     |       | 45     | ns    |  |

| Expansion Out Low Delay from Clock       | t <sub>xOL</sub>                    |       | 25     |       | 35     | ns    |  |

| Expansion Out High Delay from Clock      | t <sub>xoH</sub> <sup>(4)</sup>     |       | 25     |       | 35     | ns    |  |

| XI Pulse Width                           | t <sub>PXI</sub>                    | 25    |        | 35    |        | ns    |  |

| XI Recovery Time                         | t <sub>XIR</sub>                    | 10    |        | 10    |        | ns    |  |

| XI Set-Up to Write or Clock              | t <sub>xis</sub>                    | 15    |        | 15    |        | ns    |  |

# AC ELECTRICAL CHARACTERISTICS ( $V_{CC} = 5V \pm 10\%$ , $T_A = 0$ °C to +70°C)

|                                          | 0                                   | KM750   | C03A-50 | KM750 | 03A-80 | Unit |  |

|------------------------------------------|-------------------------------------|---------|---------|-------|--------|------|--|

| Parameter                                | Symbol                              | Min Max |         | Min   | Max    | Unit |  |

| Read Cycle Time                          | t <sub>RC</sub>                     | 65      |         | 100   |        | ns   |  |

| Access Time                              | tA                                  |         | 50      |       | 80     | ns   |  |

| Read Recovery Time                       | t <sub>RR</sub>                     | 15      |         | 20    |        | пѕ   |  |

| Read Pulse Width <sup>(2)</sup>          | t <sub>RPW</sub>                    | 50      |         | 80    |        | ns   |  |

| Data Valid from Read Pulse High          | t <sub>DV</sub>                     | 5       |         | 5     |        | пѕ   |  |

| Read Pulse High to Data Bus at High-Z(3) | t <sub>RHZ</sub>                    |         | 30      |       | 30     | ns   |  |

| Write Cycle Time                         | twc                                 | 65      |         | 100   |        | ns   |  |

| Write Pulse Width <sup>(2)</sup>         | twew                                | 50      |         | 80    |        | ns   |  |

| Write Recovery Time                      | t <sub>WB</sub>                     | 15      |         | 20    |        | ns   |  |

| Data Setup Time                          | t <sub>DS</sub>                     | 30      |         | 40    |        | ns   |  |

| Data Hold Time                           | t <sub>DH</sub>                     | 5       | Ţ       | 10    |        | ns   |  |

| Reset Cycle Time                         | t <sub>RSC</sub>                    | 65      | 1       | 100   |        | ns   |  |

| Reset Pulse Width(2)                     | t <sub>RS</sub>                     | 50      |         | 80    |        | ns   |  |

| Reset Recovery Time                      | t <sub>RSR</sub>                    | 15      |         | 20    |        | ns   |  |

| Retransmit Cycle Time                    | t <sub>RTC</sub>                    | 65      |         | 100   |        | ns   |  |

| Retransmit Pulse Width(2)                | t <sub>RT</sub>                     | 50      |         | 80    |        | ns   |  |

| Retransmit Recovery Time                 | tere                                | 15      |         | 20    |        | ns   |  |

| Reset to Empty Flag Low                  | t <sub>EFL</sub>                    |         | 65      |       | 100    | ns   |  |

| Reset to Half & Full Flag High           | t <sub>HFH</sub> , t <sub>FFH</sub> |         | 65      |       | 100    | ns   |  |

| Read Low to Empty Flag High              | t <sub>REF</sub>                    |         | 45      |       | 60     | ns   |  |

| Read High to Full Flag High              | t <sub>RFF</sub>                    |         | 45      |       | 60     | ns   |  |

| Write High to Empty Flag High            | t <sub>WEF</sub>                    |         | 45      |       | 60     | ns   |  |

| Write Low to Full Flag Low               | t <sub>WFF</sub>                    |         | 45      |       | 60     | ns   |  |

| Write Low to Half-Full Flag Low          | t <sub>WHF</sub>                    |         | 65      |       | 100    | ns   |  |

| Read High to Half-Full Flag High         | tans                                |         | 65      |       | 100    | ns   |  |

| Expansion Out Low Delay from Clock       | t <sub>xOL</sub>                    |         | 50      |       | 80     | ns   |  |

| Expansion Out High Delay from Clock      | t <sub>xoH</sub> (4)                |         | 50      |       | 65     | ns   |  |

| XI Pulse Width                           | t <sub>PXI</sub>                    | 50      |         | 80    |        | ns   |  |

| XI Recovery Time                         | t <sub>xiB</sub>                    | 15      |         | 20    |        | ns   |  |

| XI Set-Up to Write or Clock              | txis                                | 15      |         | 15    |        | ns   |  |

Notes: 1. Timings referenced as in AC Test Conditions

- 2. Pulse widths less than minimum value are not allowed.

- 3. Values guaranteed by design, not currently tested

- 4.  $t_{\text{XOH}}$  is guaranteed to be greater than or equal to  $t_{\text{XOL}}$  under all conditions.

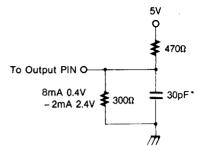

#### **AC TEST CONDITIONS**

| Input Pulse Levels                                    | GND to 3.0V  |

|-------------------------------------------------------|--------------|

| Input Rise and Fall Times                             | 5ns          |

| Input Timing Reference Levels                         | 1.5V         |

| Output Reference Levels                               | 1.5V         |

| Output Load                                           | See Figure 1 |

| Input Timing Reference Levels Output Reference Levels | 1.5V<br>1.5V |

**CAPACITANCE** ( $T_A = +25$ °C, f = 1.0MHz)

| Symbol          | Parameter          | Conditions                    | Тур | Unit |

|-----------------|--------------------|-------------------------------|-----|------|

| C <sub>IN</sub> | Input Capacitance  | $V_{IN} = 0V$                 | 5   | ρF   |

| Cout            | Output Capacitance | V <sub>OUT</sub> = <b>0</b> V | 7   | ρF   |

Note: This parameter is sampled and not 100% tested.

Figure 1. Output Load

\* INCLUDES JIG AND SCOPE CAPACITANCES

Note: Generation RW Signals-When using these high-speed FIFO devices, it is necessary to have clean inputs on the R and W signals. It is important not to have glitches, spikes or ringing on the R, W (that violate the  $V_{IL}$ ,  $V_{IH}$  requirements); although the minimum pulse width low for the  $\overline{R}$  and  $\overline{W}$  are specified in tens of nanosecond, a glitch of 3ns can affect the read or write pointer and cause it to increment.

## Master Reset (RS)

Reset is accomplished whenever the MASTER RESET (RS) input is taken to a low state. During this operation, both the internal read and the internal write pointers are set to the first FIFO location. A Master Reset pulse is required to initialize the FIFO after power-up before any write operation is performed. Both R and W inputs must be inactive for t<sub>RPW</sub> or t<sub>WPW</sub> before the rising edge of RS. and should not change for task after the rising edge of RS. Half-Full Flag (HF) will be set to inactive (high) level after master reset (RS).

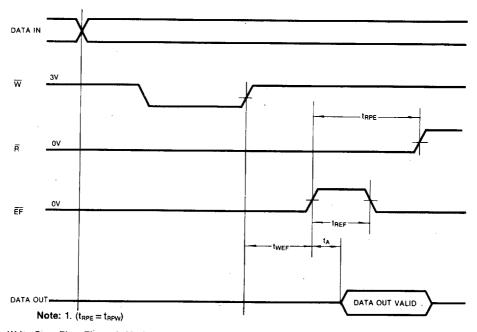

#### Read Enable (R)

READ cycles are initiated on the falling edge of the READ ENABLE (R) input provided that EMPTY-FLAG (EF) is not low. Read Cycles may be initiated asynchronously to any write operation in progress. After READ ENABLE (R) goes high, the data outputs will return to a high impedance condition until the next READ operation. If the FIFO is empty, the EMPTY-FLAG (EF) will go low and prevent any further read cycles. The data outputs will enter the high-impedance state after completion of the last read cycle.

#### Write Enable (W)

Figure 2. Reset

WRITE cycles may be initiated by a low signal at the

Winput provided the FULL-FLAG (FF) is not set. Data is stored in the memory array sequentially independent of any read operation that may be in progress.

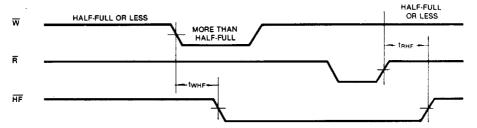

When more than half of the memory bytes have been filled, the HALF-FULL (HF) Flag output will be set low and will remain low till the difference between the write pointer and read pointer is less than or equal to one half of the total memory bytes of the device. The HALF-FULL flag is then reset by the rising edge of the read operation.

When the memory array is completely full, i.e., when the write pointer is one location from the read pointer, the FULL-FLAG (FF) will go low preventing any further write operations. The FULL-FLAG will go high again tage after completion of a valid read operation.

# First Load/Retransmit (FL/RT)

This input may be used in two different ways depending upon the configuration of EXPANSION-IN  $(\overline{XI})$ :

1. Single Device or Retransmit Mode: In this mode the XI pin must be grounded. Using this mode the device can be used to retransmit data when RT is pulsed low. A retransmit operation will set the internal read pointer

2.  $\overline{W}$  and  $\overline{R} = V_{IH}$  around the rising edge of RS.

SAMSUNG **ELECTRONICS**

to the first memory location in the array. The write pointer is unaffected. Both write enable and read enable must be inactive during the retransmit operation. This feature is particularly useful for FIFO applications in communications buffers where noise levels may be high and transmission errors are frequently detected. The retransmit feature may not be used along with depth expansion.

2. Depth Expansion Mode: In this mode the (FL/RT) pin is grounded it that device is the first of the "daisy chain." The FL pin is kept high if it is further down the chain. For details of Depth Expansion see Operating Modes.

## Expansion-In (XI)

This is a dual purpose input pin. As explained above,  $\overline{\text{XI}}$  is grounded to indicate single device mode operation. EXPANSION IN  $(\overline{\text{XI}})$  is connected to EXPANSION OUT  $(\overline{\text{XO}})$  of the previous device of the "daisy chain" in the Depth Expansion mode.

#### Full-Flag (FF)

The FULL-FLAG output goes low inhibiting further write operations when the write pointer is one memory location from the read pointer i.e., the memory array is full. The total length of he memory array is 2048 bytes write operations for the KM75C03A.

## Expansion Out/Half-Full Flag (XO/HF)

This output may be used in two different ways:

Figure 3. Asynchronous Write and Read Operation

Single Device Mode: In this mode this output acts as a HALF-FULL Flag. After half the memory locations are full, and at the falling edge of the next write operation, the HF output is set to low. It is reset to high if the difference between the write pointer and the read pointer is half the memory depth or less at the rising edge of the read operation.

**Depth Expansion Mode:** In this mode EXPANSION IN  $(\overline{XI})$  is connected to EXPANSION OUT  $(\overline{XO})$  of the previous device of the "daisy chain." In this way a signal can be passed onto the next device when the current device reaches the last memory location.

FIFO's can also be expanded simultaneously in depth and width to provide word widths greater than 9 in increments of 9. Consequently, any depth or width FIFO can be created. When expanding in depth, a composite FF must be created by OR-ing the FFs together. Likewise, a composite EF is created by OR-ing the EF's together. FF and FT functions are available in Depth Expansion Mode.

Single Device/Width Expansion Mode: Single Device and Width Expansion Modes are entered by grounding  $\overline{XI}$  during a MR cycle. During these modes the  $\overline{HF}$  and  $\overline{RT}$  features are available. FIFO's can be expanded in width to provide word widths greater than 9 in increments of 9. During Width Expansion Mode all control line inputs are common to all devices and flag outputs from any device can be monitored.

Figure 4. Full Flag From Last Write to First Read

Figure 5. Empty Flag From Last Read to First Write

Figure 6. Retransmit

#### Notes:

1.  $t_{RTC} = t_{RT} + t_{RTR}$

2. EF, HF, and FF may change state during retransmit as a result of the offset of the read and write pointers, but flags will be valid at t<sub>RTC</sub>.

Figure 7. Expansion In Timing Diagram

Figure 8. Expansion-Out Timing Diagram

Figure 9. Empty Flag Timing

Figure 10. Full Flag Timing

Figure 11. Half Full Flag Timing

# OPERATING MODES Single Device Mode

A single KM75C03A may be used when the application requirements are for 2048 words or less, the device is placed in a Single Device Configuration when the EXPANSION IN (XI) control input is grounded (See Figure 12). In this mode the HALF-FULL FLAG (HF) and RETRANSMIT (RT) features are available.

Figure 12. Block Diagram of Single 2048 x 9 FIFO

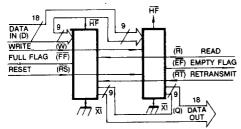

Figure 13. Block Diagram of 2048 x 18 FIFO Memory Used in Width Expansion Mode

Notes: Flag detection is accomplished by monitoring the FF, EF, and HF signals on either (any) device used in the width expansion configuration. Do not connect any output control signals together.

#### Width Expansion Mode

Word width may be increased simply by connecting the corresponding input control signals of multiple devices. Status flags (EF, FF and HF) can be detected from any one device. Figure 13 demonstrates an 18-bit word width by using two KM75C03A.

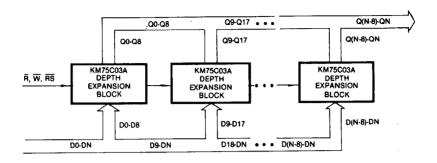

## Depth Expansion (Daisy Chain) Mode

The KM75C03A can easily be adapted to applications when the requirements are for greater than words. Figure 14 demonstrates Depth Expansion using three KM75C03A. Any depth can be attained by adding additional KM75C03A's. The KM75C03A operates in the Depth Expansion configuration when the following conditions are met:

The first device must be designed by grounding the FIRST LOAD (FL) control input. The RETRANSMIT feature is not available in this mode.

- 2. All other devices must have FL in the high state.

- The EXPANSION OUT (XO) pin of each device must be tied to the EXPANSION IN (XI) pin of the next device. The half-full flag (HF) function is not available in this mode.

- External logic is needed to generate a composite FULL FLAG (FF) and EMPTY FLAG (EF). This requires the OR-ing of all EFs and OR-ing of all FFs (i.e., all must be set to generate the correct composite FF or EF).

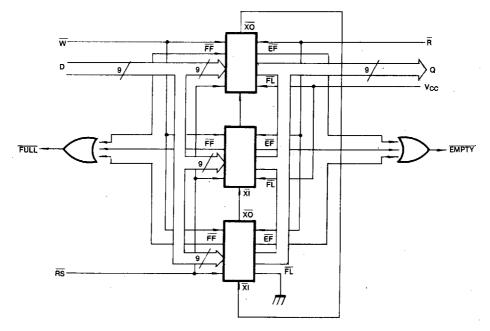

#### Compound Expansion Mode

The two expansion techniques described above can be applied together in a straightforward manner to achieve large FIFO arrays (See Figure 15).

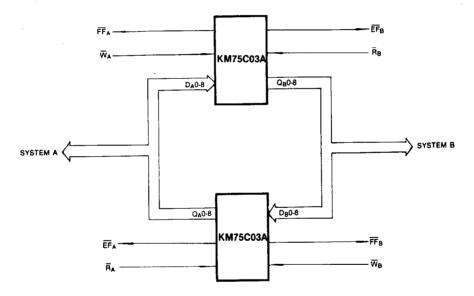

#### **Bidirection Mode**

Applications which required data buffering between two systems (each system capable of READ and WRITE operations), can be achieved by pairing KM75C03A as shown in Figure 16. Care must be taken to assure that the appropriate flag is monitored by each system; (i.e.,  $\overline{\text{FF}}$  is monitored on the device where  $\overline{\text{W}}$  is used;  $\overline{\text{EF}}$  is monitored on the device where  $\overline{\text{N}}$  is used). Both Depth Expansion and Width Expansion may be used in this mode.

#### **Data Flow-Through Modes**

This section describes two special conditions—when the FIFO is full or empty. For the read flow-through mode (Figure 17), the FIFO permits a reading of a single word after writing one word of data into an empty FIFO. The data is enabled on the bus in (tweef + ta) ns after the rising edge of W, called the first write edge, and it remains on the bus until the R line is raised from low-tohigh, after which the bus would go into a tri-state mode after  $t_{\text{RHZ}}$  ns. The  $\overline{\text{EF}}$  line would have a pulse showing temporary de-assertion and then would be asserted. In the interval of time that R was low, more words can be written to the FIFO (the subsequent writes after the first write edge would deassert the emptly flag); however, the same word (written the first write edge), presented to the output bus as the read pointer, would not be incremented when R is low. On toggling R, the other words that were written to the FIFO will appear on the output bus as in the read cycle timings.

In the write flow-through mode (Figure 18), the FIFO permits the writing of a single word of data immediately after reading one word of data (from a full FIFO. The  $\overline{\rm R}$  line causes the  $\overline{\rm FF}$  to be de-asserted but the  $\overline{\rm W}$  line being low causes it to be asserted again in anticipation of a new data word. On the rising edge of  $\overline{\rm W}$ , the new word is loaded in the FIFO. The  $\overline{\rm W}$  line must be toggled when  $\overline{\rm FF}$  is not asserted to write new data in the FIFO and to increment the write pointer.

#### **TRUTH TABLES**

Table 1. Reset and Retransmit-Single Device Configuration/Width Expansion Mode

| ***        |    | Inputs Internal Status |    |               |               |    | Outputs |    |

|------------|----|------------------------|----|---------------|---------------|----|---------|----|

| Mode       | RS | FL/RT                  | XI | Read Pointer  | Write Pointer | ĒF | FF      | HF |

| Reset      | 0  | Х                      | 0  | Location Zero | Location Zero | 0  | 1       | 1  |

| Retransmit | 1  | 0                      | 0  | Location Zero | Unchanged     | Х  | X       | Х  |

| Read/Write | 1  | 1                      | 0  | Increment (1) | Increment (1) | x  | Х       | Х  |

Note: 1. Pointer will increment if flag is high

Table 2. Reset and First Load Truth Table-Depth Expansion/Compound Expansion Mode

|            | Inputs |       | Interna | i Status      |               | puts |    |

|------------|--------|-------|---------|---------------|---------------|------|----|

| Mode       | RS     | FL/RT | Χī      | Read Pointer  | Write Pointer | EF   | HF |

| Reset      | 0      | 0     | (1)     | Location Zero | Location Zero | 0    | 1  |

| Retransmit | 0      | 1     | (1)     | Location Zero | Location Zero | 0    | 1  |

| Read/Write | 1      | Х,    | (1)     | X             | X             | Х    | Х  |

Note: 1.  $\overline{XI}$  is connected to  $\overline{XO}$  of previous device. See Figure 14.  $\overline{RS} = \text{Reset Input}$ ,  $\overline{FU}\overline{RT} = \text{First Load/Retransmit}$ ,  $\overline{EF} = \text{Empty Flag Output}$ ,  $\overline{FF} = \text{Full Flag Output}$ ,  $\overline{XI} = \text{Expansion Input}$ ,  $\overline{HF} = \text{Half-Full Flag Output}$ .

Figure 14. Block Diagram of 1536 x 9 FIFO Memory (Depth Expansion)

Figure 15. Compound FIFO Expansion

Figure 16. Bidirectional FIFO Mode

#### Notes:

- 1. For depth expansion block see DEPTH EXPANSION Section and Figure 14.

- 2. For detection see WIDTH EXPANSION Section and Figure 13.

Figure 17. Read Data Flow Through Mode

Figure 18. Write Data Flow Through Mode