# 048229

## **HS-C**<sup>2</sup>**MOS**<sup>™</sup> INTEGRATED CIRCUITS

### PRODUCT PREVIEW

# OCTAL BUS TRANSCEIVER 3-STATE DESCRIPTION

The M54/74HCT245 utilize silicon gate C2MOS technology to achieve operating speed equivalent to LSTTL parts.

Along with the low power dissipation and high noise immunity of standard CMOS integrated circuit, it has a fan-out of 15 LSTTL loads.

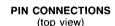

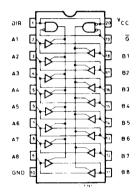

This IC' is intended for two-way asynchronous communication between data buses, the direction of data transmission being determined by the DIR

The enable input (G) can be used to disable the device so that the buses are effectively isolated. All inputs are equipped with protection circuits against static discharge or transient excess voltage. This integrated circuit has totally compatible, input and output characteristic, with standard 54/74 LSTTL logic families.

M54HCT/74HCT devices are desiged to directly interface HSC<sup>2</sup>MOS systems with TTL and NMOS components. These devices are also plug in replacements for LSTTL devices giving a reduction of power consumption.

#### **FEATURES**

- Low Power Dissipation  $I_{CC} = 4 \mu A \text{ (Max.)}$  at  $T_A = 25 \text{ °C}$

- High Noise Immunity  $V_{NIH} = V_{NIL} = 28\% V_{CC}$  (Min.)

- Output Drive Capability

15 LSTTŁ Loads

- Symmetrical Output Impedance

- $|I_{OH}| = I_{OL} = 6$  mA (Min.) • Balanced Propagation Delays

- t<sub>PLH</sub> = t<sub>PHL</sub>

Pin and Function compatible with 54/74LS245

### TRUTH TABLE

| INPUT |     | FUNCTION |        | OUTPUT |

|-------|-----|----------|--------|--------|

| G     | DIR | A BUS    | B BUS  |        |

| L     | L   | OUTPUT   | INPUT  | A = B  |

| L     | н   | INPUT    | OUTPUT | B= A   |

| Н     |     | Z        |        | Z      |

": "H" or "L"

Z: High Impedance

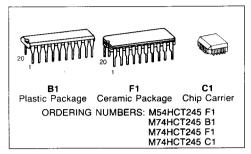

Dual in line

#### CHIP CARRIER

NC = No Internal Connection