# **Presettable BCD/Decade UP/Down Counter**

**ELECTRICALLY TESTED PER:** MII -M-38510/31507

The 54LS192 is an UP/DOWN BCD Decade (8421) Counter and the 54LS193 is an UP/DOWN MODULO-16 Binary Counter. Separate Count Up and Count Down Clocks are used and in either counting mode the circuits operate synchronously. The outputs change state synchronous with the LOW-to-HIGH transitions on the clock inputs.

Separate Terminal Count Up and Terminal Count Down outputs are provided which are used as the clocks for subsequent stages without extra logic, thus simplifying multistage counter designs. Individual preset inputs allow the circuits to be used as programmable counters. Both the Parallel Load (PL) and the Master Reset (MR) inputs asynchronously override the clocks.

- · Low Power . . . 95 mW Typical Dissipation

- High-Speed . . . 40 MHz Typical Count Frequency

- · Synchronous Counting

- · Asynchronous Master Reset and Parallel Load

- Cascading Circuitry Internally Provided

- Input Clamp Diodes Limit High-Speed Termination Effects

|     | Pin<br>Names                                   | Loading<br>(Note a) |             |  |  |

|-----|------------------------------------------------|---------------------|-------------|--|--|

|     | Names                                          | HIGH                | LOW         |  |  |

| СРО | Count UP Clock<br>Pulse Input                  | 0.5 U.L.            | 0.25 U.L.   |  |  |

| CPD | Count Down Clock<br>Pulse Input                | 0.5 U.L.            |             |  |  |

| MR  | Asynchronous<br>Master Reset                   | 0.5 U.L.            | 0.25 U.L.   |  |  |

| PL  | (Clear) Input<br>Asynchronous<br>Parallel Load | 0.5 U.L.            | 0.25 U.L.   |  |  |

| Pn  | (Active LOW) Input<br>Parallel Data<br>Inputs  | 0.5 U.L.            | 0.25 U.L.   |  |  |

| Qn  | Flip-Flop Outputs<br>(Note b)                  | 10 U.L.             | 5(2.5) U.L. |  |  |

| TCD |                                                | 10 U.L.             | 5(2.5) U.L. |  |  |

| TCU |                                                | 10 U.L.             | 5(2.5) U.L. |  |  |

### NOTES:

- a. One TTL Unit Load (U.L.) = 40 µA HIGH/ 1.6 mA LOW.

- b. The Output LOW drive factor is 2.5 U.L. for Military (54) Temperature Ranges.

# STATE DIAGRAM

### LS192 LOGIC EQUATIONS FOR **TERMINAL COUNT**

$\overline{TC}_U = Q_0 \cdot Q_3 \cdot \overline{CP}_U$   $\overline{TC}_D = \overline{Q}_0 \cdot \overline{Q}_1 \cdot \overline{Q}_2 \cdot \overline{Q}_3 \cdot \overline{CP}_D$

# Military 54LS192

### AVAILABLE AS:

1) JAN: JM38510/31507BXA

2) SMD: 7603601

3) 883: 54LS192/BXAJC

X = CASE OUTLINE AS FOLLOWS: PACKAGE: CERDIP: E

**CERFLAT: F**

THE LETTER "M" APPEARS BEFORE THE / ON LCC.

|                 | PIN ASSIGNMENTS |                 |                |                      |  |  |  |  |  |

|-----------------|-----------------|-----------------|----------------|----------------------|--|--|--|--|--|

| FUNCT.          | DIL<br>620-09   | FLATS<br>650-05 | LCC<br>756A-02 | BURN-IN<br>(COND. A) |  |  |  |  |  |

| P <sub>1</sub>  | 1               | 1               | 2              | Vcc                  |  |  |  |  |  |

| Q <sub>1</sub>  | 2               | 2               | 3              | VCC                  |  |  |  |  |  |

| $\sigma_0$      | 3               | 3               | 4              | VCC                  |  |  |  |  |  |

| CPD             | 4               | 4               | 5              | VCC                  |  |  |  |  |  |

| CPU             | 5               | 5               | 7              | VCC                  |  |  |  |  |  |

| $Q_2$           | 6               | 6               | 8              | VCC                  |  |  |  |  |  |

| Q <sub>3</sub>  | 7               | 7               | 9              | Vcc                  |  |  |  |  |  |

| GND             | 8               | 8               | 10             | GND                  |  |  |  |  |  |

| P <sub>3</sub>  | 9               | 9               | 12             | VCC                  |  |  |  |  |  |

| P <sub>2</sub>  | 10              | 10              | 13             | VCC                  |  |  |  |  |  |

| PL              | 11              | 11              | 14             | GND                  |  |  |  |  |  |

| TCU             | 12              | 12              | 15             | OPEN                 |  |  |  |  |  |

| ŤC <sub>D</sub> | 13              | 13              | 17             | VCC                  |  |  |  |  |  |

| MR              | 14              | 14              | 18             | GND                  |  |  |  |  |  |

| P <sub>0</sub>  | 15              | 15              | 19             | VCC                  |  |  |  |  |  |

| VCC             | 16              | 16              | 20             | VCC                  |  |  |  |  |  |

**BURN-IN CONDITIONS:**  $V_{CC} = 5.0 \text{ V MIN/6.0 V MAX}$

|    | MODE SELECT TABLE |     |     |                |  |  |  |  |  |  |  |

|----|-------------------|-----|-----|----------------|--|--|--|--|--|--|--|

| MR | ΡL                | CPU | CPD | MODE           |  |  |  |  |  |  |  |

| Н  | X                 | X   | X   | Reset (Asyn.)  |  |  |  |  |  |  |  |

| -  | l ∟ ∣             | X   | Х   | Preset (Asyn.) |  |  |  |  |  |  |  |

| L  | н                 | н   | н   | No Change      |  |  |  |  |  |  |  |

| L  | н                 |     | н   | Count Up       |  |  |  |  |  |  |  |

| L  | Н                 | н   | ۲   | Count Down     |  |  |  |  |  |  |  |

L = LOW Voltage Level

H = HiGH Voltage Level

X = Don't Care

### **FUNCTIONAL DESCRIPTION**

The 'LS192 and 'LS193 are Asynchronously Presettable Decade and 4-Bit Binary Synchronous UP/DOWN (Reversable) Counters. The operating modes of the 'LS192 decade counter and 'LS193 binary counter are identical, with the only difference being the count sequences as noted in the State Diagrams. Each circuit contains four master/slave flip-flops, with internal gating and steering logic to provide master reset, individual preset, count up and count down operations

Each flip-flop contains JK feedback from slave to master such that a LOW-to-HIGH transition on its T input causes the slave, and thus the Q output to change state. Synchronous switching, as opposed to ripple counting, is achieved by driving the steering gates of all stages from a common Count Up line and a common Count Down line, thereby causing all state changes to be initiated simultaneously. A LOW-to-HIGH transition on the Count Up input will advance the count by one; a similar transition on the Count Down input will decrease the count by one. While counting with one clock input, the other should be held HIGH. Otherwise, the circuit will either count by twos or not at all, depending on the state of the first flip-flop, which cannot toggle as long as either Clock input is LOW.

The Terminal Count Up  $(\overline{TC}_U)$  and Terminal Count Down  $(\overline{TC}_D)$  outputs are normally HIGH. When a circuit has reached the maximum count state (9 for the 'LS192, 15 for the 'LS193), the next HIGH-to-LOW transition of the Count Up Clock will cause  $\overline{TC}_U$  to go LOW.  $\overline{TC}_U$  will stay LOW until CPU goes HIGH again, thus effectively repeating the Count Up Clock, but delayed by two gate delays. Similarly, the  $\overline{TC}_D$  output will go LOW when the circuit is in the zero state and the Count Down Clock goes LOW. Since the TC outputs repeat the clock waveforms, they can be used as the clock input signals to the next higher order circuit in a multistage counter.

Each circuit has an asynchronous parallel load capability permitting the counter to be preset. When the Parallel Load  $(\overline{PL})$  and the Master Reset (MR) inputs are LOW, information present on the Parallel Data inputs  $(P_0,P_3)$  is loaded into the counter and appears on the outputs regardless of the conditions of the clock inputs. A HIGH signal on the Master Reset input will disable the preset gates, override both Clock inputs, and latch each Q output in the LOW state. If one of the Clock inputs is LOW during and after a reset or load operation, the next LOW-to-HIGH transition of that Clock will be interpreted as a legitimate signal and will be counted.

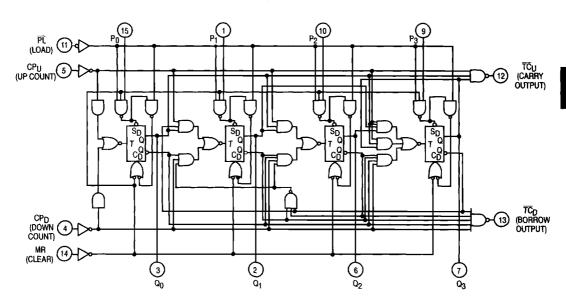

### LOGIC DIAGRAM

### 54LS192

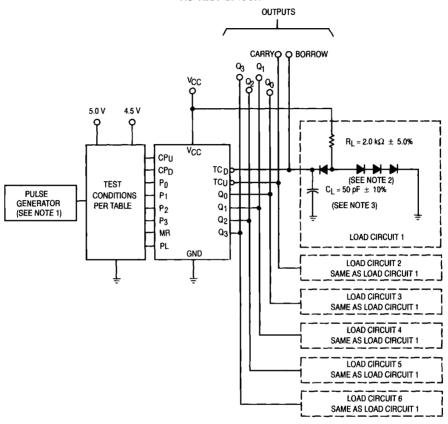

### **AC TEST CIRCUIT**

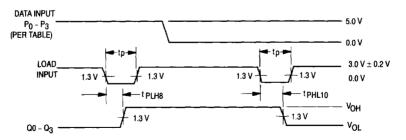

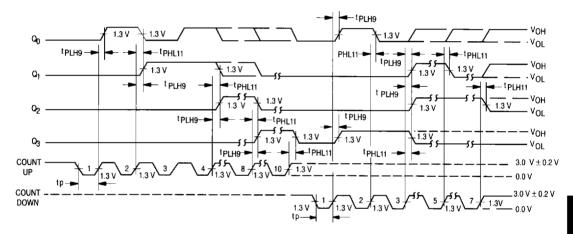

### WAVEFORMS

REFERENCE NOTES ON PAGE 5-265

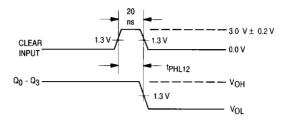

### **CLEAR SWITCHING VOLTAGE WAVEFORM**

### SERIAL LOADED VOLTAGE WAVEFORMS

### NOTES:

- 1. The load and count pulse generators have the following characteristics:  $V_{\mbox{gen}} = 3.0 \ \mbox{V, t}_p = 0.5 \ \mbox{µs, t}_r \leq 15 \ \mbox{ns, t}_f \leq 6.0 \ \mbox{ns}$  between 0.7 V and 2.7 V and PRR  $\leq$  1.0 MHz, Z\_OUT = 50  $\Omega$ .

- 2. All diodes are 1N3064, or equivalent.

- 3.  $C_{I} = 50 \text{ pF} \pm 10\%$  (including jig and probe capacitance).

- 4. Voltage values are with respect to ground terminal.

- 5.  $f_{MAX}$ :  $t_r = t_f \le 6.0 \text{ ns.}$

- 6. The clear pulse generator has the following characteristics:  $V_{gen}=3.0 \text{ V, } t_f \leq 15 \text{ ns, } t_f \leq 6.0 \text{ ns between } 0.7 \text{ V and } 2.7 \text{ V, } t_{w(clear)}=20 \text{ ns.}$

- 7.  $R_L = 2.0 \text{ k}\Omega \pm 5.0\%$ .

| Symbol          | Parameter Static Parameters:    |       | Limits               |       |                       |             |                      | Unit        | Test Condition (Unless Otherwise Specified)                                                                                                                                                    |  |                                                                                                          |

|-----------------|---------------------------------|-------|----------------------|-------|-----------------------|-------------|----------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|----------------------------------------------------------------------------------------------------------|

|                 |                                 | + 25  | + 25°C<br>Subgroup 1 |       | + 125°C<br>Subgroup 2 |             | - 55°C<br>Subgroup 3 |             | <del></del>                                                                                                                                                                                    |  |                                                                                                          |

|                 |                                 | Subgr |                      |       |                       |             |                      |             |                                                                                                                                                                                                |  |                                                                                                          |

|                 |                                 | Min   | Max                  | Min   | Max                   | Min         | Max                  |             |                                                                                                                                                                                                |  |                                                                                                          |

| Vон             | Logical "1"<br>Output Voltage   | 2.5   |                      | 2.5   | _                     | 2.5         |                      | v           | $V_{CC}$ = 4.5 V, $I_{OH}$ = $-$ 0.4 mA, $V_{IN}$ = 2.0 V, other inputs are open, MR & $\overline{PL}$ = 0.7 V.                                                                                |  |                                                                                                          |

| v <sub>OL</sub> | Logical "0"<br>Output Voltage   |       | 0.4                  |       | 0.4                   |             | 0.4                  | ٧           | $\begin{split} &V_{CC}=4.5 \text{ V, } I_{OL}=4.0 \text{ mA, } V_{IN}=0.7 \text{ V,} \\ &\text{other inputs are open,} \\ &P_0, P_3 \& \text{MR}=0.7 \text{ V or } 2.0 \text{ V.} \end{split}$ |  |                                                                                                          |

| V <sub>IC</sub> | Input Clamping<br>Voltage       |       | -1.5                 |       |                       |             |                      | V           | V <sub>CC</sub> = 4.5 V, I <sub>IN</sub> = -18 mA, other inputs are open.                                                                                                                      |  |                                                                                                          |

| liн             | Logical "1"<br>Input Current    |       | 20                   |       | 20                    |             | 20                   | μА          | $V_{CC}$ = 5.5 V, $V_{IH}$ = 2.7 V, other inputs are open, MR & $\overline{PL}$ = 5.5 V or 2.7 V.                                                                                              |  |                                                                                                          |

| Інн             | Logical "1"<br>Input Current    |       | 100                  |       | 100                   |             | 100                  | μΑ          | V <sub>CC</sub> = 5.5 V, V <sub>IN</sub> = 5.5 V, other inputs are open.                                                                                                                       |  |                                                                                                          |

| IIL             | Logical "0"<br>Input Current    | - 120 | - 360                | 120   | - 360                 | - 120       | - 360                | μА          | V <sub>CC</sub> = 5.5 V, V <sub>IN</sub> = 0.4 V,<br>PL & MR = GND, other inputs are open.                                                                                                     |  |                                                                                                          |

| ΊL              | Logical "0"<br>Input Current    | - 120 | - 360                | - 120 | -360                  | - 120       | - 360                | μА          | $V_{CC} = 5.5 \text{ V}, V_{IN} = 0.4 \text{ V} (\overline{PL}),$ other inputs are open.                                                                                                       |  |                                                                                                          |

| կլ              | Logical "0"<br>Input Current    | - 120 | - 360                | - 120 | -360                  | - 120       | - 360                | μА          | $V_{CC} = 5.5 \text{ V}, V_{IN} = 0.4 \text{ V} (\overline{TC} \& MR),$ other inputs are open.                                                                                                 |  |                                                                                                          |

| los             | Output Short<br>Circuit Current | -15   | - 100                | -15   | -100                  | -15         | - 100                | mA          | $V_{CC} = 5.5 \text{ V}, V_{IN} = 5.5 \text{ V},$<br>other inputs are open, $V_{OUT} = \text{GND}.$                                                                                            |  |                                                                                                          |

| lcc             | Power Supply<br>Current Off     |       | 34                   |       | 34                    |             | 34                   | mA          | V <sub>CC</sub> = 5.5 V, V <sub>IN</sub> = GND ( <del>PL</del> & MR), other inputs are open.                                                                                                   |  |                                                                                                          |

| VIH             | Logical "1"<br>Input Voltage    | 2.0   | _                    | 2.0   |                       | 2.0         |                      | ٧           | V <sub>CC</sub> = 4.5 V.                                                                                                                                                                       |  |                                                                                                          |

| V <sub>IL</sub> | Logical "0"<br>Input Voltage    |       | 0.7                  |       | 0.7                   |             | 0.7                  | ٧           | V <sub>CC</sub> = 4.5 V.                                                                                                                                                                       |  |                                                                                                          |

|                 | Functional Tests                | Subg  | roup 7               | Subgr | oup 8A                | Subgroup 8B |                      | Subgroup 8B |                                                                                                                                                                                                |  | per Truth Table with V <sub>CC</sub> = 4.5 V,<br>V <sub>INL</sub> = 0.4 V, and V <sub>INH</sub> = 2.5 V. |

| Symbol                                   | Parameter                                            | Limits     |                  |             |          |             | Unit     | Test Condition<br>(Unless Otherwise Specified) |                                                                                                                             |

|------------------------------------------|------------------------------------------------------|------------|------------------|-------------|----------|-------------|----------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

|                                          |                                                      | + 2        | 5°C              | + 12        | !5°C     | – 55°C      |          |                                                |                                                                                                                             |

|                                          | Switching<br>Parameters:                             | Subgroup 9 |                  | Subgroup 10 |          | Subgroup 11 |          | ]                                              |                                                                                                                             |

|                                          |                                                      | Min        | Max              | Min         | Max      | Min         | Max      |                                                |                                                                                                                             |

| <sup>†</sup> PHL10<br><sup>†</sup> PHL10 | Propagation Delay /Data-Output PL to Q Outputs       | 3.0        | 45<br>40         | 3.0         | 63<br>58 | 3.0         | 63<br>58 | ns                                             | $V_{CC} = 5.0 \text{ V}, C_L = 50 \text{ pF}, R_L = 2.0 \text{ ks}.$<br>$V_{CC} = 5.0 \text{ V}, C_L = 15 \text{ pF}.$      |

| <sup>†</sup> PLH8<br><sup>†</sup> PLH8   | Propagation Delay<br>/Data-Output<br>PL to Q Outputs | 3.0        | 45<br><b>4</b> 0 | 3.0         | 63<br>58 | 3.0         | 63<br>58 | ns                                             | $V_{CC} = 5.0 \text{ V}, C_L = 50 \text{ pF}, R_L = 2.0 \text{ k}\Omega.$ $V_{CC} = 5.0 \text{ V}, C_L = 15 \text{ pF}.$    |

| <sup>†</sup> PHL11<br>†PHL11             | Propagation Delay<br>CPD or CPU<br>to Q Outputs      | 3.0        | 52<br>47         | 3.0         | 72<br>68 | 3.0         | 72<br>68 | ns                                             | $V_{CC} = 5.0 \text{ V}, C_L = 50 \text{ pF}, R_L = 2.0 \text{ ks}.$<br>$V_{CC} = 5.0 \text{ V}, C_L = 15 \text{ pF}.$      |

| <sup>†</sup> PLH9<br>†PLH9               | Propagation Delay<br>CPD or CPU<br>to Q Outputs      | 3.0        | 43<br>38         | 3.0         | 60<br>55 | 3.0         | 60<br>55 | ns                                             | $V_{CC} = 5.0 \text{ V. C}_L = 50 \text{ pF, R}_L = 2.0 \text{ k}\Omega$ . $V_{CC} = 5.0 \text{ V, C}_L = 15 \text{ pF.}$   |

| <sup>†</sup> PHL12<br><sup>†</sup> PHL12 | Propagation Delay<br>MR (Clear)<br>to Q Outputs      | 3.0        | 40<br>35         | 3.0         | 56<br>51 | 3.0         | 56<br>51 | ns                                             | $V_{CC} = 5.0 \text{ V}, C_L = 50 \text{ pF}, R_L = 2.0 \text{ k}\Omega.$<br>$V_{CC} = 5.0 \text{ V}, C_L = 15 \text{ pF}.$ |

| <sup>†</sup> PHL13<br><sup>†</sup> PHL13 | Propagation Delay<br>Counter to Carry                | 3.0        | 29               | 3.0         | 41       | 3.0         | 41       | ns                                             | $V_{CC} = 5.0 \text{ V}, C_L = 50 \text{ pF}, R_L = 2.0 \text{ k}\Omega.$                                                   |

| <sup>t</sup> PLH13<br><sup>t</sup> PLH13 | Propagation Delay<br>Counter to Carry                | 3.0        | 31               | 3.0         | 45       | 3.0         | 45       | ns                                             | $V_{CC} = 5.0 \text{ V}, C_L = 50 \text{ pF}, R_L = 2.0 \text{ k}\Omega.$                                                   |

| tPHL14<br>tPHL14                         | Propagation Delay<br>Counter to Carry                | 3.0        | . 29             | 3.0         | 41       | 3.0         | 41       | ns                                             | $V_{CC} = 5.0 \text{ V}, C_L = 50 \text{ pF}, R_L = 2.0 \text{ k}\Omega.$                                                   |

| <sup>t</sup> PLH14<br><sup>t</sup> PLH14 | Propagation Delay<br>Counter to Carry                | 3.0        | 29               | 3.0         | 45       | 3.0         | 45       | ns                                             | $V_{CC} = 5.0 \text{ V}, C_L = 50 \text{ pF}, R_L = 2.0 \text{ k}\Omega.$                                                   |

| <sup>†</sup> MAX                         | Input Clock<br>Frequency                             | 22         |                  | 22          |          | 22          |          | MHz                                            | $V_{CC} = 5.0 \text{ V}, C_L = 50 \text{ pF}, R_L = 2.0 \text{ k}\Omega.$                                                   |

| <sup>f</sup> MAX                         | Input Clock<br>Frequency                             | 25         |                  |             |          |             |          | MHz                                            | V <sub>CC</sub> = 5.0 V, C <sub>L</sub> = 15 pF.                                                                            |

## NOTE:

<sup>1.</sup> The limit specified for  $C_L$  = 15 pF are guaranteed but not tested.