## GM16C450/82C50A **ASYNCHRONOUS** COMMUNICATIONS ELEMENT

## **General Description**

The GM16C450 is an improved specification version of the GM82C50A Asynchronous Communications Element (ACE). The improved specifications ensure compatibility with state-of-the-art CPUs. Functionally, the

GM16C450 is equivalent to the GM82C50A. The GM16C450 and GM82C50A each function as a serial data input/output interface in a microcomputer system. The functional configuration of the ACEs is programmed by the system software via a 3-state 8-bit bidirectional data bus; this includes the on-board baud

rate generator.

The ACE performs serial-to-parallel conversion on data characters received from a peripheral device or a modem, and parallel-to-serial conversion on data characters received from the CPU. The CPU can read the complete status of the ACE at any time during the functional operation. Status information reported includes the type and condition of the transfer opera-tions being performed by the ACE, as well as any error conditions (parity, overrun, framing or break interrupt). The ACE includes a programmable baud generator that is capable of dividing the timing reference clock input by a divisor between 1 and (2 to the power of 16 -1), and producing a 16x clock for driving the internal transmitter logic. Provisions are also include to use this 16x clock to drive the receiver logic. Also included in the ACE is a complete modern control capability, and a processor-interrupt system that may be software tailored to the user's requirements to minimize the computing required to handle the communications In additional, the GM16C450/GM82C50A runs at a

#### **Features**

- · Easily interfaces to most popular microproces-

- Adds or deletes standard asynchronous communication bits (start, stop and parity) to or from serial data stream

- Full double-buffering eliminates need for precise synchronization

. Independently controlled transmit, receive, line status and data set interrupts

Programmable baud generator allows division of any input clock by 1 to (2 to the power of 16 - 1) and génerates the internal 16x clock

Independent receiver clock input

- Moderm control functions (CTS, RTS, DSR, DTR, Fl and DCD)

- Fully programmable serial interface characteristics:

- 5-, 6-, 7- or 8-bit characters

- Even-, odd- or no-parity bit generation and

- 1-, 1.5- or 2-stop bit generation

Baud generation (DC to 56k baud)

False start bit detection

- Complete status reporting capabilities

3-state TTL drive capabilities for bidirectional

. Internal diagnostic capabilities:

- Loopback controls for communications link fault isolation

- Break, parity, overrun, framing error simula-- Fully prioritized interrupt system controls

- Compatible with PS/2 system speed data bus and control bus

- . Line break generation and detection

## Pin Configuration

maximum speed of 16 MHz.

\*On the GM82 C50A, PIN38(PIN42 on the PLCC PACKAGE) is also called RLSD

## 1.0 Absolute Maximum Ratings

Temperature Under Bias

0°C to + 70°C

Storage Temperature

**Power Dissipation**

-65°C to +150°C

All Input or Output Voltages with Respect to √SS

-0.5V to +7.0V

700 mW

Note: Maximum ratings indicate limits beyond which permanent damage may occur. Continuous operation at these limits is not intended and should be limited to those conditions specified under DC electrical characteristics.

## 2.0 DC Electrical Characteristics

$T_A = 0^{\circ}C$  to +70°C,  $V_{CC} = +5V \pm 5\%$ ,  $V_{SS} = 0V$ , unless otherwise specified.

| Symbol               | Parameter                                       | Conditions                                                                                                                                                                | GM16 | C450 | GM82 | C50A | Units |

|----------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

|                      |                                                 |                                                                                                                                                                           | Min  | Max  | Min  | Max  | 7     |

| V <sub>ILX</sub>     | Clock Input Low Voltage                         |                                                                                                                                                                           | 0.5  | 0.8  | -0.5 | 0.8  | V     |

| V <sub>IHX</sub>     | Clock Input High Voltage                        |                                                                                                                                                                           | 2.0  | Vcc  | 2.0  | Vcc  | V     |

| V <sub>IL</sub>      | Input Low Voltage                               |                                                                                                                                                                           | -0.5 | 0.8  | -0.5 | 0.8  | V     |

| VIH                  | Input High Voltage                              |                                                                                                                                                                           | 2.0  | Vcc  | 2.0  | Vcc  | V     |

| V <sub>OL</sub>      | Output Low Voitage                              | I <sub>OL</sub> = 1.6 mA on all (Note 2)                                                                                                                                  |      | 0.4  |      | 0.4  | V     |

| VoH                  | Output High Voltage                             | I <sub>OH</sub> = -1.0 mA (Note 2)                                                                                                                                        | 2.4  |      | 2.4  |      | V     |

| I <sub>CC</sub> (AV) | Avg. Power Supply<br>Current (V <sub>CC</sub> ) | V <sub>CC</sub> = 5.25V, T <sub>A</sub> = 25°C  No Loads on output SIN, DSR, DCD, CTS, RI = 2.4V  All other inputs = 0.4V  Baud Rate Generator at 4 MHz  Baud Rate at 50k |      | 10   |      | 10   | mA    |

| i <sub>IL</sub>      | Input Leakage                                   | V <sub>CC</sub> = 5.25V, V <sub>SS</sub> = 0V<br>All other pins floating.                                                                                                 |      | ± 10 |      | ± 10 | μА    |

| <sup>I</sup> CL      | Clock Leakage                                   | V <sub>IN</sub> ≈ 0V, 5.25V                                                                                                                                               |      | ± 10 |      | ± 10 | μΑ    |

| loz                  | TRI-STATE Leakage                               | V <sub>CC</sub> = 5.25V, V <sub>SS</sub> = 0V<br>V <sub>OUT</sub> = 0V, 5.25V<br>1) Chip deselected<br>2) WRITE mode,<br>chip selected                                    |      | ± 20 |      | ± 20 | μΑ    |

| VILMR                | MR Schmitt VIL                                  |                                                                                                                                                                           |      | 0.8  |      | 0.8  | V     |

| VIHMR                | MR Schmitt VIH                                  | 1                                                                                                                                                                         | 2.0  |      | 2.0  |      | ٧     |

### Capacitance $T_A = 25^{\circ}C, V_{CC} = V_{SS} = 0V$

| Symbol            | Parameter                | Conditions                  | Min | Тур | Max | Units |

|-------------------|--------------------------|-----------------------------|-----|-----|-----|-------|

| CXIN              | Clock Input Capacitance  |                             |     | 15  | 20  | pF    |

| C <sub>XOUT</sub> | Clock Output Capacitance | f <sub>C</sub> = 1 MHz      |     | 20  | 30  | ρF    |

| C <sub>IN</sub>   | Input Capacitance        | Unmeasured pins             |     | 6   | 10  | pF    |

| Соит              | Output Capacitance       | returned to V <sub>SS</sub> |     | 10  | 20  | pF    |

Note 1: Inputs on the CMOS parts are TTL compatible; outputs on the CMOS parts drive to GNL and V<sub>CC</sub>.

Note 2: Does not apply to XOUT

٠٠٦

## 3.0 AC Electrical Characteristics $T_A = 0$ °C to +70°C, $V_{CC} = +5V \pm 5$ %

| Symbol            | Parameter                                                         | Conditions                               | GM 1 | 6C450       | 450 GM 8   |          | Unite                   |

|-------------------|-------------------------------------------------------------------|------------------------------------------|------|-------------|------------|----------|-------------------------|

| ]                 | . =.=                                                             |                                          | Min  | Max         | Min        | Max      | 7                       |

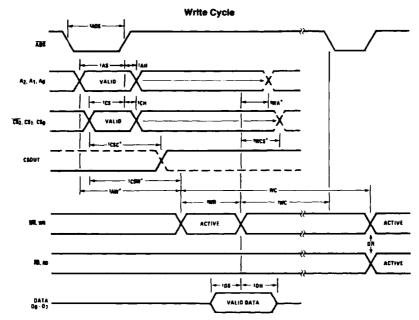

| t <sub>ADS</sub>  | Address Strobe Width                                              |                                          | 60   |             | 90         |          | ns                      |

| t <sub>AH</sub>   | Address Hold Time                                                 |                                          | 0    |             | 0          |          | ns                      |

| t <sub>AR</sub>   | RD, RD Delay from Address                                         | (Note 1)                                 | 60   |             | 80         | _        | ns                      |

| t <sub>AS</sub>   | Address Setup Time                                                |                                          | 60   |             | 90         |          | ns                      |

| t <sub>AW</sub>   | WR, WR Delay from Address                                         | (Note 1)                                 | 60   |             | 80         |          | ns                      |

| t <sub>CH</sub>   | Chip Select Hold Time                                             |                                          | 0    |             | 0          |          | ns                      |

| tcs               | Chip Select Setup Time                                            |                                          | 60   |             | 90         |          | ns                      |

| tcsc              | Chip Select Output Delay from Select                              | @100 pF loading (Note 1)                 |      | 100         |            | 125      | ns                      |

| t <sub>CSR</sub>  | RD, RD Delay from Chip Select                                     | (Note 1)                                 | 50   |             | 80         |          | ns                      |

| t <sub>CSW</sub>  | WR, WR Delay from Select                                          | (Note 1)                                 | 50   |             | 80         |          | ns                      |

| t <sub>DH</sub>   | Data Hold Time                                                    |                                          | 40   | <del></del> | 60         |          | ns                      |

| t <sub>DS</sub>   | Data Setup Time                                                   |                                          | 40   |             | 90         |          | ns                      |

| tHZ               | RD, RD to Floating Data Delay                                     | @100 pF loading (Note 3)                 | 0    | 100         | 0          | 100      | ns                      |

| t <sub>MR</sub>   | Master Reset Pulse Width                                          |                                          | 5    |             | 10         |          | μs                      |

| <sup>t</sup> RA   | Address Hold Time from RD, RD                                     | (Note 1)                                 | 20   |             | 20         |          | ns                      |

| t <sub>RC</sub>   | Read Cycle Delay                                                  |                                          | 175  | <u> </u>    | 500        |          | ns                      |

| tRCS              | Chip Select Hold Time from RD, RD                                 | (Note 1)                                 | 20   |             | 20         |          | ns                      |

| t <sub>RD</sub>   | RD, RD Strobe Width                                               |                                          | 125  |             | 175        |          | ns                      |

| t <sub>RDD</sub>  | RD, RD to Driver Disable Delay                                    | @100 pF loading (Note 3)                 |      | 60          |            | 75       | ns                      |

| t <sub>RVD</sub>  | Delay from RD, RD to Data                                         | @100 pF loading                          |      | 125         |            | 175      | ns                      |

| twa               | Address Hold Time from WR, WR                                     | (Note 1)                                 | 20   |             | 20         |          | ns                      |

| twc               | Write Cycle Delay                                                 |                                          | 200  |             | 500        |          | ns                      |

| twcs              | Chip Select Hold Time from WR, WR                                 | (Note 1)                                 | 20   |             | 20         |          | ns                      |

| twer              | WR, WR Strobe Width                                               |                                          | 100  |             | 175        |          | ns                      |

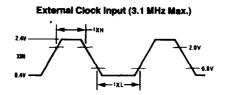

| t <sub>XH</sub>   | Duration of Clock High Pulse                                      | External Clock (3.1 MHz Max.)            | 140  |             | 140        |          | ns                      |

| t <sub>XL</sub>   | Duration of Clock Low Pulse                                       | External Clock (3.1 MHz Max.)            | 140  |             | 140        |          | ns                      |

| RC                | Read Cycle = t <sub>AR</sub> + t <sub>RD</sub> + t <sub>RC</sub>  |                                          | 360  |             | 755        |          | ns                      |

| wc                | Write Cycle = t <sub>AW</sub> + t <sub>WR</sub> + t <sub>WC</sub> |                                          | 360  | İ           | 755        |          | ns                      |

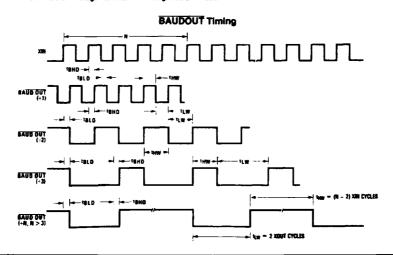

| Baud Ge           |                                                                   |                                          |      | <u> </u>    | · <u>.</u> | <u> </u> | <u> </u>                |

| N                 | Baud Divisor                                                      |                                          | 1    | 216-1       | 1          | 216-1    |                         |

| t <sub>BHD</sub>  | Baud Output Positive Edge Delay                                   | 100 pF Load                              |      | 125         |            | 250      | ns                      |

| t <sub>BLD</sub>  | Baud Output Negative Edge Del.                                    | 100 pF Load                              |      | 125         |            | 250      | ns                      |

| t <sub>HW</sub>   | Baud Output Up Time                                               | f <sub>X</sub> = 3 MHz, ÷ 3, 100 pF Load | 330  |             | 330        |          | ns                      |

| t <sub>LW</sub>   | Baud Output Down Time                                             | f <sub>X</sub> = 2 MHz, ÷ 2, 100 pF Load | 425  |             | 425        |          | ns                      |

| Receive           |                                                                   |                                          |      |             |            | ·        | •                       |

| <sup>t</sup> RINT | Delay from RD, RD<br>(RD RBR or RD LSR)<br>to Reset Interrupt     | 100 pF Load                              |      | 1           |            | 1        | μs                      |

| t <sub>SCD</sub>  | Delay from RCLK to Sample Time                                    |                                          |      | 2           |            | 2        | μs                      |

| <sup>t</sup> SINT | Delay from Stop to Set Interrupt                                  |                                          |      | 1           |            | 1        | RCLK<br>Cycle<br>(Note: |

Note 1: Applicable only when  $\overline{ADS}$  is tied low. Note 2: RCLK is equal to  $t_{XH}$  and  $t_{XL}$ .

Note 3: Charge and discharge time is determined by  $V_{\text{OL}},\,V_{\text{OH}}$  and the external loading.

# 3.0 AC Electrical Characteristics $T_A = 0^{\circ}C$ to $+70^{\circ}C$ , $V_{CC} = +5V \pm 5\%$ (Continued)

| Symbol           | Parameter                                            | Conditions  | GM16C450 |     | GM82C50A |      | Units             |

|------------------|------------------------------------------------------|-------------|----------|-----|----------|------|-------------------|

| _                |                                                      |             | Min      | Max | Min      | Max  | """               |

| Transmit         | iter                                                 |             |          |     |          |      |                   |

| t <sub>HR</sub>  | Delay from WR, WR (WR THR) to Reset Interrupt        | 100 pF Load |          | 175 | _        | 1000 | ns                |

| t <sub>IR</sub>  | Delay from RD, RD (RD IIR) to Reset Interrupt (THRE) | 100 pF Load | _        | 250 |          | 1000 | ns                |

| t <sub>IRS</sub> | Delay from Initial INTR Reset to Transmit Start      |             | 8        | 24  | 8        | 24   | BAUDOUT<br>Cycles |

| tsı              | Delay from Initial Write to Interrupt                |             | 16       | 32  | 16       | 32   | BAUDOUT<br>Cycles |

| t <sub>STI</sub> | Delay from Stop to Interrupt (THRE)                  |             | 8        | 8   | 8        | 8    | BAUDOUT<br>Cycles |

| Modem (          | Control                                              | •           |          |     |          |      |                   |

| <sup>t</sup> MDO | Delay from WR, WR (WR MCR) to<br>Output              | 100 pF Load |          | 200 |          | 1000 | ns                |

| <sup>t</sup> RIM | Delay to Reset Interrupt from RD, RD (RD MSR)        | 100 pF Load |          | 250 |          | 1000 | ns                |

| tsim             | Delay to Set Interrupt from MODEM Input              | 100 pF Load |          | 250 |          | 1000 | ns                |

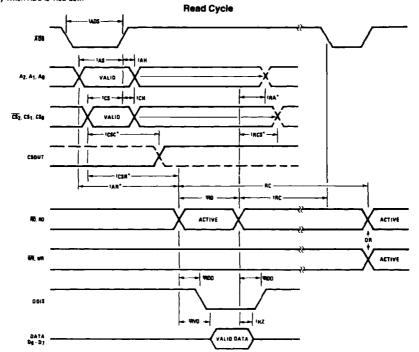

## 4.9 Timing Waveforms (All timings are referenced to valid 0 and valid 1)

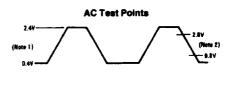

Note 1: The 2.4V and 0.4V levels are the voltages that the inputs are driven to during AC testing.

Note 2: The 2.0V and 0.8V levels are the voltages at which the timing tests are made.

T

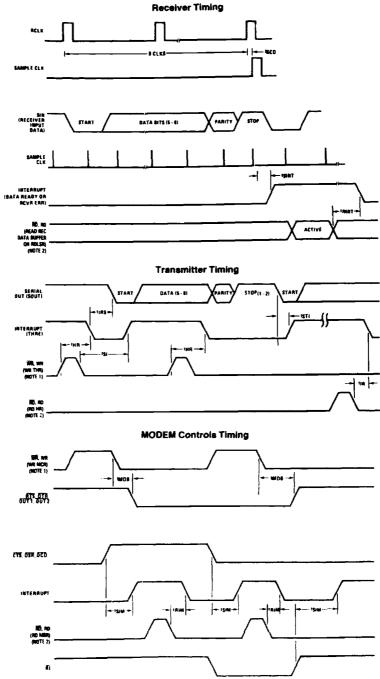

## 4.0 Timing Waveforms (Continued)

\*Applicable Only When ADS is Tied Low.

<sup>\*</sup>Applicable Only When ADS is Tied Low.

## 4.0 Timing Waveforms (Continued)

Note 1: See Write Cycle Timing Note 2: See Read Cycle Timing

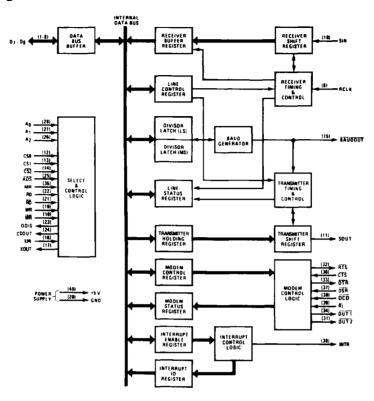

### 5.0 Block Diagram

Note: Applicable pinout numbers are included within parenthesis.

## 6.0 Pin Descriptions

The following describes the function of all ACE pins. Some of these descriptions reference internal circuits.

In the following descriptions, a low represents a logic 0 (0V nominal) and a high represents a logic 1 (+2.4V nominal).

#### 6.1 INPUT SIGNALS

Chip Select (CS0, CS1,  $\overline{CS2}$ ), Pins 12–14: When CS0 and CS1 are high and  $\overline{CS2}$  is low, the chip is selected. This enables communication between the AC£ and the CPU. The positive edge of an active Address Strobe signal latches the decoded chip select signals, completing chip selection. If  $\overline{ADS}$  is always low, valid chip selects should stabilize according to the  $t_{CSW}$  parameter.

Read (RD, RD), Pins 22 and 21: When RD is high or RD is low while the chip is selected, the CPU can read status information or data from the selected ACE register.

**Note:** Only an active RD or  $\overrightarrow{RD}$  input is required to transfer data from the UART during a read operation. Therefore, tie either the RD input permanently low or the  $\overrightarrow{RD}$  input permanently high, when it is not used.

Write (WR, WR), Pins 19 and 18: When WR is high or WR is low while the chip is selected, the CPU can write control words or data into the selected ACE register.

Note: Only an active WR or  $\overline{WR}$  input is required to transfer data to the UART during a write operation. Therefore, tie either the WR input permanently low or the  $\overline{WR}$  input permanently high, when it is not used.

Address Strobe ( $\overline{ADS}$ ), Pin 25: The positive edge of an active Address Strobe ( $\overline{ADS}$ ) signal latches the Register Select (A0, A1, A2) and Chip Select (CS0, CS1, CS2) signals. Note: An active  $\overline{ADS}$  input is required when the Register Select (A0, A1, A2) signals are not stable for the duration of a read or write operation. If not required, the the  $\overline{ADS}$  input permanently low.

Register Select (A0, A1, A2), Pins 26–28: Address signals connected to these 3 inputs select a ACE register for the CPU to read from or write to during data transfer. A table of registers and their addresses is shown below. Note that the state of the Divisor Latch Access Bit (DLAB), which is the most significant bit of the Line Control Register, affects the selection of certain ACE registers. The DLAB must be set high by the system software to access the Baud Generator Divisor Latches.

T

#### 6.0 Pin Descriptions (Continued)

#### Register Addresses

| DLAB | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | Register                 |

|------|----------------|----------------|----------------|--------------------------|

| 0    | 0              | 0              | 0              | Receiver Buffer (read),  |

| \ '  |                |                |                | Transmitter Holding      |

|      | ľ              |                |                | Register (write)         |

| 0    | 0              | 0              | 1              | Interrupt Enable         |

| ) x  | 0              | 1              | 0              | Interrupt Identification |

| 1    | ]              |                | }              | (read only)              |

| l x  | 0              | 1              | 1              | Line Control             |

| x    | 1              | 0              | 0              | MODEM Control            |

| X    | 1              | 0              | 1              | Line Status              |

| x    | 1              | 1              | 0              | MODEM Status             |

| x    | 1              | 1              | 1              | Scratch                  |

| 1    | 0              | 0              | 0              | Divisor Latch            |

| ì    |                | 1              | 1              | (least significant byte) |

| 1 1  | 0              | 0              | 1              | Divisor Latch            |

|      |                |                |                | (most significant byte)  |

Master Reset (MR), Pin 35: When this input is high, it clears all the registers (except the Receiver Buffer, Transmitter Holding, and Divisor Latches), and the control logic of the UART. The states of various output signals (SOUT, INTR, OUT 1, OUT 2, RTS, DTR) are affected by an active MR input. (Refer to Table I.) This input is buffered with a TTL-compatible Schmitt Trigger with 0.5V typical hysteresis.

Receiver Clock (RCLK), Pin 9: This input is the 16  $\times$  baud rate clock for the receiver section of the chip.

Serial Input (SIN), Pin 10: Serial data input from the communications link (peripheral device, MODEM, or data set).

Clear to Send (CTS), Pin 36: When low, this indicates that the MODEM or data set is ready to exchange data. The CTS signal is a MODEM status input whose conditions can be tested by the CPU reading bit 4 (CTS) of the MODEM Status Register. Bit 4 is the complement of the CTS signal. Bit 0 (DCTS) of the MODEM Status Register indicates whether the CTS input has changed state since the previous reading of the MODEM Status Register. CTS has no effect on the Transmitter.

Note: Whenever the CTS bit of the MODEM Status Register changes state, an interrupt is generated if the MODEM Status Interrupt is enabled.

Data Set Ready (DSR), PIn 37: When low, this indicates that the MODEM or data set is ready to establish the communications link with the ACE. The DSR signal is a MODEM status input whose condition can be tested by the CPU reading bit 5 (DSR) of the MODEM Status Register. Bit 5 is the complement of the DSR signal. Bit 1 (DDSR) of the MODEM Status Register indicates whether the DSR input has changed state since the previous reading of the MODEM Status Register.

Note: Whenever the DSR bit of the MODEM Status Register changes state, an interrupt is generated if the MODEM Status Interrupt is enabled.

Data Carrier Detect (DCD), Pln 38: When low, indicates that the data carrier has been detected by the MODEM or data set. The DCD signal is a MODEM status input whose condition can be tested by the CPU reading bit 7 (DCD) of the MODEM Status Register. Bit 7 is the complement of the DCD signal. Bit 3 (DDCD) of the MODEM Status Register indicates whether the DCD input has changed state

since the previous reading of the MODEM Status Register.  $\overline{DCD}$  has no effect on the receiver.

Note: Whenever the DCD bit of the MODEM Status Register changes state, an interrupt is generated if the MODEM Status Interrupt is enabled.

Ring Indicator (RI), Pln 39: When low, this indicates that a telephone ringing signal has been received by the MODEM or data set. The RI signal is a MODEM status input whose condition can be tested by the CPU reading bit 6 (RI) of the MODEM Status Register. Bit 6 is the complement of the RI signal. Bit 2 (TERI) of the MODEM Status Register indicates whether the RI input signal has changed from a low to a high state since the previous reading of the MODEM Status Register.

Note: Whenever the RI bit of the MODEM Status Register changes from a high to a low state, an interrupt is generated if the MODEM Status interrupt is enabled.

V<sub>CC</sub>, Pin 40: +5V supply.

V<sub>SS</sub>, Pin 20: Ground (0V) reference.

#### **6.2 OUTPUT SIGNALS**

Data Terminal Ready (DTR), Pin 33: When low, this informs the MODEM or data set that the UART is ready to establish a communications link. The DTR output signal can be set to an active low by programming bit 0 (DTR) of the MODEM Control Register to a high level. A Master Reset operation sets this signal to its inactive (high) state. Loop mode operation holds this signal in its inactive state.

Request to Send (RTS), Pin 32: When low, this informs the MODEM or data set that the ACE is ready to exchange data. The RTS output signal can be set to an active low by programming bit 1 (RTS) of the MODEM Control Register. A Master Reset operation sets this signal to its inactive (high) state. Loop mode operation holds this signal in its inactive state.

Output 1 (OUT 1), Pin 34: This user-designated output can be set to an active low by programming bit 2 (OUT 1) of the MODEM Control Register to a high level. A Master Reset operation sets this signal to its inactive (high) state. Loop mode operation holds this signal in its inactive state. In the XMOS parts this will achieve TTL levels.

Output 2 (OUT 2), Pln 31: This user-designated output can be set to an active low, by programming bit 3 (OUT 2) of the MODEM Control Register to a high level. A Master Reset operation sets this signal to its inactive (high) state. Loop mode operation holds this signal in its inactive state. In the XMOS parts this will achieve TTL levels.

Chip Select Out (CSOUT), Pin 24: When high, it indicates that the chip has been selected by active, CSO, CS1, and CS2 inputs. No data transfer can be initiated until the CSOUT signal is a logic 1. CSOUT goes low when the UART is deselected.

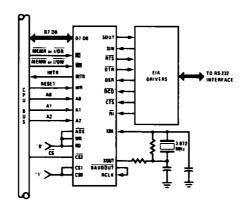

**Driver Disable (DDIS), Pin 23:** This goes low whenever the CPU is reading data from the UART. It can disable or control the direction of a data bus transceiver between the CPU and the ACE (see Typical Interface for a High Capacity Data Bus).

**Baud Out (BAUDOUT), Pln 15:** This is the  $16 \times$  clock signal from the transmitter section of the UART. The clock rate is equal to the main reference oscillator frequency divided by the specified divisor in the Baud Generator Divisor Latches. The BAUDOUT may also be used for the receiver section by tying this output to the RCLK input of the chip.

### 6.0 Pin Descriptions (Continued)

Interrupt (INTR), Pin 30: This goes high whenever any one of the following interrupt types has an active high condition and is enabled via the IER: Receiver Line Status; Received Data Available; Transmitter Holding Register Empty; and MODEM Status. The INTR signal is reset low upon the appropriate interrupt service or a Master Reset operation.

Serial Output (SOUT), Pin 11: This is the composite serial data output to the communications link (peripheral, MODEM or data set). The SOUT signal is set to the Marking (logic 1) state upon a Master Reset operation or when the transmitter is idle.

#### 6.3 INPUT/OUTPUT SIGNALS

**Data (D<sub>7</sub>-D<sub>0</sub>) Bus, Pins 1-8:** This bus is comprised of eight TRI-STATE input/output lines. The bus provides bidirectional communications between the ACE and the CPU. Data, control words, and status information are transferred via the  $D_7-D_0$  Data Bus.

External Clock Input/Output (XIN, XOUT) Pins 16 and 17: These two pins connect the main timing reference (crystal or signal clock) to the UART. When a crystal oscillator or a clock signal is provided, it drives the ACE via XIN (see typical oscillator network illustration).

### 7.0 Connection Diagrams

**TABLE I. UART Reset Functions**

| Register/Signal                   | Reset Control         | Reset State               |  |  |

|-----------------------------------|-----------------------|---------------------------|--|--|

| Interrupt Enable Register         | Master Reset          | <b>0000</b> 0000 (Note 1) |  |  |

| Interrupt Identification Register | Master Reset          | 0000 0001                 |  |  |

| Line Control Register             | Master Reset          | 0000 0000                 |  |  |

| MODEM Control Register            | Master Reset          | 0000 0000                 |  |  |

| Line Status Register              | Master Reset          | <b>0</b> 110 0000         |  |  |

| MODEM Status Register             | Master Reset          | XXXX 0000 (Note 2)        |  |  |

| SOUT                              | Master Reset          | High                      |  |  |

| INTR (RCVR Errs)                  | Read LSR/MR           | Low                       |  |  |

| INTR (RCVR Data Ready)            | Read RBR/MR           | Low                       |  |  |

| INTR (THRE)                       | Read IIR/Write THR/MR | Low                       |  |  |

| INTR (Modern Status Changes)      | Read MSR/MR           | Low                       |  |  |

| OUT 2                             | Master Reset          | High                      |  |  |

| RTS                               | Master Reset          | High                      |  |  |

| ĎΤŔ                               | Master Reset          | High                      |  |  |

| OUT 1                             | Master Reset          | High                      |  |  |

Note 1: Boldface bits are permanently low.

Note 2: Bits 7-4 are driven by the input signals