LM11C, CL

# Precision Operational Amplifiers

The LM11C is a precision, low drift operational amplifier providing the best features of existing FET and Bipolar op amps. Implementation of super gain transistors allows reduction of input bias currents by an order of magnitude over earlier devices such as the LM308A. Offset voltage and drift have also been reduced. Although bandwidth and slew rate are not as great as FET devices, input offset voltage, drift and bias current are inherently lower, particularly over temperature. Power consumption is also much lower, eliminating warm—up stabilization time in critical applications.

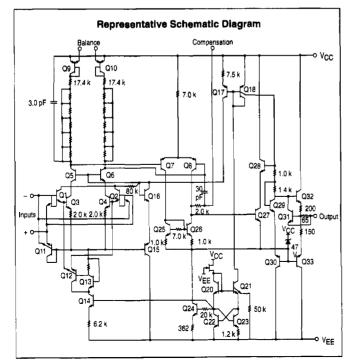

Offset balancing is provided, with the range determined by an external low resistance potentiometer. Compensation is provided internally, but external compensation can be added for improved stability when driving capacitive loads.

The precision characteristics of the LM11C make this device ideal for applications such as charge integrators, analog memories, electrometers, active filters, light meters and logarithmic amplifiers.

Low Input Offset Voltage: 100 μV

Low Input Bias Current: 17 pA

Low Input Offset Current: 0.5 pA

Low Input Offset Voltage Drift: 1.0 μV/°C

Long-Term Stability: 10 μV/year

• High Common Mode Rejection: 130 dB

# PRECISION OPERATIONAL AMPLIFIERS

SEMICONDUCTOR TECHNICAL DATA

N SUFFIX PLASTIC PACKAGE CASE 626

#### ORDERING INFORMATION

| Device     | Operating<br>Temperature Range | Package     |  |  |

|------------|--------------------------------|-------------|--|--|

| LM11CN,CLN | T <sub>A</sub> = 0° to +70°C   | Plastic DIP |  |  |

#### **MAXIMUM RATINGS**

| Rating                                 | Symbol           | Value       | Unit |

|----------------------------------------|------------------|-------------|------|

| Power Supply Voltage                   | VCC to VEE       | 40          | Vdc  |

| Differential Input Current (Note 1)    | ID               | ±10         | mA   |

| Output Short Circuit Duration (Note 2) | tsc              | Indefinite  |      |

| Power Dissipation (Note 3)             | ₽D               | 500         | mW   |

| Operating Junction Temperature         | TJ               | 85          | °C   |

| Storage Temperature Range              | T <sub>stg</sub> | -55 to +125 | ÷C   |

### **ELECTRICAL CHARACTERISTICS** (T<sub>J</sub> = 25°C, unless otherwise noted [ Note 4 ] .)

| Characteristic                                                                                                                                                                                                                                                                                                                             | Symbol                            | Min                     | Тур                 | Max         | Min                  | Тур             | Max         | Unit               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------|---------------------|-------------|----------------------|-----------------|-------------|--------------------|

| Input Offset Voltage Tlow to Thigh                                                                                                                                                                                                                                                                                                         | VIO                               | -                       | 0.2<br>-            | 0.6<br>0.8  | -<br>-               | 0.5<br>–        | 5.0<br>6.0  | mV                 |

| Input Offset Current Tlow <sup>to T</sup> high                                                                                                                                                                                                                                                                                             | lio                               | _                       | 1.0                 | 10<br>20    | -                    | 4.0<br>-        | 25<br>50    | pА                 |

| Input Bias Current Tlow to Thigh                                                                                                                                                                                                                                                                                                           | IB                                | -                       | 17<br>              | 100<br>150  | _<br>_               | 17<br>-         | 200<br>300  | pА                 |

| Input Resistance                                                                                                                                                                                                                                                                                                                           | rį                                | -                       | 1011                | -           | -                    | 1011            | _           | Ω                  |

| Input Offset Voltage Drift Tlow <sup>to T</sup> high                                                                                                                                                                                                                                                                                       | ∆V <sub>IO</sub> /∆T              | -                       | 2.0                 | 5.0         | _                    | 3.0             | -           | μV/ <sup>-</sup> C |

| Input Offset Current Drift Tlow to Thigh                                                                                                                                                                                                                                                                                                   | ΔΙ <sub>ΙΟ</sub> /ΔΤ              | _                       | 10                  | -           | _                    | 50              | -           | fA/°C              |

| Input Bias Current Drift Tlow to Thigh                                                                                                                                                                                                                                                                                                     | Δl <sub>IB</sub> / <sub>Δ</sub> T | -                       | 0.8                 | 3.0         | -                    | 1.4             | -           | pA∕°C              |

| Large Signal Voltage Gain $V_S = \pm 15 \text{ V, } V_{\text{out}} = \pm 12 \text{ V, } I_{\text{out}} = \pm 2.0 \text{ mA}$ $T_{\text{low}} \text{ to } T_{\text{high}} \text{ (Note 5)}$ $V_S = \pm 15 \text{ V, } V_{\text{out}} = \pm 12 \text{ V, } I_{\text{out}} = \pm 0.5 \text{ mA}$ $T_{\text{low}} \text{ to } T_{\text{high}}$ | Avol                              | 100<br>50<br>250<br>100 | 300<br><br>1200<br> | -<br>-<br>- | 25<br>15<br>50<br>30 | 300<br>-<br>800 | -<br>-<br>- | V/mV               |

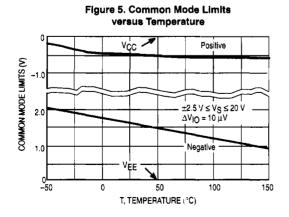

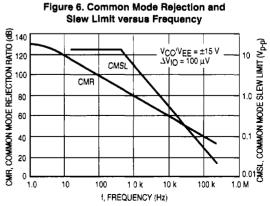

| Common Mode Rejection $V_S = \pm 15 \text{ V,} -13 \text{ V} \leq V_{CM} \leq 14 \text{ V}$ $V_S = \pm 15 \text{ V,} -12.5 \text{ V} \leq V_{CM} \leq 14 \text{ V.} \text{ Tlow to Thigh}$                                                                                                                                                 | CMR                               | 110<br>100              | 130                 | -<br>-      | 96<br>90             | 110             | -           | dB                 |

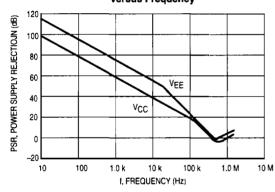

| Power Supply Rejection<br>±2.5 V ≤ V <sub>S</sub> ≤ ±20 V<br>T <sub>low</sub> to Thigh                                                                                                                                                                                                                                                     | PSR                               | 100<br>96               | 118                 | -           | 84<br>80             | 100             | -           | dB                 |

| Power Supply Current Tlow to Thigh                                                                                                                                                                                                                                                                                                         | ΙD                                | -                       | 0.3                 | 0.8         | -                    | 0.3             | 0.8         | mA                 |

| Output Short Circuit Current T <sub>J</sub> = 150°C, Output Shorted to Ground                                                                                                                                                                                                                                                              | Isc                               | -                       | ±10                 | -           | -                    | ±10             | -           | mA                 |

- NOTES: 1. The inputs are shunted by back-to-back diodes for over-voltage protection. Excessive current will flow if the input differential voltage is in excess of 1.0 V if no limiting resistance is used. Additionally, a 2.0 kΩ resistance in each input is suggested to prevent possible latch-up initiated by supply reversals.

- reversals.

2. The output is current limited when shorted to ground or any voltages less than the supplies. Continuous overloads will require package dissipation to be considered and heatsinking should be provided when necessary.

3. Devices must be derated based on package thermal resistance (see package outline dimensions).

4. These specifications apply for VEE +2.0 V ≤ VCM ≤ VCC −1.0 V (VEE +2.5 V ≤ VCM ≤ VCC −1.0 V for Tlow to Thigh; 0°C ≤ T ≤ +70°C for LM11C and LM11C.

5. Vout = ±11 5 V, all other conditions unchanged.

Figure 1. Input Bias Current versus Case Temperature 50 40 IB, INPUT BIAS CURRENT (pA) 30 VCC/VEE = ±2.0 V 20 10 0 -10 -20 VCC√VEE = ±2.5 V -30 -40 -50 -50 -25 25 75 50 100 125 150 TC, CASE TEMPERATURE (°C)

Figure 2. Input Offset Current versus Case Temperature I<sub>IO</sub>, INPUT OFFSET CURRENT (pA) 30 Curve 1,  $V_{CC}/V_{EE} = \pm 20 \text{ V}$ 2,  $V_{CC}/V_{EE} = \pm 2.5 \text{ V}$ 20 10 2 0 -50 -25 0 25 50 75 100 125 150 TC. CASE TEMPERATURE (°C)

Figure 3. Temperature Coefficient of Input Offset Voltage versus Input Offset Voltage

VCC/VEE = ±20 V

At = 25° to 125°C

VIO, INPUT OFFSET VOLTAGE (mv) @ 25°C

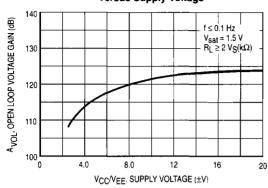

Figure 7. Open Loop Voltage Gain versus Supply Voltage

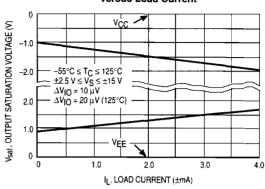

Figure 8. Output Saturation versus Load Current

Figure 9. Power Supply Rejection Ratio versus Frequency

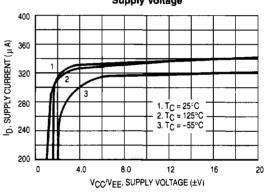

Figure 10. Supply Current versus Supply Voltage

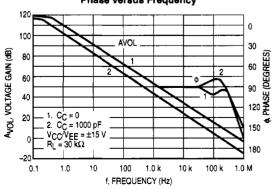

Figure 11. Open Loop Voltage Gain and Phase versus Frequency

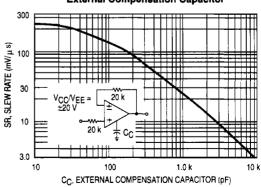

Figure 12. Slew Rate versus External Compensation Capacitor

1.0 k

1.0 k

100

A<sub>V</sub> = 1000

VCC<sup>V</sup>EE = ±15 V

I<sub>out</sub> = ±1.0 mA

Figure 13. Closed Loop Output Impedance versus Frequency

## **APPLICATIONS INFORMATION**

10 k

f, FREQUENCY (Hz)

100 k

1.0 M

Due to the extremely low input bias currents of this device, it may be tempting to remove the bias current compensation resistor normally associated with a summing amplifier configuration. Direct connection of the inputs to a low impedance source or ground should be avoided when supply voltages greater than approximately 3.0 V are used. The potential problem involves reversal of one supply which can cause excessive current to flow in the second supply. Possible destruction of the IC could result if the second supply is not current limited to approximately 100 mA or if bypass capacitors greater than 1.0  $\mu F$  are used in the supply bus.

0.01

100

1.0 k

Disconnecting one supply will generally cause reversal due to loading of the other supply within the IC and in external circuitry. Although the problem can usually be avoided by placing clamp diodes across the power supplies of each printed circuit board, a careful design will include sufficient resistance in the input leads to limit the current to 10 mA if the input leads are pulled to either supply by internal currents. This precaution is not limited only to the LM11C.

The LM11C is capable of resolving picoampere level signals. Leakage currents external to the IC can severely impair the performance of the device. It is important that high quality insulating materials such as teflon be employed. Proper cleaning to remove fluxes and other residues from

printed circuit boards, sockets and the device package are necessary to minimize surface leakage.

10 M

When operating in high humidity environments or temperatures near 0°C, a surface coating is suggested to set up a moisture barrier.

Leakage effects on printed circuit boards can be reduced by encircling the inputs (both sides of pc board) with a conductive guard ring connected to a low impedance potential nearly the same as that of the inputs.

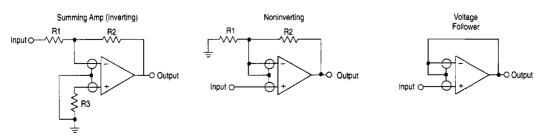

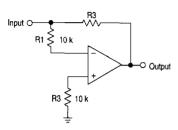

Guard ring electrical connections for common operational amplifier configurations are illustrated in Figure 14. Electrostatic shielding is suggested in high impedance circuits

Error voltages in external circuitry can be generated by thermocouple effects. Dissimilar metals along with temperature gradients can set up an error voltage ranging in the hundreds of microvolts. Some of the best thermocouples are junctions of dissimilar metals made up of IC package pins and printed circuit boards. Problems can be avoided by keeping low level circuitry away from heat generating elements.

The LM11C is internally compensated, but external compensation can be added to improve stability, particularly when driving capacitive loads.

Figure 14. Guard Ring Electrical Connections for Common Amplifier Configurations

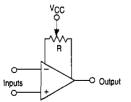

Figure 15. Input Protection for Summing (Inverting) Amplifier

Current is limited by R1 in the event the input is connected to a low impedance source outside the common mode range of the device. Current is controlled by R2 if one supply reverses, R1 and R2 do not affect normal operation.

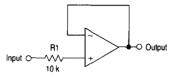

Figure 16. Input Protection for a Voltage Follower

Input current is limited by R1 when the input exceeds supply voltage, power supply is turned off, or output is shorted.

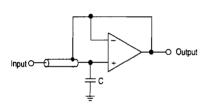

Figure 17. Cable Bootstrapping and input Shields

An input shield bootstrapped in a voltage follower reduces input capacitance, leakage, and spurious voltages from cable flexing. A small capacitor from the input to ground will prevent any instability.

In a summing amplifier the input is at virtual ground. Therefore the shield can be grounded. A small feedback capacitor will insure stability.

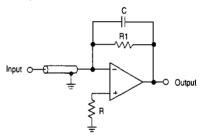

Figure 18. Adjusting input Offset Voltage with Balance Potentiometer

| Minimum<br>Adjustment Range<br>(mV) | ਸ<br>(Ω) |  |  |

|-------------------------------------|----------|--|--|

| ±0.4                                | 1.0 k    |  |  |

| ±1.0                                | 3.0 k    |  |  |

| ±2.0                                | 10 k     |  |  |

| ±5.0                                | 100 k    |  |  |

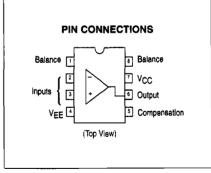

Input offset voltage adjustment range is a function of the Balance Potentiometer Resistance as indicated by the table above. The potentiometer is connected between the two "Balance" pins.