# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceed the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-35835

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

February 1990 Revised August 2000

### 100331

## Low Power Triple D-Type Flip-Flop

#### **General Description**

The 100331 contains three D-type, edge-triggered master/slave flip-flops with true and complement outputs, a Common Clock (CP<sub>C</sub>), and Master Set (MS) and Master Reset (MR) inputs. Each flip-flop has individual Clock (CP<sub>n</sub>), Direct Set (SD<sub>n</sub>) and Direct Clear (CD<sub>n</sub>) inputs. Data enters a master when both CP<sub>n</sub> and CP<sub>C</sub> are LOW and transfers to a slave when CP<sub>n</sub> or CP<sub>C</sub> (or both) go HIGH. The Master Set, Master Reset and individual CD<sub>n</sub> and SD<sub>n</sub> inputs override the Clock inputs. All inputs have 50 k $\Omega$  pull-down resistors.

#### **Features**

- 35% power reduction of the 100131

- 2000V ESD protection

- Pin/function compatible with 100131

- Voltage compensated operating range = -4.2V to -5.7V

- Available to industrial grade temperature range

## **Ordering Code:**

| Order Number | Package Number | Package Description                                                                                                |

|--------------|----------------|--------------------------------------------------------------------------------------------------------------------|

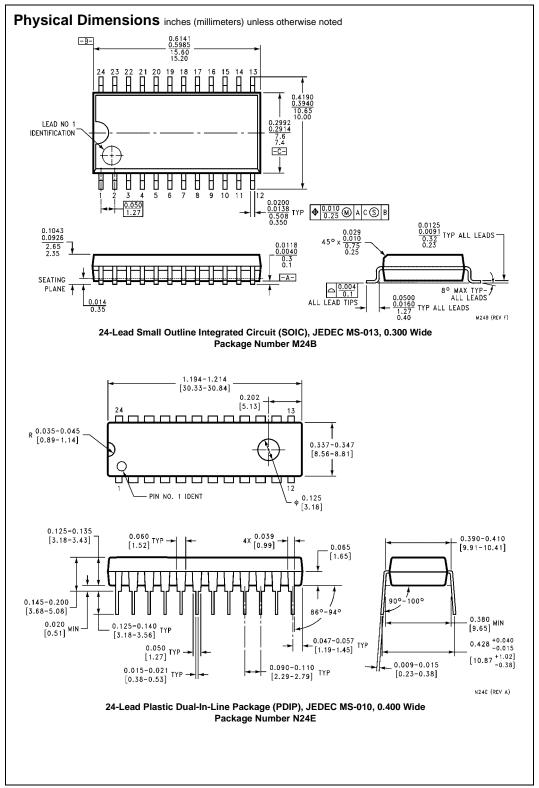

| 100331SC     | M24B           | 24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide                                          |

| 100331PC     | N24E           | 24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-010, 0.400 Wide                                              |

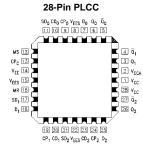

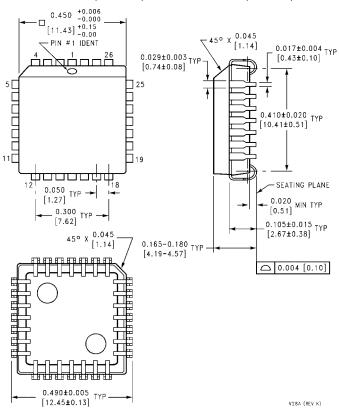

| 100331QC     | V28A           | 28-Lead Plastic Lead Chip Carrier (PLCC), JEDEC MO-047, 0.450 Square                                               |

| 100331QI     |                | 28-Lead Plastic Lead Chip Carrier (PLCC), JEDEC MO-047, 0.450 Square Industrial Temperature Range (–40°C to +85°C) |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

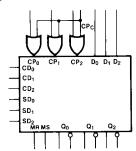

#### **Logic Symbol**

#### **Pin Descriptions**

| Pin Names                         | Description                    |

|-----------------------------------|--------------------------------|

| CP <sub>0</sub> -CP <sub>2</sub>  | Individual Clock Inputs        |

| CP <sub>C</sub>                   | Common Clock Input             |

| D <sub>0</sub> -D <sub>2</sub>    | Data Inputs                    |

| CD <sub>0</sub> -CD <sub>2</sub>  | Individual Direct Clear Inputs |

| SD <sub>n</sub>                   | Individual Direct Set Inputs   |

| MR                                | Master Reset Input             |

| MS                                | Master Set Input               |

| $Q_0-Q_2$                         | Data Outputs                   |

| $\overline{Q}_0 - \overline{Q}_2$ | Complementary Data Outputs     |

#### **Connection Diagrams**

### **Truth Tables**

#### Synchronous Operation (Each Flip-Flop)

|                | Inputs          |                 |                       |                       |                        |  |  |  |  |  |  |

|----------------|-----------------|-----------------|-----------------------|-----------------------|------------------------|--|--|--|--|--|--|

| D <sub>n</sub> | CP <sub>n</sub> | CP <sub>C</sub> | MS<br>SD <sub>n</sub> | MR<br>CD <sub>n</sub> | Q <sub>n</sub> (t + 1) |  |  |  |  |  |  |

| L              | ~               | L               | L                     | L                     | L                      |  |  |  |  |  |  |

| Н              | ~               | L               | L                     | L                     | Н                      |  |  |  |  |  |  |

| L              | L               | ~               | L                     | L                     | L                      |  |  |  |  |  |  |

| Н              | L               | ~               | L                     | L                     | Н                      |  |  |  |  |  |  |

| Х              | L               | L               | L                     | L                     | Q <sub>n</sub> (t)     |  |  |  |  |  |  |

| X              | Н               | Х               | L                     | L                     | Q <sub>n</sub> (t)     |  |  |  |  |  |  |

| Х              | Х               | Н               | L                     | L                     | Q <sub>n</sub> (t)     |  |  |  |  |  |  |

Asynchronous Operation (Each Flip-Flop)

|                | Outputs         |                 |                       |                       |                        |

|----------------|-----------------|-----------------|-----------------------|-----------------------|------------------------|

| D <sub>n</sub> | CP <sub>n</sub> | CP <sub>C</sub> | MS<br>SD <sub>n</sub> | MR<br>CD <sub>n</sub> | Q <sub>n</sub> (t + 1) |

| Х              | Х               | Х               | Н                     | L                     | Н                      |

| X              | Х               | Х               | L                     | Н                     | L                      |

| X              | Х               | Х               | Н                     | Н                     | U                      |

- H = HIGH Voltage Level L = LOW Voltage Level X = Don't Care U = Undefined

- t = Time before CP Positive Transition

t + 1 = Time after CP Positive Transition

= LOW-to-HIGH Transition

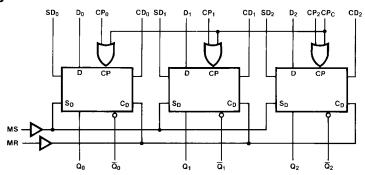

## **Logic Diagram**

### **Absolute Maximum Ratings**(Note 1)

$\begin{array}{lll} Storage \ Temperature \ (T_{STG}) & -65^{\circ}C \ to +150^{\circ}C \\ Maximum \ Junction \ Temperature \ (T_{J}) & +150^{\circ}C \\ Pin \ Potential \ to \ Ground \ Pin \ (V_{EE}) & -7.0V \ to +0.5V \\ Input \ Voltage \ (DC) & V_{EE} \ to +0.5V \\ Output \ Current & & & & & & & \\ \end{array}$

(DC Output HIGH) -50 mAESD (Note 2)  $\leq 2000 \text{V}$

## Recommended Operating Conditions

Case Temperature (T<sub>C</sub>)

Note 1: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum rating. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

Note 2: ESD testing conforms to MIL-STD-883, Method 3015.

#### **Commercial Version**

#### **DC Electrical Characteristics** (Note 3)

$V_{EE} = -4.2V$  to -5.7V,  $V_{CC} = V_{CCA} = GND$ ,  $T_{C} = 0$ °C to +85°C

| Symbol           | Parameter            | Min   | Тур   | Max   | Units | Con                                                  | Conditions                              |  |  |  |  |

|------------------|----------------------|-------|-------|-------|-------|------------------------------------------------------|-----------------------------------------|--|--|--|--|

| V <sub>OH</sub>  | Output HIGH Voltage  | -1025 | -955  | -870  | mV    | V <sub>IN</sub> = V <sub>IH</sub> (Max) Loading with |                                         |  |  |  |  |

| V <sub>OL</sub>  | Output LOW Voltage   | -1830 | -1705 | -1620 | mV    | or V <sub>IL</sub> (Min)                             | $50\Omega$ to $-2.0V$                   |  |  |  |  |

| V <sub>OHC</sub> | Output HIGH Voltage  | -1035 |       |       | mV    | V <sub>IN</sub> = V <sub>IH</sub> (Min) Loading with |                                         |  |  |  |  |

| V <sub>OLC</sub> | Output LOW Voltage   |       |       | -1610 | mV    | or V <sub>IL</sub> (Max) 50Ω to -2.0                 |                                         |  |  |  |  |

| V <sub>IH</sub>  | Input HIGH Voltage   | -1165 |       | -870  | mV    | Guaranteed HIGH Signal                               |                                         |  |  |  |  |

|                  |                      |       |       |       |       | for All Inputs                                       |                                         |  |  |  |  |

| V <sub>IL</sub>  | Input LOW Voltage    | -1830 |       | -1475 | mV    | Guaranteed LOW Signal                                |                                         |  |  |  |  |

|                  |                      |       |       |       |       | for All Inputs                                       |                                         |  |  |  |  |

| I <sub>IL</sub>  | Input LOW Current    | 0.5   |       |       | μΑ    | $V_{IN} = V_{IL}$ (Min)                              | $V_{IN} = V_{IL}$ (Min)                 |  |  |  |  |

| I <sub>IH</sub>  | Input HIGH Current   |       |       | 240   | μΑ    | V <sub>IN</sub> = V <sub>IH</sub> (Max)              | V <sub>IN</sub> = V <sub>IH</sub> (Max) |  |  |  |  |

| I <sub>EE</sub>  | Power Supply Current | -122  |       | -65   | mA    | Inputs OPEN                                          | Inputs OPEN                             |  |  |  |  |

Note 3: The specified limits represent the "worst case" value for the parameter. Since these values normally occur at the temperature extremes, additional noise immunity and guardbanding can be achieved by decreasing the allowable system operating ranges. Conditions for testing shown in the tables are chosen to guarantee operation under "worst case" conditions.

## Commercial Version (Continued) DIP AC Electrical Characteristics

$V_{EE} = -4.2V$  to -5.7V,  $V_{CC} = V_{CCA} = GND$

| Symbol              | Parameter                                        | T <sub>C</sub> = | = 0°C | T <sub>C</sub> = | +25°C | $T_C = +85^{\circ}C$ |      | Units  | Conditions             |              |

|---------------------|--------------------------------------------------|------------------|-------|------------------|-------|----------------------|------|--------|------------------------|--------------|

| Symbol              | raiametei                                        | Min              | Max   | Min              | Max   | Min                  | Max  | Oilles | Con                    | uitions      |

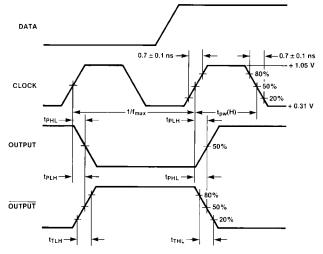

| f <sub>MAX</sub>    | Toggle Frequency                                 | 375              |       | 375              |       | 375                  |      | MHz    | Figures 2, 3           |              |

| t <sub>PLH</sub>    | Propagation Delay                                | 0.75             | 2.00  | 0.75             | 2.00  | 0.75                 | 2.00 | ns     |                        |              |

| t <sub>PHL</sub>    | CP <sub>C</sub> to Output                        | 0.75             | 2.00  | 0.75             | 2.00  | 0.75                 | 2.00 | 115    | Figures 1, 3           |              |

| t <sub>PLH</sub>    | Propagation Delay                                | 0.75             | 2.00  | 0.75             | 2.00  | 0.75                 | 2.00 | ns     | Tigules 1, 3           |              |

| t <sub>PHL</sub>    | CP <sub>n</sub> to Output                        | 0.73             | 2.00  | 0.73             | 2.00  | 0.73                 | 2.00 | 115    |                        |              |

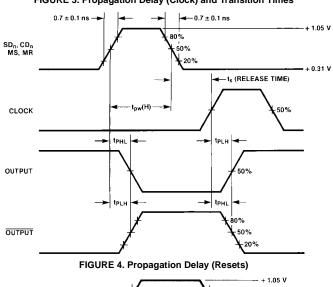

| t <sub>PLH</sub>    | Propagation Delay                                | 0.70             | 1.70  | 0.70             | 1.70  | 0.70                 | 1.80 |        | $CP_n$ , $CP_C = L$    |              |

| $t_{PHL}$           | CD <sub>n</sub> , SD <sub>n</sub> to Output      | 0.70             | 1.70  | 0.70             | 1.70  | 0.70                 | 1.00 | ns     | or n, or c - L         |              |

| t <sub>PLH</sub>    |                                                  | 0.70             | 2.00  | 0.70             | 2.00  | 0.70                 | 2.00 | 113    | $CP_n$ , $CP_C = H$    |              |

| t <sub>PHL</sub>    |                                                  | 0.70             | 2.00  | 0.70             | 2.00  | 0.70                 | 2.00 |        | or n, or c = 11        | Figures 1, 4 |

| t <sub>PLH</sub>    | Propagation Delay                                | 1.10             | 2.60  | 1.10             | 2.60  | 1.10                 | 2.60 |        | $CP_n$ , $CP_C = L$    | rigules 1, 4 |

| t <sub>PHL</sub>    | MS, MR to Output                                 | 1.10             | 2.00  | 1.10             | 2.00  | 1.10                 | 2.00 | ns     | 01 h, 01 C = L         |              |

| t <sub>PLH</sub>    |                                                  | 1.10             | 2.80  | 1.10             | 2.80  | 1.10                 | 2.80 | 1      | $CP_n$ , $CP_C = H$    |              |

| t <sub>PHL</sub>    |                                                  | 0                | 2.00  | 0                | 2.00  |                      | 2.00 |        | o. <sub>h</sub> , o. c |              |

| $t_{TLH}$           | Transition Time                                  | 0.35             | 1.30  | 0.35             | 1.30  | 0.35                 | 1.30 | ns     | Figures 1, 3, 4        |              |

| t <sub>THL</sub>    | 20% to 80%, 80% to 20%                           |                  |       |                  |       |                      |      |        | ga. cc ., c, .         |              |

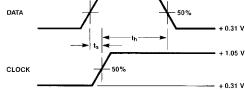

| t <sub>S</sub>      | Setup Time                                       |                  |       |                  |       |                      |      |        | Figure 5               |              |

|                     | D <sub>n</sub>                                   | 0.40             |       | 0.40             |       | 0.40                 |      | ns     | r igure o              |              |

|                     | CD <sub>n</sub> , SD <sub>n</sub> (Release Time) | 1.30             |       | 1.30             |       | 1.30                 |      | 1.0    | Figure 4               |              |

|                     | MS, MR (Release Time)                            | 2.30             |       | 2.30             |       | 2.30                 |      |        | rigule 4               |              |

| t <sub>H</sub>      | Hold Time D <sub>n</sub>                         | 0.5              |       | 0.5              |       | 0.7                  |      | ns     | Figure 5               |              |

| t <sub>PW</sub> (H) | Pulse Width HIGH                                 |                  |       |                  |       |                      |      |        | Figures 3, 4           |              |

|                     | $CP_n$ , $CP_C$ , $CD_n$ ,                       | 2.00             |       | 2.00             |       | 2.00                 |      | ns     |                        |              |

|                     | SD <sub>n</sub> , MR, MS                         |                  |       |                  |       |                      |      |        |                        |              |

## **SOIC and PLCC AC Electrical Characteristics**

$V_{\mbox{\footnotesize EE}} = -4.2 \mbox{\footnotesize V}$  to  $-5.7 \mbox{\footnotesize V}, \ \mbox{\footnotesize $V_{\mbox{\footnotesize CC}} = V_{\mbox{\footnotesize CCA}} = \mbox{\footnotesize GND}}$

| Symbol                               | Parameter                                                                                       | T <sub>C</sub> = | $T_C = 0^{\circ}C$ |              | $T_C = +25^{\circ}C$ |              | $T_C = +85^{\circ}C$ |       | Conditions                            |               |  |

|--------------------------------------|-------------------------------------------------------------------------------------------------|------------------|--------------------|--------------|----------------------|--------------|----------------------|-------|---------------------------------------|---------------|--|

| Syllibol                             | r ai ailletei                                                                                   | Min              | Max                | Min          | Max                  | Min          | Max                  | Units | Conditions                            |               |  |

| f <sub>MAX</sub>                     | Toggle Frequency                                                                                | 400              |                    | 400          |                      | 400          |                      | MHz   | Figures 2, 3                          |               |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay CP <sub>C</sub> to Output                                                     | 0.75             | 1.80               | 0.75         | 1.80                 | 0.75         | 1.80                 | ns    | Figures 1, 3                          |               |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay CP <sub>n</sub> to Output                                                     | 0.75             | 1.80               | 0.75         | 1.80                 | 0.75         | 1.80                 | ns    | rigures 1, 3                          |               |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay CD <sub>n</sub> , SD <sub>n</sub> to Output                                   | 0.70             | 1.50               | 0.70         | 1.50                 | 0.70         | 1.60                 | ns    | CP <sub>n</sub> , CP <sub>C</sub> =L  |               |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> |                                                                                                 | 0.80             | 1.80               | 0.70         | 1.80                 | 0.70         | 1.80                 | 110   | $CP_n$ , $CP_C = H$                   | Figures 1, 4  |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay MS, MR to Output                                                              | 1.10             | 2.40               | 1.10         | 2.40                 | 1.10         | 2.40                 | ns    | $CP_n$ , $CP_C = L$                   | 1.194.00 1, 1 |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> |                                                                                                 | 1.10             | 2.60               | 1.10         | 2.60                 | 1.10         | 2.60                 |       | CP <sub>n</sub> , CP <sub>C</sub> = H |               |  |

| t <sub>TLH</sub>                     | Transition Time<br>20% to 80%, 80% to 20%                                                       | 0.35             | 1.10               | 0.35         | 1.10                 | 0.35         | 1.10                 | ns    | Figures 1, 3, 4                       |               |  |

| t <sub>S</sub>                       | Setup Time<br>D <sub>n</sub>                                                                    | 0.30             |                    | 0.30         |                      | 0.30         |                      |       | Figure 5                              |               |  |

|                                      | CD <sub>n</sub> , SD <sub>n</sub> (Release Time) MS, MR (Release Time)                          | 1.20<br>2.20     |                    | 1.20<br>2.20 |                      | 1.20<br>2.20 |                      | ns    | Figure 4                              |               |  |

| t <sub>H</sub>                       | Hold Time D <sub>n</sub>                                                                        | 0.5              | •                  | 0.5          | •                    | 0.7          |                      | ns    | Figure 5                              | Figure 5      |  |

| t <sub>PW</sub> (H)                  | Pulse Width HIGH CP <sub>n</sub> , CP <sub>C</sub> , CD <sub>n</sub> , SD <sub>n</sub> , MR, MS | 2.00             |                    | 2.00         |                      | 2.00         |                      | ns    | Figures 3, 4                          |               |  |

## Commercial Version (Continued)

| 0                 | D                                           | T <sub>C</sub> = | = 0°C | T <sub>C</sub> = | +25°C | $T_C = +85^{\circ}C$ |      | 11-21- | Conditions                           |              |

|-------------------|---------------------------------------------|------------------|-------|------------------|-------|----------------------|------|--------|--------------------------------------|--------------|

| Symbol            | Parameter                                   | Min              | Max   | Min              | Max   | Min                  | Max  | Units  | Cond                                 | itions       |

| t <sub>PLH</sub>  | Propagation Delay                           | 0.75             | 1.40  | 0.75             | 1.40  | 0.80                 | 1.50 | ns     |                                      |              |

| t <sub>PHL</sub>  | CP <sub>C</sub> to Output                   | 0.75             | 1.40  | 0.75             | 1.40  | 0.60                 | 1.50 | 115    | Figures 1, 3 PLCC Only               |              |

| t <sub>PLH</sub>  | Propagation Delay                           | 0.70             | 1.40  | 0.75             | 1.40  | 0.80                 | 1.50 | ns     |                                      |              |

| t <sub>PHL</sub>  | CP <sub>n</sub> to Output                   | 0.70             | 1.40  | 0.75             | 1.40  | 0.00                 | 1.50 | 113    |                                      |              |

| t <sub>PLH</sub>  | Propagation Delay                           | 0.70             | 1.50  | 0.70             | 1.50  | 0.80                 | 1.60 |        | CP <sub>n</sub> , CP <sub>C</sub> =L |              |

| t <sub>PHL</sub>  | CD <sub>n</sub> , SD <sub>n</sub> to Output | 00               |       | 0.10             |       | 0.00                 | 1.00 | ns     | PLCC Only                            |              |

| t <sub>PLH</sub>  |                                             | 0.80             | 1.70  | 0.80             | 1.70  | 0.80                 | 1.80 |        | $CP_n$ , $CP_C = H$                  |              |

| t <sub>PHL</sub>  |                                             | 0.00             | 0     | 0.00             | 0     | 0.00                 | 1.00 |        | PLCC Only                            | Figures 1, 4 |

| t <sub>PLH</sub>  | Propagation Delay                           | 1.10             | 2.00  | 1.10             | 2.00  | 1.20                 | 2.10 |        | $CP_n$ , $CP_C = L$                  | ga. 00 ., .  |

| t <sub>PHL</sub>  | MS, MR to Output                            | 0                | 2.00  |                  | 2.00  | 1.20                 | 20   | ns     | PLCC Only                            |              |

| t <sub>PLH</sub>  |                                             | 1.20             | 2.10  | 1.20             | 2.10  | 1.30                 | 2.20 | 110    | $CP_n$ , $CP_C = H$                  |              |

| t <sub>PHL</sub>  |                                             | 1.20             | 20    | 20               | 20    | 1.00                 | 2.20 |        | PLCC Only                            |              |

| toshl             | Maximum Skew Common Edge                    |                  |       |                  |       |                      |      |        | PLCC Only                            |              |

|                   | Output-to-Output Variation                  |                  | 100   |                  | 100   |                      | 100  | ps     | (Note 4)                             |              |

|                   | Common Clock to Output Path                 |                  |       |                  |       |                      |      |        |                                      |              |

| toshl             | Maximum Skew Common Edge                    |                  |       |                  |       |                      |      |        | PLCC Only                            |              |

|                   | Output-to-Output Variation                  |                  | 235   |                  | 235   |                      | 235  | ps     | (Note 4)                             |              |

|                   | CP <sub>n</sub> to Output Path              |                  |       |                  |       |                      |      |        |                                      |              |

| t <sub>OSLH</sub> | Maximum Skew Common Edge                    |                  |       |                  |       |                      |      |        | PLCC Only                            |              |

|                   | Output-to-Output Variation                  |                  | 120   |                  | 120   |                      | 120  | ps     | (Note 4)                             |              |

|                   | Common Clock to Output Path                 |                  |       |                  |       |                      |      |        |                                      |              |

| t <sub>OSLH</sub> | Maximum Skew Common Edge                    |                  |       |                  |       |                      |      |        | PLCC Only                            |              |

|                   | Output-to-Output Variation                  |                  | 275   |                  | 275   |                      | 275  | ps     | (Note 4)                             |              |

|                   | CP <sub>n</sub> to Output Path              |                  |       |                  |       |                      |      |        |                                      |              |

| t <sub>OST</sub>  | Maximum Skew Opposite Edge                  |                  |       |                  |       |                      |      | ps     | PLCC Only                            |              |

|                   | Output-to-Output Variation                  |                  | 125   |                  | 125   |                      | 125  |        | (Note 4)                             |              |

|                   | Common Clock to Output Path                 |                  |       |                  |       |                      |      |        |                                      |              |

| t <sub>OST</sub>  | Maximum Skew Opposite Edge                  |                  |       |                  |       |                      |      | ps     | PLCC Only                            |              |

|                   | Output-to-Output Variation                  |                  | 265   |                  | 265   |                      | 265  |        | (Note 4)                             |              |

|                   | CP <sub>n</sub> to Output Path              |                  |       |                  |       |                      |      |        |                                      |              |

| t <sub>PS</sub>   | Maximum Skew                                |                  |       |                  |       |                      |      |        | PLCC Only                            | <u></u>      |

|                   | Pin (Signal) Transition Variation           |                  | 90    |                  | 90    |                      | 90   | ps     | (Note 4)                             |              |

|                   | Common Clock to Output Path                 |                  |       |                  |       |                      |      |        |                                      |              |

| t <sub>PS</sub>   | Maximum Skew                                |                  |       |                  |       |                      |      |        | PLCC Only                            |              |

|                   | Pin (Signal) Transition Variation           |                  | 90    |                  | 90    |                      | 90   | ps     | (Note 4)                             |              |

|                   | CP <sub>n</sub> to Output Path              |                  |       |                  |       |                      |      |        |                                      |              |

Note 4: Output-to-Output Skew is defined as the absolute value of the difference between the actual propagation delay for any outputs within the same packaged device. The specifications apply to any outputs switching in the same direction either HIGH-to-LOW (toshl), or LOW-to-HIGH (tosl), or in opposite directions both HL and LH (tost). Parameters tost and tost guaranteed by design.

## **Industrial Version**

## PLCC DC Electrical Characteristics (Note 5) $V_{EE} = -4.2 V$ to -5.7 V, $V_{CC} = V_{CCA} = GND$ , $T_C = -40 ^{\circ} C$ to $+85 ^{\circ} C$

| Symbol           | Parameter            | T <sub>C</sub> = - | -40°C | T <sub>C</sub> = 0°C | to +85°C | Units | Conditions                                           |                                         |  |  |

|------------------|----------------------|--------------------|-------|----------------------|----------|-------|------------------------------------------------------|-----------------------------------------|--|--|

| Oyboi            |                      | Min                | Max   | Min                  | Max      | Onno  |                                                      |                                         |  |  |

| V <sub>OH</sub>  | Output HIGH Voltage  | -1085              | -870  | -1025                | -870     | mV    | V <sub>IN</sub> = V <sub>IH</sub> (Max)              | Loading with                            |  |  |

| V <sub>OL</sub>  | Output LOW Voltage   | -1830              | -1575 | -1830                | -1620    | mV    | or V <sub>IL</sub> (Min)                             | $50\Omega$ to $-2.0V$                   |  |  |

| V <sub>OHC</sub> | Output HIGH Voltage  | -1095              |       | -1035                |          | mV    | V <sub>IN</sub> = V <sub>IH</sub> (Min) Loading with |                                         |  |  |

| V <sub>OLC</sub> | Output LOW Voltage   |                    | -1565 |                      | -1610    | mV    | or $V_{IL}$ (Max) 50 $\Omega$ to -2.0                |                                         |  |  |

| V <sub>IH</sub>  | Input HIGH Voltage   | -1170              | -870  | -1165                | -870     | mV    | Guaranteed HIGH Signal                               | Guaranteed HIGH Signal                  |  |  |

|                  |                      |                    |       |                      |          |       | for All Inputs                                       |                                         |  |  |

| V <sub>IL</sub>  | Input LOW Voltage    | -1830              | -1480 | -1830                | 1475     | mV    | Guaranteed LOW Signal                                |                                         |  |  |

|                  |                      |                    |       |                      |          |       | for All Inputs                                       |                                         |  |  |

| I <sub>IL</sub>  | Input LOW Current    | 0.5                |       | 0.5                  |          | μΑ    | V <sub>IN</sub> = V <sub>IL</sub> (Min)              |                                         |  |  |

| I <sub>IH</sub>  | Input HIGH Current   |                    | 300   |                      | 240      | μΑ    | V <sub>IN</sub> = V <sub>IH</sub> (Max)              | V <sub>IN</sub> = V <sub>IH</sub> (Max) |  |  |

| I <sub>FF</sub>  | Power Supply Current | -122               | -60   | -122                 | -65      | mA    | Inputs Open                                          |                                         |  |  |

Note 5: The specified limits represent the "worst case" value for the parameter. Since these values normally occur at the temperature extremes, additional noise immunity and guardbanding can be achieved by decreasing the allowable system operating ranges. Conditions for testing shown in the tables are chosen to guarantee operation under "worst case" conditions.

#### **PLCC AC Electrical Characteristics**

$\rm V_{\mbox{\footnotesize EE}} = -4.2 \mbox{\footnotesize V}$  to  $-5.7 \mbox{\footnotesize V}, \mbox{\footnotesize $V_{\mbox{\footnotesize CC}} = V_{\mbox{\footnotesize CCA}} = \mbox{\footnotesize GND}}$

| Symbol                               | Parameter                                                                                       | T <sub>C</sub> = | -40°C | T <sub>C</sub> = | +25°C | T <sub>C</sub> = | +85°C | Units | Conditions                            |              |  |

|--------------------------------------|-------------------------------------------------------------------------------------------------|------------------|-------|------------------|-------|------------------|-------|-------|---------------------------------------|--------------|--|

| Symbol                               | Farameter                                                                                       | Min              | Max   | Min              | Max   | Min              | Max   | Units | Cond                                  | itions       |  |

| f <sub>MAX</sub>                     | Toggle Frequency                                                                                | 375              |       | 400              |       | 400              |       | MHz   | Figures 2, 3                          |              |  |

| t <sub>PLH</sub>                     | Propagation Delay CP <sub>C</sub> to Output                                                     | 0.75             | 1.80  | 0.75             | 1.80  | 0.75             | 1.80  | ns    | Figures 1, 3                          |              |  |

| t <sub>PLH</sub>                     | Propagation Delay CP <sub>n</sub> to Output                                                     | 0.70             | 1.80  | 0.75             | 1.80  | 0.75             | 1.80  | ns    |                                       |              |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay CD <sub>n</sub> , SD <sub>n</sub> to Output                                   | 0.60             | 1.50  | 0.70             | 1.50  | 0.70             | 1.60  | ns    | $CP_n$ , $CP_C = L$                   |              |  |

| t <sub>PLH</sub>                     |                                                                                                 | 0.70             | 1.80  | 0.70             | 1.80  | 0.70             | 1.80  | 115   | CP <sub>n</sub> , CP <sub>C</sub> = H | Figures 1, 4 |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay MS, MR to Output                                                              | 1.10             | 2.40  | 1.10             | 2.40  | 1.10             | 2.40  | ns    | $CP_n$ , $CP_C = L$                   | rigules 1, 4 |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> |                                                                                                 | 1.10             | 2.60  | 1.10             | 2.60  | 1.10             | 2.60  |       | $CP_n$ , $CP_C = H$                   |              |  |

| t <sub>TLH</sub><br>t <sub>THL</sub> | Transition Time<br>20% to 80%, 80% to 20%                                                       | 0.20             | 1.40  | 0.35             | 1.10  | 0.35             | 1.10  | ns    | Figures 1, 3, 4                       |              |  |

| t <sub>S</sub>                       | Setup Time<br>D <sub>n</sub>                                                                    | 1.00             |       | 0.30             |       | 0.30             |       |       | Figure 5                              |              |  |

|                                      | CD <sub>n</sub> , SD <sub>n</sub> (Release Time)<br>MS, MR (Release Time)                       | 1.50<br>2.50     |       | 1.20<br>2.20     |       | 1.20<br>2.20     |       | ns    | Figure 4                              |              |  |

| t <sub>H</sub>                       | Hold Time D <sub>n</sub>                                                                        | 0.7              |       | 0.5              |       | 0.7              |       | ns    | Figure 5                              |              |  |

| t <sub>PW</sub> (H)                  | Pulse Width HIGH CP <sub>n</sub> , CP <sub>C</sub> , CD <sub>n</sub> , SD <sub>n</sub> , MR, MS | 2.00             |       | 2.00             |       | 2.00             |       | ns    | Figures 3, 4                          |              |  |

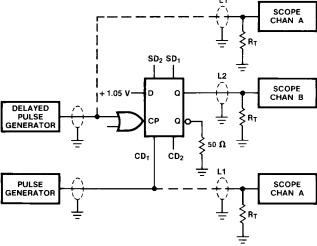

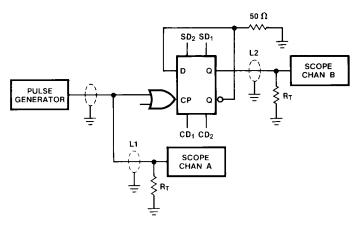

## **Test Circuits**

FIGURE 1. AC Test Circuit

#### Notes

$V_{CC},\,V_{CCA}=+2V,\,V_{EE}=-2.5V$

L1 and L2 = Equal length  $50\Omega$  impedance lines

$R_T = 50\Omega$  terminator internal to scope

. Decoupling 0.1  $\mu\text{F}$  from GND to  $\text{V}_{\text{CC}}$  and  $\text{V}_{\text{EE}}$

All unused outputs are loaded with  $50\Omega$  to GND

$C_L$  = Fixture and stray capacitance  $\leq$  3 pF

FIGURE 2. Toggle Frequency Test Circuit

## **Switching Waveforms**

FIGURE 3. Propagation Delay (Clock) and Transition Times

FIGURE 5. Data Setup and Hold Time

#### Note:

$t_{\mbox{\scriptsize S}}$  is the minimum time before the transition of the clock that information must be present at the data input.

$t_{\mbox{\scriptsize H}}$  is the minimum time after the transition of the clock that information must remain unchanged at the data input.

#### Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

28-Lead Plastic Lead Chip Carrier (PLCC), JEDEC MO-047, 0.450 Square Package Number V28A

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com