# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceed the OCM data sheet.

# **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-35835

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# **MOTOROLA**

# **HEX D FLIP-FLOP**

The LSTTL/MSI SN54/74LS174 is a high speed Hex D Flip-Flop. The device is used primarily as a 6-bit edge-triggered storage register. The information on the D inputs is transferred to storage during the LOW to HIGH clock transition. The device has a Master Reset to simultaneously clear all flip-flops. The LS174 is fabricated with the Schottky barrier diode process for high speed and is completely compatible with all Motorola TTL families.

- Edge-Triggered D-Type Inputs

- Buffered-Positive Edge-Triggered Clock

- · Asynchronous Common Reset

- Input Clamp Diodes Limit High Speed Termination Effects

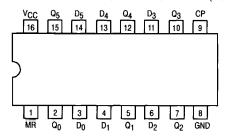

### **CONNECTION DIAGRAM DIP (TOP VIEW)**

NOTE: The Flatpak version has the same pinouts (Connection Diagram) as the Dual In-Line Package.

### PIN NAMES

### LOADING (Note a)

|                                |                                      | HIGH     | FOM          |

|--------------------------------|--------------------------------------|----------|--------------|

| D <sub>0</sub> -D <sub>5</sub> | Data Inputs                          | 0.5 U.L. | 0.25 U.L.    |

| CP                             | Clock (Active HIGH Going Edge) Input | 0.5 U.L. | 0.25 U.L.    |

| MR                             | Master Reset (Active LOW) Input      | 0.5 U.L. | 0.25 U.L.    |

| $Q_0 - Q_5$                    | Outputs (Note b)                     | 10 U.L.  | 5 (2.5) U.L. |

| OTCO                           |                                      |          |              |

#### NOTES

- a. 1 TTL Unit Load (U.L.) = 40  $\mu$ A HIGH/1.6 mA LOW.

- b. The Output LOW drive factor is 2.5 U.L. for Military (54) and 5 U.L. for Commercial (74) Temperature Ranges.

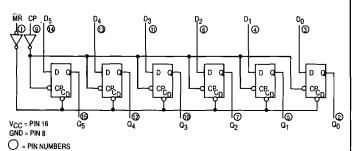

## **LOGIC DIAGRAM**

# SN54/74LS174

# HEX D FLIP-FLOP LOW POWER SCHOTTKY

J SUFFIX CERAMIC CASE 620-09

N SUFFIX PLASTIC CASE 648-08

D SUFFIX SOIC CASE 751B-03

### ORDERING INFORMATION

SN54LSXXXJ Ceramic SN74LSXXXN Plastic SN74LSXXXD SOIC

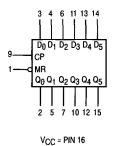

# LOGIC SYMBOL

GND = PIN 8

### SN54/74LS174

### **FUNCTIONAL DESCRIPTION**

The LS174 consists of six edge-triggered D flip-flops with individual D inputs and Q outputs. The Clock (CP) and Master Reset ( $\overline{MR}$ ) are common to all flip-flops.

Each D input's state is transferred to the corresponding flipflop's output following the LOW to HIGH Clock (CP) transition. A LOW input to the Master Reset ( $\overline{\text{MR}}$ ) will force all outputs LOW independent of Clock or Data inputs. The LS174 is useful for applications where the true output only is required and the Clock and Master Reset are common to all storage elements.

### **TRUTH TABLE**

| Inputs (t = n, MR = H) | Outputs (t = n+1) Note 1 |  |  |  |  |

|------------------------|--------------------------|--|--|--|--|

| D                      | Q                        |  |  |  |  |

| Н                      | н                        |  |  |  |  |

| L                      | L                        |  |  |  |  |

Note 1: t = n + 1 indicates conditions after next clock.

#### **GUARANTEED OPERATING RANGES**

| Symbol | Parameter                           |          | Min         | Тур        | Max         | Unit |

|--------|-------------------------------------|----------|-------------|------------|-------------|------|

| VCC    | Supply Voltage                      | 54<br>74 | 4.5<br>4.75 | 5.0<br>5.0 | 5.5<br>5.25 | V    |

| TA     | Operating Ambient Temperature Range | 54<br>74 | -55<br>0    | 25<br>25   | 125<br>70   | °C   |

| loн    | Output Current High                 | 54, 74   |             |            | -0.4        | mA   |

| IOL    | Output Current — Low                | 54<br>74 |             |            | 4.0<br>8.0  | mA   |

### DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

|        |                                |        |     | Limits |      |      |                                                                                                                    |                                                                         |

|--------|--------------------------------|--------|-----|--------|------|------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Symbol | Parameter                      |        | Min | Тур    | Max  | Unit | Tes                                                                                                                | st Conditions                                                           |

| VIH    | Input HIGH Voltage             |        | 2.0 |        |      | ٧    | Guaranteed Input HIGH Voltage for All Inputs                                                                       |                                                                         |

|        | Input LOW Voltage              | 54     |     |        | 0.7  | v    | Guaranteed Input LOW Voltage for                                                                                   |                                                                         |

| VIL    |                                | 74     |     |        | 8.0  |      | All Inputs                                                                                                         |                                                                         |

| VIK    | Input Clamp Diode Voltage      |        |     | -0.65  | -1.5 | ٧    | V <sub>CC</sub> = MIN, I <sub>IN</sub> = -18 mA                                                                    |                                                                         |

| VOH    | Output HIGH Voltage            | 54     | 2.5 | 3.5    |      | ٧    | V <sub>CC</sub> = MIN, I <sub>OH</sub> = MAX, V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> per Truth Table |                                                                         |

|        |                                | 74     | 2.7 | 3.5    |      | ٧    |                                                                                                                    |                                                                         |

|        | 0 0                            | 54, 74 |     | 0.25   | 0.4  | ٧    | I <sub>OL</sub> = 4.0 mA                                                                                           | V <sub>CC</sub> = V <sub>CC</sub> MiN,                                  |

| VOL    | Output LOW Voltage             | 74     |     | 0.35   | 0.5  | ٧    |                                                                                                                    | V <sub>IN</sub> = V <sub>IL</sub> or V <sub>IH</sub><br>per Truth Table |

|        | Input HIGH Current             |        |     |        | 20   | μА   | V <sub>CC</sub> = MAX, V <sub>IN</sub>                                                                             | j = 2.7 V                                                               |

| lН     |                                |        |     |        | 0.1  | mA   | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 7.0 V                                                                     |                                                                         |

| IJL    | Input LOW Current              |        |     |        | -0.4 | mA   | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 0.4 V                                                                     |                                                                         |

| los    | Short Circuit Current (Note 1) |        | -20 |        | ~100 | mA   | V <sub>CC</sub> = MAX                                                                                              |                                                                         |

| lcc    | Power Supply Current           |        |     |        | 26   | mA   | V <sub>CC</sub> = MAX                                                                                              | _                                                                       |

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.

## SN54/74LS174

## AC CHARACTERISTICS (TA = 25°C)

|                                      |                                    | Limits |          |          |      |                         |

|--------------------------------------|------------------------------------|--------|----------|----------|------|-------------------------|

| Symbol                               | Parameter                          | Min    | Тур      | Max      | Unit | Test Conditions         |

| fMAX                                 | Maximum Input Clock Frequency      | 30     | 40       |          | MHz  |                         |

| <sup>t</sup> PHL                     | Propagation Delay, MR to Output    |        | 23       | 35       | ns   | V <sub>CC</sub> = 5.0 V |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Propagation Delay, Clock to Output |        | 20<br>21 | 30<br>30 | ns   | C <sub>L</sub> = 15 pF  |

## AC SETUP REQUIREMENTS (TA = 25°C)

|                  |                         |     | Limits |     |      |                         |

|------------------|-------------------------|-----|--------|-----|------|-------------------------|

| Symbol           | Parameter               | Min | Тур    | Max | Unit | Test Conditions         |

| tw               | Clock or MR Pulse Width | 20  |        |     | ns   |                         |

| ts               | Data Setup Time         | 20  |        |     | ns   | ,                       |

| th               | Data Hold Time          | 5.0 |        |     | ns   | V <sub>CC</sub> = 5.0 V |

| t <sub>rec</sub> | Recovery Time           | 25  |        |     | ns   |                         |

### **AC WAVEFORMS**

\*The shaded areas indicate when the input is permitted to change for predictable output performance.

T.3 V Trec

1.3 V

Figure 2. Master Reset to Output Delay, Master Reset Pulse Width, and Master Reset Recovery Time

Figure 1. Clock to Output Delays, Clock Pulse Width, Frequency, Setup and Hold Times Data to Clock

### **DEFINITIONS OF TERMS**

SETUP TIME (t<sub>s</sub>) — is defined as the minimum time required for the correct logic level to be present at the logic input prior to the clock transition from LOW to HIGH in order to be recognized and transferred to the outputs.

HOLD TIME  $(t_h)$  — is defined as the minimum time following the clock transition from LOW to HIGH that the logic level must be maintained at the input in order to ensure continued recog-

nition. A negative HOLD TIME indicates that the correct logic level may be released prior to the clock transition from LOW to HIGH and still be recognized.

RECOVERY TIME  $(t_{rec})$  — is defined as the minimum time required between the end of the reset pulse and the clock transition from LOW to HIGH in order to recognize and transfer HIGH Data to the Q outputs.