# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceed the OCM data sheet.

# **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-35835

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# 16K x 4 Static RAM

#### **Features**

- High speed

- 15 ns

- Output enable (OE) feature (CY7C166)

- CMOS for optimum speed/power

- · Low active power

- 633 mW

- · Low standby power

- 110 mW

- · TTL-compatible inputs and outputs

- · Automatic power-down when deselected

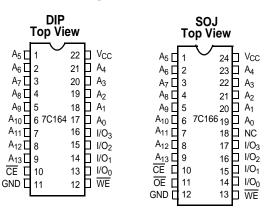

- CY7C164 is available in non Pb-free 22-pin (300-Mil)

Molded DIP, CY7C166 in non Pb-free 24-pin Molded SOJ

#### **Functional Description**

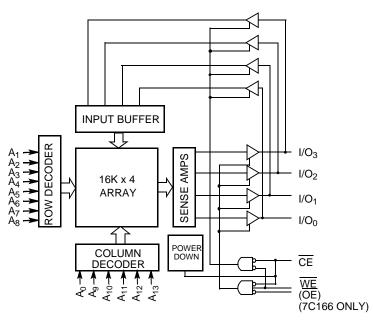

The CY7C164 and CY7C166 are high-performance CMOS static RAMs organized as 16,384 by 4 bits. Easy memory expansion is provided by an active LOW Chip Enable (CE) and tri-state drivers. The CY7C166 has an active LOW Output Enable (OE) feature. Both devices have an automatic power-down feature, reducing the power consumption by 65% when deselected.

Writing to the device is accomplished when the Chip Enable ( $\overline{\text{CE}}$ ) and Write  $\underline{\text{En}}$ able ( $\overline{\text{WE}}$ ) inputs are both LOW (and the Output Enable ( $\overline{\text{OE}}$ ) is LOW for the CY7C166). Data on the four input/output pins (I/O<sub>0</sub> through I/O<sub>3</sub>) is written into the memory location specified on the address pins (A<sub>0</sub> through A<sub>13</sub>).

Reading the device is accomplished by taking Chip Enable (CE) LOW (and OE LOW for CY7C166), while Write Enable (WE) remains HIGH. Under these conditions the contents of the memory location specified on the address pins will appear on the four data I/O pins.

The I/O pins stay in a high-impedance state when Chip Enable (CE) is HIGH (or Output Enable (OE) is HIGH for CY7C166). A die coat is used to insure alpha immunity.

### **Logic Block Diagram**

### **Pin Configurations**

#### **Selection Guide**

|                                   | CY7C164-15<br>CY7C166-15 | CY7C164-25<br>CY7C166-25 |

|-----------------------------------|--------------------------|--------------------------|

| Maximum Access Time (ns)          | 15                       | 25                       |

| Maximum Operating Current (mA)    | 115                      | 105                      |

| Maximum CMOS Standby Current (mA) | 20                       | 20                       |

# **Maximum Ratings**

| (Above which the useful life may be i lines, not tested.)    | mpaired. For user guide- |

|--------------------------------------------------------------|--------------------------|

| Storage Temperature                                          | 65°C to +150°C           |

| Ambient Temperature with Power Applied                       | 55°C to +125°C           |

| Supply Voltage to Ground Potential                           | 0.5V to +7.0V            |

| DC Voltage Applied to Outputs in High Z State <sup>[1]</sup> | 0.5V to +7.0V            |

| DC Input Voltage <sup>[1]</sup>                              | 0.5V to +7.0V            |

| Output Current into Outputs (LOW)                      | 20 mA    |

|--------------------------------------------------------|----------|

| Static Discharge Voltage(per MIL-STD-883, Method 3015) | . >2001V |

| Latch-Up Current                                       | >200 mA  |

# **Operating Range**

| Range      | Ambient<br>Temperature | V <sub>CC</sub> |

|------------|------------------------|-----------------|

| Commercial | 0°C to +70°C           | 5V ± 10%        |

# **Electrical Characteristics** Over the Operating Range

|                  |                                                   |                                                                                                     |            | -15             |            | -25             |      |

|------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------|-----------------|------------|-----------------|------|

| Parameter        | Description                                       | Test Conditions                                                                                     | Min.       | Max.            | Min.       | Max.            | Unit |

| V <sub>OH</sub>  | Output HIGH Voltage                               | $V_{CC} = Min., I_{OH} = -4.0 \text{ mA}$                                                           | 2.4        |                 | 2.4        |                 | V    |

| V <sub>OL</sub>  | Output LOW Voltage                                | V <sub>CC</sub> = Min., I <sub>OL</sub> = 8.0 mA                                                    |            | 0.4             |            | 0.4             | V    |

| V <sub>IH</sub>  | Input HIGH Voltage                                |                                                                                                     | 2.2        | V <sub>CC</sub> | 2.2        | V <sub>CC</sub> | V    |

| V <sub>IL</sub>  | Input LOW Voltage[1]                              |                                                                                                     | -0.5       | 0.8             | -0.5       | 0.8             | V    |

| I <sub>IX</sub>  | Input Leakage Current                             | $GND \le V_I \le V_{CC}$                                                                            | <b>-</b> 5 | +5              | <b>-</b> 5 | +5              | μΑ   |

| l <sub>OZ</sub>  | Output Leakage Current                            | $GND \le V_O \le V_{CC}$ , Output Disabled                                                          | <b>-</b> 5 | +5              | <b>-</b> 5 | +5              | μΑ   |

| I <sub>CC</sub>  | V <sub>CC</sub> Operating Supply Current          | V <sub>CC</sub> = Max., I <sub>OUT</sub> = 0 mA                                                     |            | 115             |            | 105             | mA   |

| I <sub>SB1</sub> | Automatic CE<br>Power-Down Current <sup>[2]</sup> | Max. $V_{CC}$ , $\overline{CE} \ge V_{IH}$ ,<br>Min. Duty Cycle = 100%                              |            | 40              |            | 20              | mA   |

| I <sub>SB2</sub> | Automatic CE<br>Power-Down Current <sup>[2]</sup> | Max. $V_{CC}$ , $\overline{CE} \ge V_{CC} - 0.3V$ , $V_{IN} \ge V_{CC} - 0.3V$ or $V_{IN} \le 0.3V$ |            | 20              |            | 20              | mA   |

# Capacitance<sup>[3]</sup>

| Parameter        | Description        | Test Conditions                         | Max. | Unit |

|------------------|--------------------|-----------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$ | 10   | pF   |

| C <sub>OUT</sub> | Output Capacitance | $V_{CC} = 5.0V$                         | 10   | pF   |

- Minimum voltage is equal to -3.0V for pulse durations less than 30 ns.

A pull-up resistor to V<sub>CC</sub> on the CE input is required to keep the device deselected during V<sub>CC</sub> power-up, otherwise I<sub>SB</sub> will exceed values given.

Tested initially and after any design or process changes that may affect these parameters.

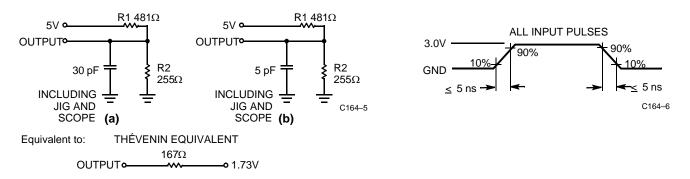

#### **AC Test Loads and Waveforms**

#### Switching Characteristics Over the Operating Range<sup>[4]</sup>

|                           |                                     |       | CY7C164-15<br>CY7C166-15 |      |      | 164-25<br>166-25 |      |

|---------------------------|-------------------------------------|-------|--------------------------|------|------|------------------|------|

| Parameter                 | Description                         |       | Min.                     | Max. | Min. | Max.             | Unit |

| READ CYCLE                | ·                                   |       |                          |      |      |                  |      |

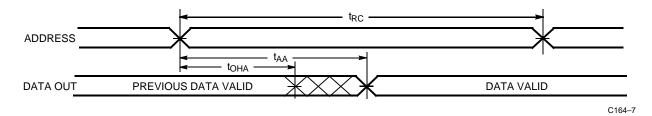

| t <sub>RC</sub>           | Read Cycle Time                     |       | 15                       |      | 25   |                  | ns   |

| t <sub>AA</sub>           | Address to Data Valid               |       |                          | 15   |      | 25               | ns   |

| t <sub>OHA</sub>          | Output Hold from Address Change     |       | 3                        |      | 5    |                  | ns   |

| t <sub>ACE</sub>          | CE LOW to Data Valid                |       |                          | 15   |      | 25               | ns   |

| t <sub>DOE</sub>          | OE LOW to Data Valid                | 7C166 |                          | 10   |      | 12               | ns   |

| t <sub>LZOE</sub>         | OE LOW to Low Z                     | 7C166 | 3                        |      | 3    |                  | ns   |

| t <sub>HZOE</sub>         | OE HIGH to High Z                   | 7C166 |                          | 8    |      | 10               | ns   |

| t <sub>LZCE</sub>         | CE LOW to Low Z <sup>[5]</sup>      |       | 3                        |      | 5    |                  | ns   |

| t <sub>HZCE</sub>         | CE HIGH to High Z <sup>[5, 6]</sup> |       |                          | 8    |      | 10               | ns   |

| t <sub>PU</sub>           | CE LOW to Power-Up                  |       | 0                        |      | 0    |                  | ns   |

| t <sub>PD</sub>           | CE HIGH to Power-Down               |       |                          | 15   |      | 20               | ns   |

| WRITE CYCLE <sup>[7</sup> | 7                                   |       | •                        | •    | •    | •                | •    |

| t <sub>WC</sub>           | Write Cycle Time                    |       | 15                       |      | 20   |                  | ns   |

| t <sub>SCE</sub>          | CE LOW to Write End                 |       | 12                       |      | 20   |                  | ns   |

| t <sub>AW</sub>           | Address Set-Up to Write End         |       | 12                       |      | 20   |                  | ns   |

| t <sub>HA</sub>           | Address Hold from Write End         |       | 0                        |      | 0    |                  | ns   |

| t <sub>SA</sub>           | Address Set-Up to Write Start       |       | 0                        |      | 0    |                  | ns   |

| t <sub>PWE</sub>          | WE Pulse Width                      |       | 12                       |      | 15   |                  | ns   |

| t <sub>SD</sub>           | Data Set-Up to Write End            |       | 10                       |      | 10   |                  | ns   |

| t <sub>HD</sub>           | Data Hold from Write End            |       | 0                        |      | 0    |                  | ns   |

| t <sub>LZWE</sub>         | WE HIGH to Low Z <sup>[5]</sup>     |       | 5                        |      | 5    |                  | ns   |

| t <sub>HZWE</sub>         | WE LOW to High Z <sup>[5, 6]</sup>  |       |                          | 7    |      | 7                | ns   |

#### Notes:

- 4. Test conditions assume signal transition time of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specified lo<sub>L</sub>/l<sub>OH</sub> and 30-pF load capacitance.

5. At any given temperature and voltage condition, t<sub>HZCE</sub> is less than t<sub>LZCE</sub> for any given device. These parameters are guaranteed by design and not 100% tested.

6. t<sub>HZCE</sub> and t<sub>HZWE</sub> are specified with C<sub>L</sub> = 5 pF as in part (b) in AC Test Loads. Transition is measured ±500 mV from steady-state voltage.

7. The internal write time of the memory is defined by the overlap of CE LOW and WE LOW. Both signals must be LOW to initiate a write and either signal can terminate a write by going HIGH. The data input set-up and hold timing should be referenced to the rising edge of the signal that terminates the write.

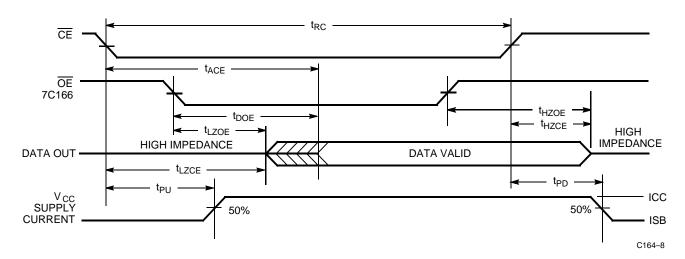

### **Switching Waveforms**

Read Cycle No. 1<sup>[8,9]</sup>

Read Cycle No.  $2^{[8,10]}$

- Notes:

8. WE is HIGH for read cycle.

9. Device is continuously selected, CE = V<sub>IL</sub>.(CY7C166: OE = V<sub>IL</sub> also).

10. Address valid prior to or coincident with CE transition LOW.

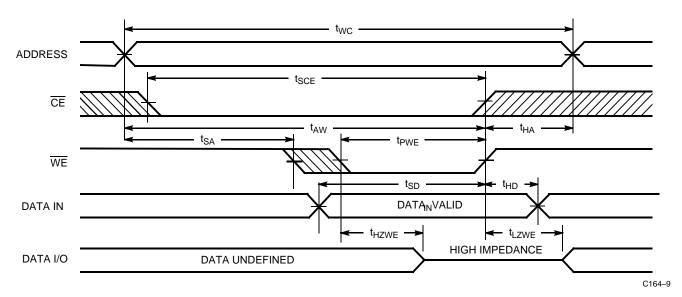

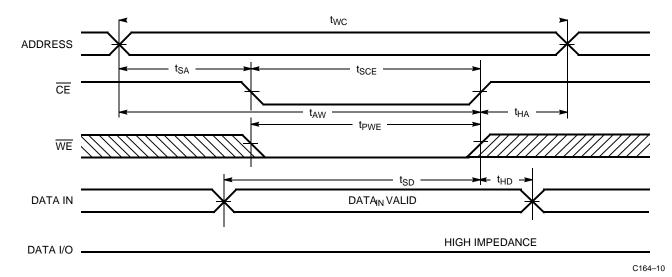

#### Switching Waveforms (continued)

Write Cycle No. 1(WE Controlled)<sup>[7,11]</sup>

# Write Cycle No. 2(CE Controlled)[7,11,12]

Notes: 11. CY7C166 only: Data I/O will be high-impedance if  $\overline{OE} = V_{IH}$ . 12. If  $\overline{CE}$  goes HIGH simultaneously with  $\overline{WE}$  HIGH, the output remains in a high-impedance state.

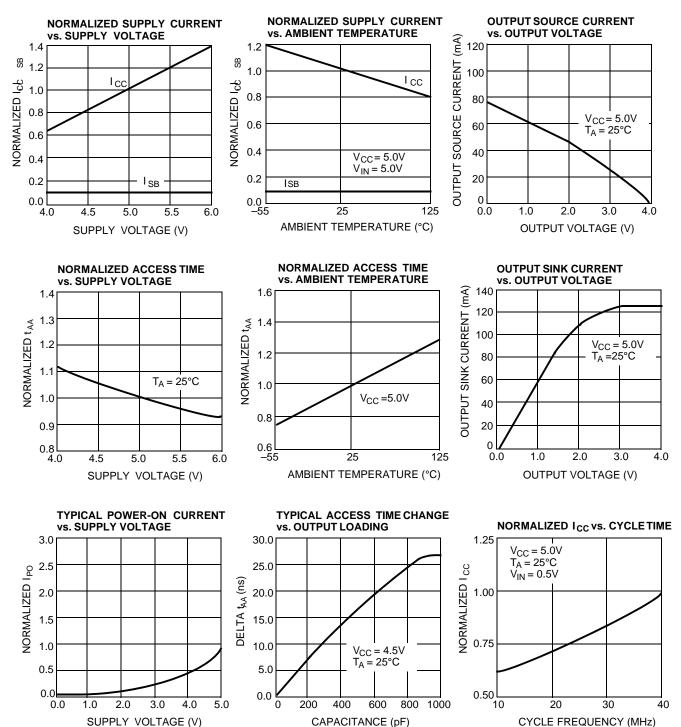

### Typical DC and AC Characteristics

#### **CY7C164 Truth Table**

| CE | WE | Input/Output | Mode                | Power                      |

|----|----|--------------|---------------------|----------------------------|

| Н  | Х  | High Z       | Deselect/Power-Down | Standby (I <sub>SB</sub> ) |

| L  | Н  | Data Out     | Read                | Active (I <sub>CC</sub> )  |

| L  | L  | Data In      | Write               | Active (I <sub>CC</sub> )  |

#### **CY7C166 Truth Table**

| CE | WE | OE | Input/Output | Mode                   | Power                      |

|----|----|----|--------------|------------------------|----------------------------|

| Н  | Х  | Х  | High Z       | Deselect/Power-Down    | Standby (I <sub>SB</sub> ) |

| L  | Н  | L  | Data Out     | Read                   | Active (I <sub>CC</sub> )  |

| L  | L  | Н  | Data In      | Write                  | Active (I <sub>CC</sub> )  |

| L  | Н  | Н  | High Z       | Select/Output Disabled | Active (I <sub>CC</sub> )  |

# **Address Designators**

| Address<br>Name | Address<br>Function | CY 7C164 Pin<br>Number | CY7C166 Pin<br>Number |

|-----------------|---------------------|------------------------|-----------------------|

| A5              | Х3                  | 1                      | 1                     |

| A6              | X4                  | 2                      | 2                     |

| A7              | X5                  | 3                      | 3                     |

| A8              | X6                  | 4                      | 4                     |

| A9              | X7                  | 5                      | 5                     |

| A10             | Y5                  | 6                      | 6                     |

| A11             | Y4                  | 7                      | 7                     |

| A12             | Y0                  | 8                      | 8                     |

| A13             | Y1                  | 9                      | 9                     |

| A0              | Y2                  | 17                     | 19                    |

| A1              | Y3                  | 18                     | 20                    |

| A2              | X0                  | 19                     | 21                    |

| A3              | X1                  | 20                     | 22                    |

| A4              | X2                  | 21                     | 23                    |

# **Ordering Information**

| Speed<br>(ns) | Ordering Code | Package<br>Diagram | Package Type                | Operating<br>Range |

|---------------|---------------|--------------------|-----------------------------|--------------------|

| 15            | CY7C164-15PC  | 51-85012           | 22-pin (300-Mil) Molded DIP | Commercial         |

|               | CY7C166-15VC  | 51-85030           | 24-pin (300-Mil) Molded SOJ |                    |

| 25            | CY7C164-25PC  | 51-85012           | 22-pin (300-Mil) Molded DIP | Commercial         |

|               | CY7C166-25VC  | 51-85030           | 24-pin (300-Mil) Molded SOJ |                    |

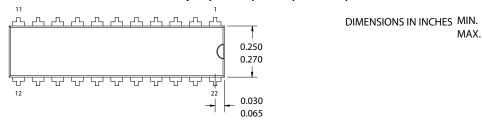

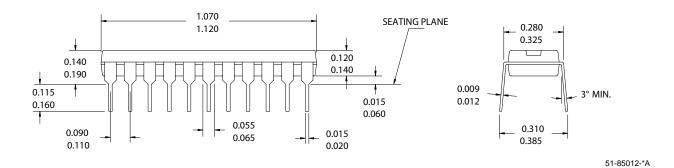

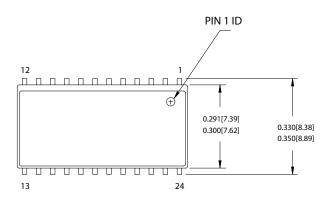

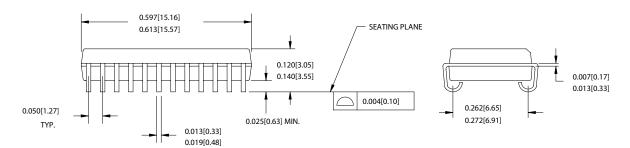

#### **Package Diagrams**

#### 22-pin (300-Mil) PDIP (51-85012)

#### 24-pin (300-mil) SOJ (51-85030)

DIMENSIONS IN INCHES[MM]

MIN. MAX.

REFERENCE JEDEC MO-088

PACKAGE WEIGHT 0.75gms

| PART #                |  |  |  |

|-----------------------|--|--|--|

| V24.3 STANDARD PKG.   |  |  |  |

| VZ24.3 LEAD FREE PKG. |  |  |  |

51-85030-\*B

# **Document History Page**

| Document Title: CY7C164/CY7C166 16K x 4 Static RAM Document Number: 38-05025 |         |               |                 |                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------|---------|---------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REV.                                                                         | ECN NO. | Issue<br>Date | Orig. of Change | Description of Change                                                                                                                                                                                                                                                                                                                                    |

| **                                                                           | 106811  | 09/10/01      | SZV             | Change from Spec number: 38-00032 to 38-05025                                                                                                                                                                                                                                                                                                            |

| *A                                                                           | 486744  | See ECN       | NXR             | Removed 20 ns and 35 ns speed bin from Product offering Removed 24-pin (300-Mil) Molded DIP package Changed the description of I <sub>IX</sub> from Input Load Current to Input Leakage Current in DC Electrical Characteristics table Removed I <sub>OS</sub> parameter from DC Electrical Characteristics table Updated the ordering information table |