## Advance Information

## **MPA17000 Serial EEPROM**

The MPA17C256 is an easy to use and cost effective serial configuration memory ideally suited for use with today's popular SRAM based FPGAs. The MPA17C256 is available in 8-pin PDIP and 20-pin SOIC and PLCC packages, adhering to industry standard pinouts. The device interfaces downstream FPGA(s) with a very simple enable, clock and data interface. The MPA17C256 is reprogrammable with no need for a higher programming "super voltage"; it may even be reprogrammed on board. The MPA17C256 also has user programmable RESET/OE polarity.

- EE Programmable 262,144 x 1 bit Serial Memories Designed to Store Configuration Programs for FPGAs

- Simple Interface to SRAM FPGAs

- Cascadable to Support Additional Configurations or Future Higher Density **FPGAs**

- Low Power CMOS EEPROM Process

- Programmable Reset Polarity

- Available in Space Efficient 8-Pin PDIP, 20-Pin SOIC and 20-Pin PLCC **Packages**

- In-System Programmable via 2-Wire Bus

#### Controlling the MPA17C256 Serial EEPROM

Most connections between the FPGA device and the Serial EEPROM are simple and self-explanatory:

- The DATA output of the MPA17C256 drives DIN of the FPGA devices

- The master FPGA DCLK output drives the CLK input of the MPA17C256

- . The CEO output of the first MPA17C256 drives the CE input of the next MPA17C256 in a cascade chain of EEPROMs.

- SER\_EN must be connected to VCC

- . CE enables the chip and is required to enable the DATA output pin

- RESET/OE is chip reset and is part of the DATA output enable structure

MPA17C256

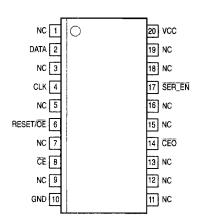

P SUFFIX 8-LEAD PLASTIC PACKAGE CASE 626-05

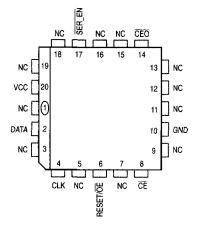

**DW SUFFIX** 20-LEAD PLASTIC SOIC WIDE PACKAGE CASE 751D-04

**FN SUFFIX** 20-LEAD PLCC PACKAGE CASE 775-02

#### PIN NAMES

| Pins                                       | Function                                                                                                                                            |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| DATA CLK RESET/OE CE VSS CEO SER_EN VCC NC | Data I/O Clock Reset Input and Output Enable Chip Enable Input Ground Chip Enable Output Programming Enable +4.5 to 6.0V Power Supply Not Connected |

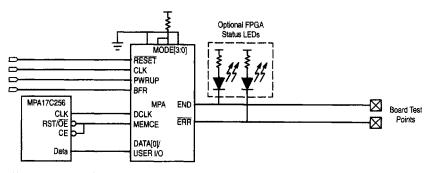

The simplest connection to a Motorola Programmable array (MPA) is shown below. In this configurations, the MEMCE output of the MPA enables the MPA17C256 and takes it out of reset. Shortly after, the first bit of configuration data will appear on DATA. Subsequent rising edges of DCLK bring out the next bits. For more complex connections, including cascading of EEPROMs and cascading of MPA devices, please consult the MPA databook (DL201/D).

This document contains information on a new product. Specifications and information herein are subject to change without notice.

© Motoroia, Inc. 1997

Figure 2-57. BFR Mode 2: 1-Bit (Serial) Data, External Address, External Clock

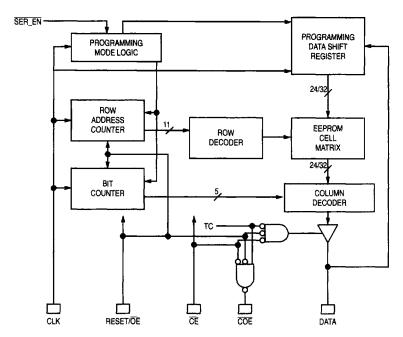

Figure 2-58. Block Diagram

Figure 2-59. 8-Lead DIP Pinout

Figure 2-60. 20-Lead SOIC Pinout

Figure 2-61. 20-Lead PLCC Pinout

#### Table 2-23. PIN DESCRIPTIONS

| PLCC/<br>SOIC | DIP | Name                       | vo  | Description                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|-----|----------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2             | 1   | DATA                       | 1/0 | Three-State DATA output for reading. Input/Output pin for programming                                                                                                                                                                                                                                                                                                                           |

| 4             | 2   | CLK                        | l   | Clock Input. Rising edge used to increment the internal address and bit counter for reading and programming                                                                                                                                                                                                                                                                                     |

| 6             | 3   | RESET/OE                   | ì   | RESET/Output Enable input (when SER_EN is High). A Low level on both the CE and RESET/OE inputs enables the data output driver. A High level on RESET/OE resets both the address and bit counters. The logic polarity of this input is programmable as either RESET/OE or RESET/OE. This document describes the pin as RESET/OE.                                                                |

|               |     | RESET Polarity<br>Selected | 1   | RESET Polarity Select Input. During programming, when CE is High, this input is used to determine the polarity of the pin when SER_EN is High.                                                                                                                                                                                                                                                  |

|               |     | WP                         | ı   | Write Protect (WP) input. When WP is Low, the entire memory can be written. When WP is enabled (High), the lowest 1/4 of the memory cannot be written; i.e., 64K in MPA17C256. Note that when WP is High, the chip will still acknowledge the receipt of data, but it will not write it into memory.                                                                                            |

| 8             | 4   | CE                         |     | Chip Enable input. Used for device selection only when SER_EN is High. A Low level on both CE and OE enables the data output driver. A High level on CE disables both the address and bit counters and forces the device into a low power mode. Note this pin will not enable/disable the device in 2-wire Serial mode (i.e., when SER_EN is Low).                                              |

|               |     |                            |     | During programming, and when $\overline{\text{CE}}$ is Low, the main array is read and written. When $\overline{\text{CE}}$ is High, the main array is deselected and a Serial WRITE operation will change the polarity of the RESET pin.                                                                                                                                                       |

| 10            | 5   | GND                        | -   | Ground Pin                                                                                                                                                                                                                                                                                                                                                                                      |

| 14            | 6   | CEO                        | 0   | Chip Enable Out output. This signal is asserted Low on the clock cycle following the last bit read from the memory. It will stay Low as long as $\overline{CE}$ and $\overline{OE}$ are both low. It will then follow $\overline{CE}$ until $\overline{OE}$ goes High. Thereafter, $\overline{CEO}$ will stay High until the entire PROM is read again and senses the status of RESET polarity. |

|               |     | A2                         | . 1 | Device selection input, A2. Used to enable (select) the device during programming. When SER_EN is Low, this pin MUST be at either a logic level '1' or '0' (i.e., not 3-state) and the A2 contents of the Device Address must match the condition of the pin for the device to be selected.                                                                                                     |

| 17            | 7   | SER_EN                     | 1   | Serial enable is normally high during FPGA loading operations. Bringing SER_EN Low, enables the two wire serial interface mode for programming.                                                                                                                                                                                                                                                 |

| 20            | 8   | Vcc                        | _   | +5V Power Supply input                                                                                                                                                                                                                                                                                                                                                                          |

#### Table 2-24, MAXIMUM RATINGS\*

| Symbol           | Parameter                                         | Value                         | Unit |

|------------------|---------------------------------------------------|-------------------------------|------|

| Vcc              | DC Supply Voltage (Referenced to GND)             | -0.5 to +7.0                  | V    |

| •                | Voltage Applied to Output in High Output State    | -0.1 to V <sub>CC</sub> +0.5V | ٧    |

| TA               | Operating Temperature Range (In Free-Air)         | -55 to +125                   | °C   |

| TSTG             | Storage Temperature Range                         | -65 to +150                   | °C   |

| T <sub>SOL</sub> | Maximum Soldering Temperature (10s @ 1/16in)      | 260                           | °C   |

| ESD              | R <sub>ZAP</sub> = 1.5K, C <sub>ZAP</sub> = 100pF | 2000                          | ٧    |

<sup>\*</sup> Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Recommended Operating Conditions.

#### Table 2-25. RECOMMENDED OPERATING CONDITIONS

| Symbol | Paramete                          | Min                                                   | Max          | Unit         |   |

|--------|-----------------------------------|-------------------------------------------------------|--------------|--------------|---|

| vcc    | Supply Voltage Relative to Ground | Commercial (-0 to +70°C)<br>Industrial (-40 to +85°C) | 4.75<br>4.50 | 5.25<br>5.50 | ٧ |

Table 2-26. DC CHARACTERISTICS OVER OPERATING CONDITIONS

| Symbol          | Parameter                                       |                          | Min          | Max          | Unit |

|-----------------|-------------------------------------------------|--------------------------|--------------|--------------|------|

| V <sub>IH</sub> | High Level Input Voltage                        |                          | 2.0          | Vcc          | V    |

| V <sub>IL</sub> | Low Level Input Voltage                         |                          | 0            | 0.8          | V    |

| VOH             | High Level Output Voltage                       | Commercial<br>Industrial | 3.86<br>3.76 |              | V    |

| V <sub>OL</sub> | Low Level Output Voltage                        | Commercial<br>Industrial |              | 0.32<br>0.37 | ٧    |

| ICCA            | Supply Current, Active Mode                     |                          | , ,          | 10           | mA   |

| IIL             | Input/Output Leakage Current (Vin = VCC or GND) |                          | -10          | 10           | μА   |

| lccs            | Supply Current, Standby Mode                    | Commercial<br>Industrial |              | 1 2          | mA   |

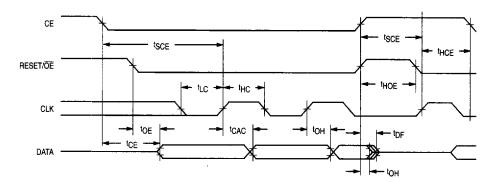

Figure 2-62. AC Characteristics Over Operating Conditions

Table 2-27. AC CHARACTERISTICS OVER OPERATING CONDITIONS (Note 1.)

|                  |                                                     | Comr | Commercial |     | industrial |      |

|------------------|-----------------------------------------------------|------|------------|-----|------------|------|

| Symbol           | Parameter                                           | Min  | Max        | Min | Max        | Unit |

| <sup>‡</sup> OE  | OE to Data Delay                                    |      | 110        |     | 150        | ns   |

| <sup>†</sup> CE  | ČĒ to Data Delay                                    |      | 50         |     | 50         | ns   |

| †CAC             | CLK to Data Delay                                   |      | 50         |     | 55         | ns   |

| tон              | Data Hold from CE, OE, or CLK                       | 0    |            | 0   |            | ns   |

| t <sub>DF</sub>  | CE or OE to Data Float Delay (Note 2.)              |      | 50         |     | 50         | ns   |

| †LC              | CLK Low Time                                        | 30   |            | 35  |            | ns   |

| <sup>t</sup> HC  | CLK High Time                                       | 30   |            | 35  |            | ns   |

| †SCE             | CE Setup Time to CLK (To Guarantee Proper Counting) | 45   |            | 50  |            | ns   |

| <sup>†</sup> HCE | CE Hold Time to CLK (To Guarantee Proper Counting)  | 0    |            | 5   |            | ns   |

| †HOE             | OE High Time (Guarantees Counter Is Reset)          | 50   |            | 60  |            | ns   |

| † <sub>max</sub> | Maximum Input Clock Frequency                       |      | 10         |     | 10         | MHz  |

<sup>1.</sup> AC test load = 50pF.

<sup>2.</sup> Float delays are measured with 5pF AC loads. Transition is measured ±500mV from steady state active levels.

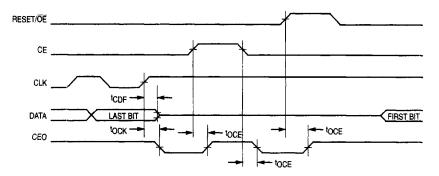

Figure 2-63. AC Characteristics Over Operating Conditions When Cascading

Table 2-28. AC CHARACTERISTICS OVER OPERATING CONDITIONS WHEN CASCADING

| Symbol           |                         |     | Commercial |     | Industrial |        |

|------------------|-------------------------|-----|------------|-----|------------|--------|

|                  | Parameter               | Min | Max        | Min | Max        | v Unit |

| <sup>t</sup> CDF | CLK to Data Float Delay |     | 50         |     | 50         | ns     |

| <sup>t</sup> OCK | CLK to CEO Delay        |     | 65         |     | 75         | ns     |

| <sup>t</sup> OCE | CE to CEO Delay         |     | 55         |     | 60         | ns     |

| <sup>t</sup> OOE | RESET/OE to CEO Delay   |     | 55         |     | 55         | ns     |

Table 2–29. DC CHARACTERISTICS ( $V_{CC} = 5.0V \pm 5\%$ )

| Symbol          | Parameter                | Min                   | Тур  | Max                   | Unit | Condition             |

|-----------------|--------------------------|-----------------------|------|-----------------------|------|-----------------------|

| Vcc             | Supply Voltage           | 4.75                  | 5.00 | 5.25                  | >    |                       |

| lcc             | Supply Current           |                       | 2.0  | 5.0                   | mA   | V <sub>CC</sub> = 5V  |

| ILL             | Input Leakage Current    |                       | 0.10 | 3.00                  | μА   | Vin = VCC or VSS      |

| <sup>I</sup> LO | Output Leakage Current   |                       | 0.05 | 3.00                  | μΑ   | Vout = VCC or VSS     |

| VIH             | High Level Input Voltage | V <sub>CC</sub> × 0.7 |      | V <sub>CC</sub> + 0.5 | ٧    |                       |

| VIL             | Low Level Input Voltage  | -0.5                  |      | 0.4                   | ٧    |                       |

| VOL             | Output Low Level Voltage |                       |      | 0.4                   | ٧    | I <sub>OL</sub> = 3mA |

Table 2–30. DC CHARACTERISTICS ( $V_{CC} = 3.3V \pm 10\%$ )

| Symbol          | Parameter                | Min                  | Тур  | Max                   | Unit | Condition               |

|-----------------|--------------------------|----------------------|------|-----------------------|------|-------------------------|

| VCC             | Supply Voltage           | 3.0                  | 3.3  | 3.6                   | ٧    |                         |

| lcc             | Supply Current           |                      | 2.0  | 3.0                   | mA   | V <sub>CC</sub> = 3.6V  |

| ILL             | Input Leakage Current    |                      | 0.10 | 3.00                  | μА   | Vin = VCC or VSS        |

| <sup>1</sup> LO | Output Leakage Current   |                      | 0.05 | 3.00                  | μΑ   | Vout = VCC or VSS       |

| VIH             | High Level Input Voltage | V <sub>CC</sub> ×0.7 |      | V <sub>CC</sub> + 0.5 | ٧    |                         |

| VIL             | Low Level Input Voltage  | -0.5                 |      | 0.2                   | ٧    |                         |

| VOL             | Output Low Level Voltage |                      |      | 0.4                   | ٧    | I <sub>OL</sub> = 2.1mA |

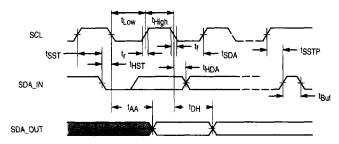

| Symbol             | Parameter                                                     | Min | Max | Unit |

|--------------------|---------------------------------------------------------------|-----|-----|------|

| <sup>f</sup> Clock | Clock Frequency, Clock                                        |     | 400 | kHz  |

| tLow               | Clock Pulse Width Low                                         | 1.2 |     | μs   |

| <sup>t</sup> High  | Clock Pulse Width High                                        | 0.8 |     | μs   |

| <sup>t</sup> AA    | Clock Low to Data Out Valid                                   | 0.1 | 0.9 | μs   |

| <sup>t</sup> Buf   | Time the Bus Must Be Free Before a New Transmission Can Start | 1.2 |     | μs   |

| tHST               | Start Hold Time                                               | 0.6 |     | μs   |

| †SST               | Start Setup Time                                              | 0.6 |     | μs   |

| tHDA               | Data In Hold Time                                             | 0   |     | μѕ   |

| <sup>†</sup> SDA   | Data In Setup Time                                            | 100 |     | ns   |

| t <sub>r</sub>     | Input Rise Time                                               |     | 0.3 | μs   |

| tf                 | Input Fall Time                                               |     | 300 | ns   |

| tSSTP              | Stop Setup Time                                               | 0.6 |     | μs   |

| †DH                | Data Out Hold Time                                            | 50  |     | ns   |

| tWR                | Write Cycle Time                                              |     | 10  | ms   |

Figure 2-64. Serial Data Timing Diagram

Table 2–32. AC CHARACTERISTICS ( $V_{CC} = 3.3V \pm 10\%$ )

| Symbol             | Parameter                                                     | Min | Max | Unit |

|--------------------|---------------------------------------------------------------|-----|-----|------|

| <sup>f</sup> Clock | Clock Frequency, Clock                                        |     | 100 | kHz  |

| †Low               | Clock Pulse Width Low                                         | 4.0 |     | μs   |

| <sup>t</sup> High  | Clock Pulse Width High                                        | 4.0 |     | μs   |

| t <sub>AA</sub>    | Clock Low to Data Out Valid                                   | 0.1 | 1.0 | μs   |

| tBuf               | Time the Bus Must Be Free Before a New Transmission Can Start | 4.5 |     | μs   |

| thst               | Start Hold Time                                               | 2.0 |     | με   |

| tsst               | Start Setup Time                                              | 2.0 |     | μs   |

| <sup>†</sup> HDA   | Data In Hold Time                                             | 0   |     | με   |

| <sup>†</sup> SDA   | Data In Setup Time                                            | 200 |     | ns   |

| tr                 | Input Rise Time                                               |     | 0.3 | μs   |

| tf                 | Input Fall Time                                               |     | 300 | ns   |

| †SSTP              | Stop Setup Time                                               | 2.0 |     | μs   |

2

Table 2-32. AC CHARACTERISTICS (VCC = 3.3V ±10%)

| Symbol          | Parameter          | Min | Max | Unit |

|-----------------|--------------------|-----|-----|------|

| <sup>†</sup> DH | Data Out Hold Time | 100 |     | ns   |

| twa             | Write Cycle Time   |     | 20  | ms   |

#### Cascading Serial Configuration EEPROMs

For multiple FPGAs configured as a daisy-chain, or for future FPGAs requiring larger configuration memories, cascading MPA17C256s provides additional memory.

After the last bit from the first MPA17C256 is read, the next clock signal asserts its  $\overline{CEO}$  output LOW and disables its DATA line. The second MPA17C256 recognizes the LOW level on its  $\overline{CE}$  input and enables its DATA output.

#### Standby Mode

The MPA17C256 enters a low power standby mode whenever  $\overline{\text{CE}}$  is asserted HIGH. In this mode, it consumes

less than 1.0mA of current. The output remains in a high impedance state regardless of the state of the  $\overline{OE}$  input.

#### MPA17C256 Reset Polarity

The MPA17C256 lets the user choose the reset polarity as either RESET/OE or RESET/OE.

#### **Programming Mode**

The programming mode is entered by bringing SER\_EN LOW. In this mode, the chip can be programmed by a 2-wire interface. The programming is done at V<sub>CC</sub> supply only. Programming (high) voltages are generated inside the chip. For additional programming information, see the Programmer's Guide section on page 2-71.

# **Programmer's Guide**

#### Serial Bus Overview

The serial bus is a two wire bus; one wire (CLOCK) functions as a clock and is provided by the programmer, the second wire (DATA) is a bi-directional signal and is used to provide data and control information.

Information is transmitted on the serial bus in messages. Each MESSAGE is preceded by a START BIT and is ended with a STOP BIT. The message consists of an integer number of bytes, each byte consists of 8 bits of data and is followed by a ninth ACKNOWLEDGE BIT. This ACKNOWLEDGE BIT is provided by the recipient of the data, This is possible because devices only drive DATA low, the system (in the programming case the Programmer) provides a small pull—up current (1k Ohm equivalent) for the Data Pin.

The MESSAGE FORMAT consists of the bytes shown in the Message Bytes table below. The MESSAGE FORMAT is preceded by a start bit and ended by a stop bit.

The programmer provides all the bytes except for the data bytes when the device is being read. Note that each byte is individually acknowledged. This acknowledgment is provided by the MPA17C256 in all cases except for the data bytes in the read mode, in which case the acknowledge is provided by the programmer.

#### **Bit Format**

Data on the DATA pin may change only during CLOCK low times.

#### Figure 2-65. Message Bytes

| DEVICE  | 1ST ADDRESS | 2ND ADDRESS | DATA BYTE(S) |

|---------|-------------|-------------|--------------|

| ADDRESS | WORD        | WORD        |              |

|         |             |             |              |

#### Figure 2-66. Message Format

| START<br>BIT | DEVICE<br>ADDRESS | 1ST<br>ADDRESS<br>WORD | 2ND<br>ADDRESS<br>WORD | DATA<br>BYTE(S) | STOP<br>BIT |

|--------------|-------------------|------------------------|------------------------|-----------------|-------------|

|--------------|-------------------|------------------------|------------------------|-----------------|-------------|

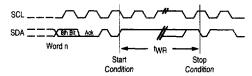

#### Start and Stop Bits

The START BIT is indicated by a high--to-low transition of DATA when CLOCK is high. Similarly, the STOP BIT is generated by a low--to--high transition of DATA when CLOCK is high, as shown below.

Figure 2-67. Start and Stop Bits

#### Acknowledge Bit

The ACKNOWLEDGE BIT is shown in the above figure. Note that the ACKNOWLEDGE BIT is provided by the device receiving the byte. The receiving device can accept the byte, by asserting a low value, on DATA or it can refuse the byte by asserting (not driving the signal) a 1 on DATA. All bytes must be terminated by either the ACKNOWLEDGE BIT or a STOP BIT

The most significant bit is the first bit of a byte transmitted on DATA for the DEVICE ADDRESS BYTE and the EEPROM ADDRESS BYTES. It is followed by the lesser significant bits until the eighth bit, the least significant bit is transmitted. This is followed by the acknowledge bit. However, for DATA BYTES (both writing and reading) the first bit transmitted is the least significant bit. This protocol is shown in the tables below.

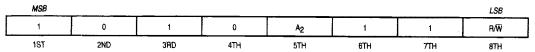

#### **Device Address Byte**

The contents of the Device Address Byte are shown below, along with the order in which the bits are clocked into the device. The A2 bit is provided to allow 2 devices to share a common bus; when programming a single device, the A2 bit must be forced to a logic '0' or '1' level. It is recommended that this pin be connected to 0V using a 4.7K ohm resistor pulldown

2

#### **EEPROM Address**

The EEPROM address consists of two bytes, each of which is followed by an acknowledge bit. These two bytes define a

15-bit address AE14 - AE0. The order in which each byte is clocked into the device is also indicated. AE14 is MSB for 17C256.

# 2

#### Figure 2-69.

| _ | MSB |                    |        |                  |                  |      |                 | LSB | _   | MSB |     |                 |                 |                 |                 |                 | LSB             |     |

|---|-----|--------------------|--------|------------------|------------------|------|-----------------|-----|-----|-----|-----|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----|

|   | 0   | 0/A <sub>E14</sub> | 0/AE13 | A <sub>E12</sub> | A <sub>E11</sub> | AE10 | A <sub>E9</sub> | AE8 | Ack | AE7 | AE6 | A <sub>E5</sub> | A <sub>E4</sub> | A <sub>E3</sub> | A <sub>E2</sub> | A <sub>E1</sub> | A <sub>E0</sub> | Ack |

|   | 1ST | 2ND                | 3RD    | 4TH              | 5TH              | 6TH  | 7TH             | 8ТН | -   | tST | 2N0 | 3FID            | 4TH             | 5TH             | 6TH             | 7TH             | втн             |     |

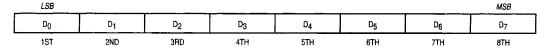

#### **Data Byte**

The organization of the Data Byte is shown below. Note that in this case, the data byte is clocked into the device LSB first and MSB last.

#### Writing

All writing takes place in pages. A page is 64-bytes long and the page boundaries are addresses where A5-A0 are all

zero. Writing can start at any address within a page and the number of bytes written must be 64. The first byte is written at the transmitted address. The address is incremented in the device following the receipt of each data word received, Only the lower six bits of the address are incremented and if the address is incremented after the 64th byte in the page is sent, then the next byte to be written is the first byte of the page.

Figure 2-70.

A write action consists of

a Start Bit

a Device Address with R/W = 0

An Acknowledge Bit From the device

First Word of the Address

An Acknowledge Bit From the device

Second Word of the Address

An Acknowledge Bit From the device

One or more data bytes (sent to the device)

Each followed by an Acknowledge Bit From the device

a Stop Bit

WRITE POLLING: On receipt of the stop bit, the device enters an internally timed write cycle. While the device is busy with this write cycle it will not acknowledge any transfers. Thus the programmer can start the next page write by sending the Start Bit followed by the Device Address. If this is not acknowledged, then the programmer should abandon the transfer without asserting a stop bit. The programmer can then repeat this until an acknowledge is received. When this is received the write action can proceed, i.e., the next byte to be sent is the device address.

#### Reading

Read operations are initiated the same way as write operations with the exception that the  $R\overline{W}$  bit in the device address is set to one. There are three read operations: current address read, random read and sequential read.

CURRENT ADDRESS READ: The internal data word address counter maintains the last address accessed during the last read or write operation. incremented by one. This address stays valid between operations as long as the chip

power is maintained and the device remains in 2-wire access mode. If the last operation was a read at address n, then the current address would be n+1. If the final operation was a write at address n, then the current address would again be n+1 with one exception. If address n was the 64th byte address in the page, the incremented address n+1 would "roll over" to the first byte address on the next page.

Once the device address with the RNW select bit set is clocked in and acknowledged by the device the current address word is serially clocked out. The programmer does not acknowledge the read but does generate a following stop condition.

```

A current address read action consists of a Start Bit a Device Address with R/\widetilde{W}=1 An Acknowledge Bit From the device a data byte from the device a Stop Bit from the programmer

```

**RANDOM READ:** A random read requires a "dummy" byte write sequence to load in the data word address. Once the device address word and data word address are clocked in and acknowledged by the device, the programmer must generate another start condition. The programmer now initiates a current address read by sending a device address with the  $R/\overline{W}$  bit high. The device acknowledges the device address and serially clocks out the data word. The programmer does not acknowledge the read but does generate a following stop condition.

```

A random address read action consists of a Start Bit a Device Address with R/\widetilde{W}=0 An Acknowledge Bit From the device First Word of the Address An Acknowledge Bit From the device Second Word of the Address An Acknowledge Bit From the device a Start Bit a Device Address with R/\widetilde{W}=1 An Acknowledge Bit From the device a data byte from the device a stop bit from the programmer

```

SEQUENTIAL READ: Sequential reads are initiated by either a current address read or a random address read. After the programmer receives a data word, it responds with an acknowledge. As long as the device receives an acknowledge, it will continue to increment the data word address and serially clock out sequential data words. When the memory address limit is reached, the data word address will "roll over". The sequential read operation is terminated when the programmer does not respond with an acknowledge but generates a stop condition.

#### **Programming Pins**

Eight pins are used to program the devices. These eight pins, and their mapping to the package pins are shown in the following table:

Table 2-33. Programming Pins

| Pin      | 8-Pin Device | 20-Pin Device |  |  |  |  |

|----------|--------------|---------------|--|--|--|--|

| DATA     | 1            | 2             |  |  |  |  |

| CLOCK    | 2            | 4             |  |  |  |  |

| RESET/OF | 3            | 6             |  |  |  |  |

| CE       | 4            | 8             |  |  |  |  |

| GROUND   | 5            | 10            |  |  |  |  |

| A2 (CEO) | 6            | 14            |  |  |  |  |

| SER_EN   | 7            | 17            |  |  |  |  |

| Vcc      | 8            | 20            |  |  |  |  |

#### **Programmer Functions**

The programmer needs to perform the following functions:

- Check the Manufacturers Code and the Device Code (Not necessary for In-System Programming)

- 2. Program the device

- 3. Verify the device

- 4. Set the Reset Polarity option

In the order given above. They are performed in the following

#### Reading Manufacturers and Device Code

These two bytes are read from addresses 0 and 1, respectively, by performing a "read" as specified in this spec, with the following DC voltages set:

```

RESET/CE = 0V

CE = 11.5 ± 0.5V

A2 (CEO) = (Same as applied to A2 Pin,

usually 0V)

SER_EN = 0V

```

The correct codes are (Note 1.)

```

Manufacturers Code - Byte 0 1E

Device Code - Byte 1 FF 17C128

7F 17C65

77 17C256

```

The Manufacturer's Code and Device Code are read using the same byte ordering specified in the beginning of this document: i.e., LSB first, MSB last.

#### **Programming the Device**

All the bytes in the device's 64-byte page must be written, The order is not important but it is suggested that the device be written sequentially from Byte 0. Writing is accomplished by using the DATA and CLOCK pins and setting the other programming pins as follows:

2

```

RESET/CE = 0V

CE = 0V

A2 (CEO) = (Same as applied to A2 Pin, usually 0V)

SER_EN = 0V

```

#### Verifying the Device

All bytes in the device must be read and compared to their intended values. Reading is done using the CLOCK and DATA pins with the other programming pins set to the same value as in programming:

```

RESET/CE = 0V

CE = 0V

A2 (CEO) = (Same as applied to A2 Pin,

usually 0V)

SER_EN = 0V

```

#### MPA17C256 Setting the Polarity Option

#### Setting the Polarity Option Active High

Write a byte of data set to FF to address 3FFF, using the previously defined 2-wire write algorithm, with the other programming pins set to the following:

```

\begin{array}{lll} {\rm RESET/CB} & = & {\rm VCC} \pm 0.25 {\rm V} \\ {\rm CE} & = & {\rm VCC} \pm 0.25 {\rm V} \\ {\rm A2~(CEO)} & = & {\rm (Same~as~applied~to~A2~Pin,} \\ {\rm Usually~0V)} \\ {\rm SER.EN} & = & {\rm OV} \\ \end{array}

```

This will change RESET/OE pin functionality to RESET/OE, i.e., active high OE and active low RESET.

#### Setting the Polarity Option Active Low:

Write a byte of data set to FE to address 3FFF, using the previously defined 2-wire write algorithm, with the other programming pins set to the following:

This will change RESET/OE functionality to RESET/OE i.e., active low OE and active high RESET (the default condition).

After RESET polarity has been modified the MPA17C256 device must be powered down before the modified RESET polarity takes effect.

#### Verifying the RESET/OE Polarity

If a programmed (master) device is to be used as the source for the data to be programmed into some new devices, then the programmer can read the data from the master The polarity of the RESET/OE must be known before this can be done successfully for the MPA17C256. Depending on the capabilities of the programming device, one of the following algorithms can be used to read the programmed polarity of the RESET/OE pin.

#### It the programmer is able to sense a tn-state condition:

Switch the power on with

```

RESET/CE

=

0V

CE

=

0V

A2 (CEO)

=

Input to programmer (High Z)

SER_EN

=

VCC ± 0.25V

CLOCK

=

0

INPUT

=

Input to programmer

```

In this condition, if the SDA pin is 3-stated then he RESET/OE fuse is active high: it the SDA pin reads a "O" or a "1", then the RESET/OE fuse is active low.

# 2. If the programmer is NOT able to sense a 3-state condition:

Switch the power on with

```

RESET/CE

=

VCC ± 0.25V

CE

=

0V

A2 (CEO)

=

Input to programmer (High Z)

SER_EN

=

VCC ± 0.25V

CLOCK

=

0

INPUT

=

Input to programmer

```

Hold this configuration for twn time after VCC reaches nominal level. Then, set RESET/ÖE to low and pulse the clock 262,144 times for the MPA17C256, reading the data provided at each clock pulse. After the last clock has been issued  $\overline{\text{CEO}}$  should drop from high to low. If it does so then the polarity is RESET/ÖE (active low). If  $\overline{\text{CEO}}$  remains high, then the polarity is  $\overline{\text{RESET/OE}}$  (active high). In this latter case, none of the data read is reliable and it should be discarded. The procedure should be redone with RESET/ $\overline{\text{OE}}$  = 0V on power up and switched to VCC  $\pm$  0.25V before starting the clock. The data read is now good data.