# agere

# LCK4953/L-LCK4953 Low-Voltage PLL Clock Driver

## Features

- Fully integrated PLL.

- Output frequency up to 130 MHz in PLL mode.

- Nine outputs with high-impedance disable.

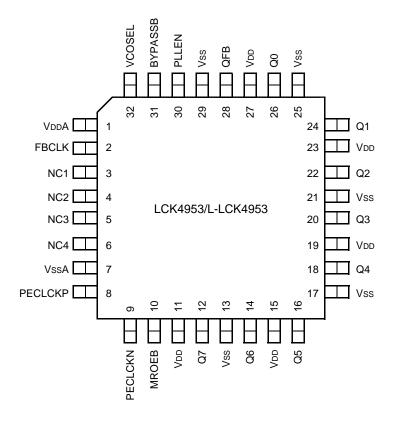

- 32-lead TQFP.

- 50 ps cycle-to-cycle jitter.

- Pin compatible with the *Motorola*<sup>®</sup> MPC953 clock driver.

# Description

The LCK4953 is a PLL-based clock driver device intended for high-performance clock tree designs. The LCK4953 is 3.3 V compatible with output frequencies of up to 130 MHz and output skews of 75 ps. The LCK4953 can meet the most demanding timing requirements and employs on-chip voltage regulators to minimize cycle-to-cycle jitter and phase jitter.

The LCK4953 is ideal for use as a zero delay, low skew, fan-out buffer due to its differential LVPECL reference input along with an external feedback input. The MROEB pin of the LCK4953, when driven high, will reset the internal counters and 3-state the output buffers. The LCK4953 has been optimized for zero delay performance. The LCK4953 is fully 3.3 V compatible and requires no external loop filter components. All control inputs accept LVCMOS or LVTTL compatible levels while the outputs provide LVCMOS levels with the ability to drive terminated 50  $\Omega$  transmission lines. For series-terminated 50  $\Omega$  lines, each of the LCK4953 outputs can drive two traces giving the device an effective fan-out of 1:18. For the optimum combination of board density and performance, the device is packaged in a 7 mm  $\times$  7 mm 32-lead TQFP package. The L-LCK4953 is a lead-free device.

#### Table 1. Function Table

| BYPASSB | Function         |

|---------|------------------|

| 1       | PLL Enabled      |

| 0       | PLL Bypass       |

| MROEB   | Function         |

| 1       | Outputs Disabled |

| 0       | Outputs Enabled  |

| VCOSEL  | Function         |

| 1       | ÷ 8              |

| 0       | ÷ 4              |

| PLLEN   | Function         |

| 1       | Select VCO       |

| 0       | Select PELCLK    |

## Description (continued)

5-8653(F)

Figure 1. 32-Lead Pinout (Top View)

## **Absolute Maximum Ratings**

Stresses which exceed the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to absolute maximum ratings for extended periods of time can adversely affect device reliability.

#### Table 2. Absolute Maximum Ratings

| Parameter                 | Symbol | Min  | Мах       | Unit |

|---------------------------|--------|------|-----------|------|

| Supply Voltage            | Vdd    | -0.3 | 4.2       | V    |

| Input Voltage             | Vin    | -0.3 | Vdd + 0.3 | V    |

| Input Current             | lin    | —    | ±20       | mA   |

| Storage Temperature Range | Tstg   | -40  | 125       | ٥C   |

Notes:

Lead free: No intentional addition of lead, and less than 1000 ppm.

Agere Systems lead-free devices are fully compliant with the Restriction of Hazardous Substances (RoHS) directive that restricts the content of six hazardous substances in electronic equipment in the European Union. Beginning July 1, 2006, electronic equipment sold in the European Union must be manufactured in accordance with the standards set by the RoHS directive.

External leads can be bonded and soldered safely at temperatures of up to 300 °C on non-lead-free parts and up to 350 °C on lead-free parts.

## Absolute Maximum Ratings (continued)

| Parameter                                   | Symbol | Min       | Тур | Max       | Unit | Condition                                |

|---------------------------------------------|--------|-----------|-----|-----------|------|------------------------------------------|

| Input High-voltage LVCMOS<br>Inputs         | Vін    | 2.0       | —   | 3.6       | V    | _                                        |

| Input Low-voltage LVCMOS<br>Inputs          | VIL    | —         | —   | 0.8       | V    | —                                        |

| Peak-to-peak Input Voltage<br>PECL_CLK      | Vр-р   | 300       | —   | 1000      | mV   | —                                        |

| Common-mode Range<br>PECL_CLK               | VCMR   | Vdd - 1.5 | —   | Vdd - 0.6 | mV   | *                                        |

| Output High Voltage                         | Vон    | 2.4       | _   | —         | V    | $IOH = -30 \text{ mA}^{\dagger}$         |

| Output Low Voltage                          | Vol    | —         |     | 0.6       | V    | $IOL = 30 \text{ mA}^{\dagger}$          |

| Input Current                               | lin    | —         | _   | ±120      | μA   | —                                        |

| Input Capacitance                           | CIN    | —         | _   | 4         | pF   | —                                        |

| Power Dissipation Capacitance               | Cpd    | —         | 12  | —         | pF   | Per output                               |

| Maximum Quiescent Supply<br>Current Non-PLL | IDDQ   | —         | _   | 1         | mA   | All VDD pins except<br>VDDA <sup>‡</sup> |

| Maximum PLL Supply Current                  | IDDPLL | —         | _   | 45        | mA   | VDDA pin only                            |

#### Table 3. dc Characteristics (TA = 0 °C to 70 °C, VDD = 3.3 V $\pm$ 5%)

\* VCMR is the difference from the most positive side of the differential input signal. Normal operation is obtained when the high input is within the VCMR range and the input swing lies within the Vp-p specification.

† The LCK4953 outputs can drive series- or parallel-terminated 50 Ω (or 50 Ω to Vcc/2) transmission lines on the incident edge.

<sup>‡</sup> Total power = (IDDPLL + IDDQ + fCV) \* V; where f = fref, V = VDDD, C = total load capacitance on all outputs.

#### **Table 4. PLL Input Reference Characteristics** (TA = 0 °C to 70 °C)

| Parameter                  | Symbol | Min | Max | Unit | Condition |

|----------------------------|--------|-----|-----|------|-----------|

| Reference Input Frequency  | fref   | 25  | 130 | MHz  | —         |

| Reference Input Duty Cycle | trefdc | 25  | 75  | %    | —         |

#### Table 5. ac Characteristics (TA = 0 °C to 70 °C, VDD = 3.3 V $\pm$ 5%)

| Parameter                                         | Symbol      | Min           | Тур | Max              | Unit              | Condition                     |

|---------------------------------------------------|-------------|---------------|-----|------------------|-------------------|-------------------------------|

| Output Rise/Fall Time                             | tr, tf      | 0.10          | _   | 1.0              | ns                | 0.8 V to 2.0 V                |

| Output Duty Cycle                                 | tpw         | 47            | 50  | 53               | %                 | —                             |

| Output-to-output Skews                            | tsk(O)      | _             | _   | 75               | ps                | —                             |

| PLL VCO Lock Range                                | fVco        | 200           |     | 520              | MHz               | —                             |

| Frequency Output:<br>Frequency PLL<br>Bypass Mode | fout        | 25<br>50<br>— |     | 65<br>130<br>250 | MHz<br>MHz<br>MHz | VCOSEL = 1<br>VCOSEL = 0<br>— |

| Input to Ext_FB Delay (with PLL locked)           | tpd (lock)  | -75           |     | 125              | ps                | tref = 75 MHz                 |

| Input to Q Delay                                  | tpd(bypass) | 3             | _   | 7                | ns                | PLL bypassed                  |

| Part to Part Delay                                | Ī           |               |     | 1.5              |                   |                               |

| Output Disable Time                               | tPLZHZ      | _             |     | 7                | ns                | —                             |

| Output Enable Time                                | tPZL        |               |     | 6                | ns                | —                             |

| Cycle-to-cycle Jitter (peak-to-peak)              | tjitter     | _             |     | 50               | ps                | fout > 75 MHz                 |

# **Electrical Characteristics**

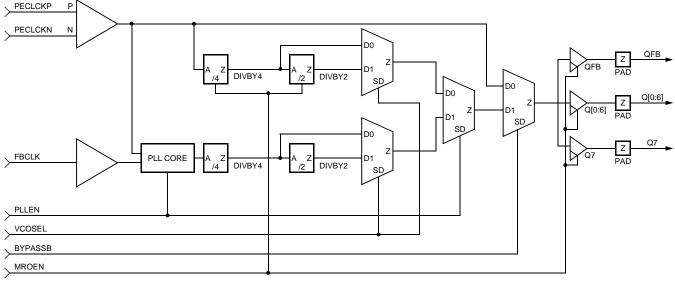

#### Figure 2. Logic Diagram

5-8654.a (F)

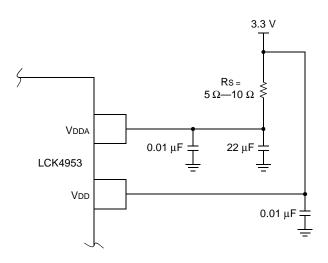

## **Power Supply Filtering**

The LCK4953 is a mixed-signal product that is susceptible to random noise, especially when this noise is on the power supply pins. To isolate the output buffer switching from the internal phase-locked loop, the LCK4953 provides separate power supplies for the phase-locked loop (VDDA) and for the output buffers (VDD). In a digital system environment, besides this isolation technique, it is highly recommended that both VDDA and VDD power supplies be filtered to reduce the random noise as much as possible.

Figure 3 illustrates a typical power supply filter scheme. A filter for the LCK4953 should be designed to target noise in the 100 kHz to 10 MHz range, due to the LCK4953's susceptibility to noise with spectral content in this range. The RC filter in Figure 3 will provide a broadband filter with approximately –40 dB attenuation for noise with spectral content above 20 kHz. More elaborate power supply schemes may be used to achieve increased power supply noise filtering.

Figure 3. Power Supply Filter

5-9575(F)

## Electrical Characteristics (continued)

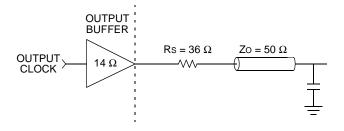

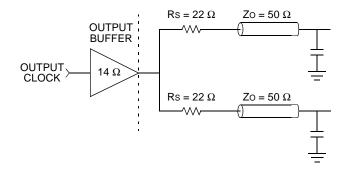

## **Driving Transmission Lines**

The LCK4953 clock driver was designed to drive high-speed clock terminals in a terminated transmission line environment. Point-to-point distribution of signals is a common method in most high-performance clock networks. Either series-terminated or parallel-terminated transmission lines can be used in a point-to-point scheme. The parallel technique terminates the signal at the end of a line with a 50  $\Omega$  resistance to VDD/2. This draws a fairly high level of dc current. Due to this aspect, only a single terminated line can be driven by each output of the LCK4953 clock driver. However, for the series-terminated case, there is no dc current draw. Therefore, the outputs are capable of driving multiple series-terminated lines.

Figure 4 illustrates an output driving a single series-terminated line.

5-9576(F)

Figure 4. Single Transmission Line

In Figure 4, because the output buffer has an impedance of 14  $\Omega$ , the series resistance (Rs) is set at 36  $\Omega$ . This ensures that the total impedance is matched with the 50  $\Omega$  transmission line.

Figure 5 illustrates an output driving two series-terminated lines.

5-9577(F)

Figure 5. Dual Transmission Lines

In Figure 5, the two series resistors (Rs) are set at 22  $\Omega$  because the 14  $\Omega$  output buffer can be viewed as two 28  $\Omega$  resistors in parallel. Accordingly, for each transmission line, the impedance is well matched.

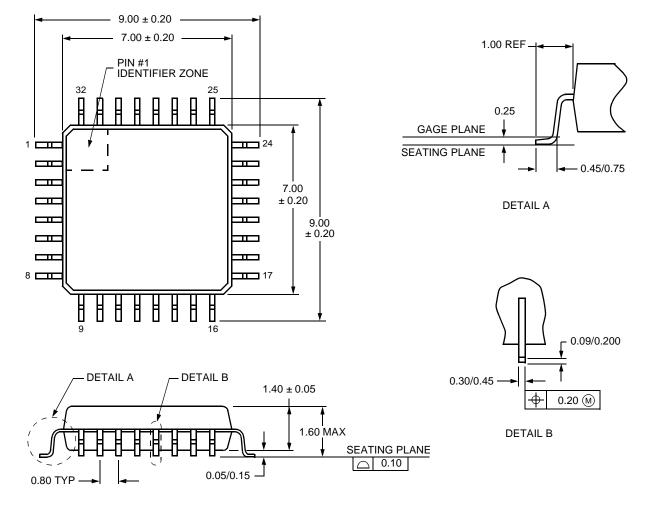

# **Outline Diagram**

## 32-Pin TQFP

Dimensions are in millimeters.

12-3076(F)

Motorola is a registerd trademark of Motorola, Inc.

|             | information, contact your Agere Systems Account Manager or the following:                                                      |

|-------------|--------------------------------------------------------------------------------------------------------------------------------|

| INTERNET:   | Home: http://www.agere.com Sales: http://www.agere.com/sales                                                                   |

| E-MAIL:     | docmaster@agere.com                                                                                                            |

| N. AMERICA: | Agere Systems Inc., Lehigh Valley Central Campus, Room 10A-301C, 1110 American Parkway NE, Allentown, PA 18109-9138            |

|             | 1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106)                                                 |

| ASIA:       | CHINA: (86) 21-54614688 (Shanghai), (86) 755-25881122 (Shenzhen)                                                               |

|             | JAPAN: (81) 3-5421-1600 (Tokyo), KOREA: (82) 2-767-1850 (Seoul), SINGAPORE: (65) 6741-9855, TAIWAN: (886) 2-2725-5858 (Taipei) |

| EUROPE:     | Tel. (44) 1344 296 400                                                                                                         |

Agere Systems Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. Agere is a registered trademark of Agere Systems Inc. Agere Systems and the Agere logo are trademarks of Agere Systems Inc.

Copyright © 2005 Agere Systems Inc. All Rights Reserved