# Am2130/Am2140

1024x8 Dual-Port Static Random-Access Memories

#### DISTINCTIVE CHARACTERISTICS

- True dual port operation

- · Access time as fast as 55 ns

- Master device (Am2130) has on-chip arbitration

- Expandable data bus width in multiples of 8 bits using one master (Am2130) and required number of slave devices (Am2140)

- · Automatic power-down feature

- · All inputs and outputs are TTL-compatible

- 48-pin DIP or 52-pin PLCC

- Single +5-volt power supply

- Advanced N-MOS technology

#### GENERAL DESCRIPTION

The Am2130 and the Am2140 are members of the 1K x 8 dual-port static RAM family. The Am2130 is designated as the master and the Am2140 as the slave device. The master provides the necessary control signal to the slave devices to facilitate implementing a wider data bus in a system. The master/slave concept allows expansion with minimal external logic.

Both devices have two independent ports called Left and Right port. Each port consists of an 8-bit bidirectional data bus and a 10-bit address input bus and necessary control signals.

The Am2130 has an on-board arbiter to resolve contention between the left and right ports. When contention between ports occurs, one port is given priority while the other port receives a busy indication.

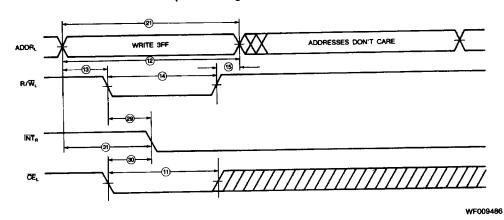

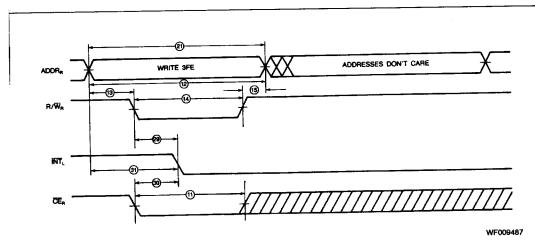

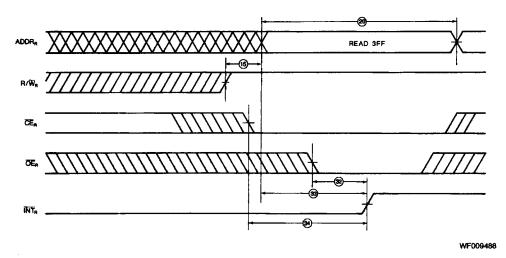

The Am2130 also contains on-chip facilities for supporting semaphores. Addresses (3FE) $_{\rm H}$  and (3FF) $_{\rm H}$  serve as

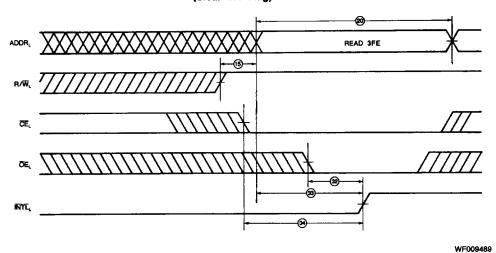

interrupt generators. If any data is written at the address (3FF)<sub>H</sub> from the left port, an interrupt signal becomes active for the right port. The interrupt signal is deactivated by reading from the right port at the same address. The address (3FE)<sub>H</sub> is used in a similar fashion by the right port to activate the interrupt signal for the left port.

The Am2130/Am2140 also have two chip enable signals corresponding to the left and right ports. Before any transaction on a port takes place, the corresponding chip enable input must be activated. If a chip enable signal is not active, the circuitry corresponding to its side automatically powers down and enters standby mode.

The Am2130/Am2140 are packaged in 48-pin DIPs or 52-pin plastic leaded chip carrier. All inputs and outputs are TTL-compatible and the devices operate from a single +5-volt power supply.

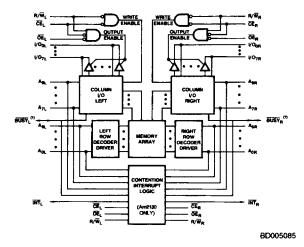

#### **BLOCK DIAGRAM**

Notes: 1. Am2130 (Master): BUSY is open-drain output and requires pull-up resistor.

Am2140 (Slave): BUSY is an input.

Publication # Rev. Amendment 05157 F /0 Issue Date: January 1989

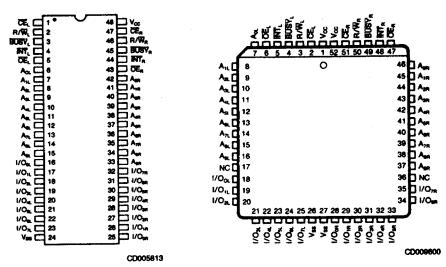

# CONNECTION DIAGRAMS Top View

PLCC

DIP

Note: Pin 1 is marked for orientation.

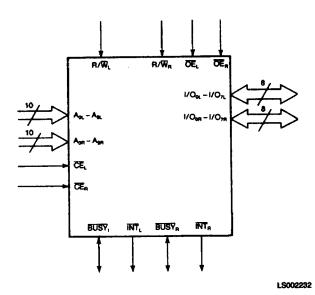

#### LOGIC SYMBOL

V<sub>CC</sub> = +5-V Power Supply V<sub>SS</sub> = Ground

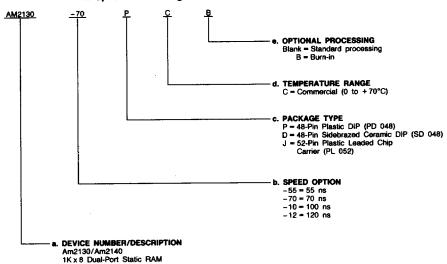

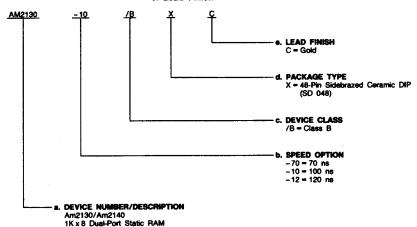

#### ORDERING INFORMATION

#### Standard Products

AMD products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range

- e. Optional Processing

| Vaild     | Combinations |

|-----------|--------------|

| AM2130-55 |              |

| AM2130-70 | $\neg$       |

| AM2130-10 |              |

| AM2130-12 | PC, PCB, DC, |

| AM2140-55 | DCB, JC, JCB |

| AM2140-70 |              |

| AM2140-10 |              |

| AM2140-12 |              |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

#### **MILITARY ORDERING INFORMATION**

#### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for APL products is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Device Class

- d. Package Type

- e. Lead Finish

| Valid Combinations |      |  |  |

|--------------------|------|--|--|

| AM2130-70          |      |  |  |

| AM2130-10          |      |  |  |

| AM2130-12          | /BXC |  |  |

| AM2140-70          | /BAC |  |  |

| AM2140-10          |      |  |  |

| AM2140-12          |      |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

#### **Group A Tests**

Group A Tests consist of subgroups 1, 2, 3, 7, 8, 9, 10, 11.

#### PIN DESCRIPTION

#### Am2130

#### A<sub>OL</sub> - A<sub>9L</sub> Left Port Address (inputs)

These 10 inputs constitute the memory address for the left port.  $A_0$  is the least significant bit position and  $A_0$  is the most significant position. A HIGH level on any of these inputs represents a logic 1 at that position and LOW represents a logic 0. The sequence of events and related timing for the address inputs during read and write operations will be discussed in later sections of this data sheet

If a write operation is performed using (3FF)H, an interrupt signal is activated for the right port (see  $\overline{\text{INT}}_R$  pin description).

If a read operation is performed using (3FE)<sub>H</sub>, the  $\overline{\text{INT}}_{\text{L}}$  signal will be deactivated (see  $\overline{\text{INT}}_{\text{L}}$  description).

#### Ang - Agg Right Port Address (Inputs)

These 10 inputs constitute the memory address for the right port.  $A_0$  is the least significant bit position and  $A_0$  is the most significant position. A HIGH level on any of these inputs represents a logic 1 at that position and LOW represents a logic 0. The sequence of events and related timing for the address inputs during read and write operations will be discussed in later sections of this data sheet

If a write operation is performed using (3FE) $_{H}$ , an interrupt signal is activated for the left port (see  $\overline{INT}_{L}$  pin description).

If a read operation is performed using (3FF)H, the  $\overline{\text{INT}}_{R}$  signal will be deactivated (see  $\overline{\text{INT}}_{R}$  description).

#### BUSY: Left Port Busy Flag (Output; Open Drain)

This open-drain output requires a pull-up resistor for proper operation. A LOW on this output indicates that the on-chip arbitration logic detected a contention between the left and right ports and the right port is given priority. All left port signals must be held stable until a HIGH on this output is indicated.

The  $\overline{BUSY}_L$  signal generation is a logical function of the left and right port address inputs and the  $\overline{CE}_L$  and  $\overline{CE}_R$  inputs. The transient behavior of the  $\overline{BUSY}_L$  output is not assured while the inputs are changing.

#### BUSY<sub>R</sub> Right Port Busy Flag (Output; Open Drain)

This open-drain output requires a pull-up resistor for proper operation. A LOW on this output indicates that the on-chip arbitration logic detected a contention between the left and right ports and the left port is given priority. All right port signals must be held stable until a HIGH on this output is indicated.

The BUSY<sub>R</sub> signal generation is a logical function of the left and right port address inputs and the CE<sub>L</sub> and CE<sub>R</sub> inputs. The transient behavior of the BUSY<sub>R</sub> output is not assured while the inputs are changing.

#### CE<sub>I</sub> Left Port Chip Enable (Input)

This input must be LOW before any transaction from the left port and remain LOW for the duration of the transaction. When this input goes HIGH, left port logic circuits enter standby power mode and remain in this mode as long as this input remains HIGH. It should be noted that powering down the left port to standby mode does not affect the  $\overline{\text{INT}}_{L}$  or  $\overline{\text{INT}}_{R}$  outputs. This input going HIGH also initializes the internal arbitration latch. It is recommended that  $\overline{\text{CE}}_{L}$  go HIGH after completing a transaction (see discussion on arbitration).

#### CEn Right Port Chip Enable (Input)

Operation of this input is identical to CEL except that the CEB input controls the right port.

#### GND (VSS) Ground

# I/O<sub>0L</sub> - I/O<sub>7L</sub> Left Port Input/Output Bus (Input/Output; Three State)

These eight lines constitute the data bus for the left port. If a read operation is performed using the left port, data from the location addressed by the left port address will be available on these lines. Similarly, to perform a write operation using the left port, data to be written into the memory must be presented on these lines. The drivers on the chip to drive these lines are enabled only when the  $\overline{\text{CE}}_{\text{L}}$  is LOW,  $\overline{\text{OE}}_{\text{L}}$  is LOW and  $\overline{\text{R/W}}_{\text{l}}$  is HIGH.

# I/O<sub>0R</sub> - I/O<sub>7R</sub> Right Port Input/Output Bus (Input/Output; Three State)

These eight lines constitute the data bus for the right port. If a read operation is performed using the right port, data from the location addressed by the right port address will be available on these lines. Similarly, to perform a write operation using the right port, data to be written into the memory must be presented on these lines. The drivers on the chip to drive these lines are enabled only when the  $\overline{\text{CE}}_R$  is LOW,  $\overline{\text{OE}}_R$  is LOW and  $R/\overline{W}_R$  is HIGH.

#### INT: Left Port Interrupt Flag (Output; Open Drain)

This open-drain output requires a pull-up resistor for proper operation. If the right port performs any write operation using address (3FE)H, then this output goes LOW. It will remain LOW until the left port successfully completes any read operation using the address (3FE)H. It should be noted that powering down the ports has no effect on this output.

### INT<sub>R</sub> Right Port Interrupt Flag (Output; Open Drain)

This open-drain output requires a pull-up resistor for proper operation. If the left port performs any write operation using address (3FF)H, then this output goes LOW. It will remain LOW until the right port successfully completes any read operation using the address (3FF)H. It should be noted that powering down the ports has no effect on this output.

### OEL Output Enable Left I/O Port (Input)

When this input is HIGH, the left port I/O bus lines are in high impedance state. If this input is LOW and  $\overline{CE}_{L}$  is LOW and  $R/\overline{W}_{L}$  is HIGH, the left port drivers are enabled and data from the location addressed by the  $A_{OL}$  –  $A_{9L}$  input will be available on the I/O bus lines of the left port. It may be of interest to note that the  $\overline{OE}_{L}$  input has no effect on the  $\overline{BUSY}_{L}$  or  $\overline{BUSY}_{R}$  or  $\overline{INT}_{L}$  or  $\overline{INT}_{R}$  signals. Even though the left port I/O port drivers are disabled when the  $R/\overline{W}_{L}$  input goes LOW (write operation), it is recommended that the  $\overline{OE}_{L}$  signal be kept HIGH during write operations to the left port.

#### OER Output Enable Right I/O Port (Input)

When this input is HIGH, the right port I/O bus lines are in high impedance state. If this input is LOW and  $\overline{CE}_R$  is LOW and R/ $\overline{W}_R$  is HIGH, the right port drivers are enabled and data from the location addressed by the AoR – AgR inputs will be available on the I/O bus lines of the right port. It may be of interest to note that the  $\overline{OE}_R$  input has no effect on the  $\overline{BUSY}_R$  or  $\overline{INT}_L$  or  $\overline{INT}_R$  signals. Even though the left port I/O port drivers are disabled when the  $R/\overline{W}_R$  input goes LOW (write operation), it is recommended that the  $\overline{OE}_R$  signal be kept HIGH during write operations to the right port.

#### R/WL Left Port Read/Write Enable (Input)

This input is used to specify the left port function to be performed. HIGH indicates a read and LOW indicates a write function.

When the  $\overline{CE}_L$  is LOW and the  $\overline{OE}_L$  is LOW and the R/ $\overline{W}_L$  is HIGH, data from the location addressed by the  $A_{0L}-A_{9L}$  will be available on the  $I/O_{0L}-I/O_{7L}$  lines. As mentioned earlier, reading from the left port at the location (3FE)<sub>H</sub> disables the  $\overline{INT}_L$  output.

When the  $\overline{\text{CE}}_L$  is LOW and the R/ $\overline{\text{W}}_L$  goes LOW, data present on the I/O<sub>0L</sub> – I/O<sub>7L</sub> lines will be written into the location addressed by the A<sub>0L</sub> – A<sub>9L</sub> inputs. It should be noted that the write operation is not affected by the  $\overline{\text{OE}}_L$  input. However, it is recommended that the  $\overline{\text{OE}}_L$  input beheld HIGH during a write operation. As mentioned earlier, performing a write operation from the left port at the address (3FF)<sub>H</sub> causes the  $\overline{\text{INT}}_R$  output to go LOW.

It should be noted that even though  $R/\overline{W}_L$  is LOW, writing is internally inhibited if the right port is given priority by the arbiter. Discussion on arbitration can be found in a later section.

R/WR Right Port Read/Write Enable (Input)

This input is used to specify the right port function to be performed. HIGH indicates a read and LOW indicates a write function.

When the  $\overline{\text{CE}}_R$  is LOW and the  $\overline{\text{OE}}_R$  is LOW and the  $R/\overline{W}_R$  is HIGH, data from the location addressed by the  $A_{OR}-A_{PR}$  will be available on the  $I/O_{OR}-I/O_{7R}$  lines. As mentioned earlier, reading from the right port at the location (3FF)<sub>H</sub> disables the  $\overline{INT}_R$  output.

When the  $\overline{CE}_{H}$  is LOW and the R/ $\overline{W}_{H}$  goes LOW, data present on the I/O<sub>0R</sub> – I/O<sub>7R</sub> lines will be written into the location addressed by the A<sub>0R</sub> – A<sub>9R</sub> inputs. It should be noted that the write operation is not affected by the  $\overline{OE}_{R}$  input. However, it is recommended that the  $\overline{OE}_{R}$  input held HIGH during a write operation. As mentioned earlier, performing a write operation from the left port at the address (3FE)<sub>H</sub> causes the  $\overline{INT}_{L}$  output to go LOW.

It should be noted that even though  $R/\overline{W}_R$  is LOW, writing is internally inhibited if the left port is given priority by the arbiter. Discussion on arbitration can be found in a later section.

V<sub>CC</sub> +5-Volt Power Supply

#### Am2140

The Am2140 is functionally very similar to the Am2130. The Am2140 differs from the Am2130 in two signals only— BUSYL and BUSYR. In the case of the Am2140 they are used as inputs and play a significant role in expanding the word width.

#### BUSY, Left Port Busy Flag (Input)

If this input is LOW, a write enable signal to the left side of the memory array is internally disabled. In expanded systems where an Am2130 is used as the master, this input is connected to the BUSY L output of the Am2130.

BUSY<sub>R</sub> Right Port Busy Flag (Output; Open Drain)

If this input is LOW, a write enable signal to the right side of

the memory array is internally disabled. In expanded

systems where an Am2130 is used as the master, this input

is connected to the BUSY<sub>R</sub> output of the Am2130.

#### **FUNCTIONAL DESCRIPTION**

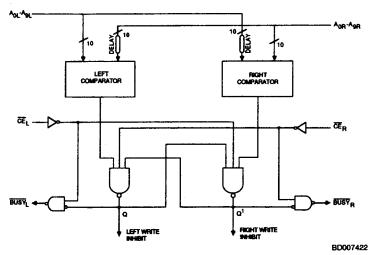

As shown in the block diagram, the Am2130/Am2140 is a true 1K x 8 dual-port RAM. It consists of a memory array with two sets of address decoders and associated logic. This arrangement allows the accessing of every word in the memory array from two independent sources. We call these sources left side and right side for convenience. Data accessed by the left-side address inputs appears on the left-side data lines of the array and is connected to the left-side I/O pins through the associated three-state buffers. The enable control signal for these buffers is generated using the R/WL, CEL and OEL inputs. If the I/O buffers are disabled on the chip, the I/O pins can be used as inputs. Data to be written from the left port is presented on these inputs. Writing into the memory array from the left side is controlled by the left write enable signal generated on the chip using the R/WL and CEL inputs. An identical arrangement exists for the right side also. In addition, there is on-chip arbitration logic to give priority to one port over the other in case of a contention, and interrupt flag logic.

#### **Contention Arbitration**

Two independent access facilities are provided in a dual-port memory to eliminate physical interference between signals. However, there are two significant possibilities of "logical" interference which are not tolerable: when one port is reading from a location while the other port is writing into the same location at the same time. In this case, data received by the reading port may not be predictable. Similarly, consider the situation when both ports write information into the same location simultaneously. The resultant data that finally ends up in the memory location may not be valid. These two situations are commonly called contention. The Am2130 has on-chip logic to detect contention and give priority to one port over the other. In a true dual-port RAM, simultaneous reading from both ports at the same address does not corrupt the data. Hence, it can be construed that no contention occurs. However, for the sake of simplicity and compatibility with the industry standard practices, the Am2130 arbitration is based purely on addresses. Hence, in the case of a simultaneous read from both ports at the same address, the arbitration logic will sense contention and give priority to one of the ports. The other port will receive a busy indication.

Figure 1 is a conceptual logic diagram of contention arbitration logic. It consists of two equality comparators. The left comparator compares the left port address inputs to the delayed version of the right port address. Similarly, the right comparator compares the right-port address to the delayed version of the left port address. The output of the comparators is connected to a latch formed by two cross-coupled NAND gates as shown in Figure 1. The chip enable signals, CEL and CER, are also inputs to this latch as shown. The BUSYL and BUSYR outputs are generated by gating the latch output with the proper chip enable signal as shown. Also note that the latch outputs are used internally for left and right write inhibit signals. For example, if the right side write inhibit signal in Figure 1 is LOW, writing into the memory does not occur even if the R/WR input of the Am2130 is LOW.

The operation of the arbitration circuit can now be explained. Assume that the left port address had been stable and CEL is LOW. Both Q and Q' outputs of the latch will be HIGH because the output of both comparators is LOW (addresses are different). So the BUSY output on both sides is HIGH. Now assume that the right address changes and becomes equal to the left address. The right address comparator output goes HIGH and the Q' output of the latch goes LOW. Eventually the output of the left comparator also goes HIGH, but because of the cross coupling of the Q' into the gate generating the Q output, Q output remains HIGH. As soon as the CER input goes LOW, BUSYR becomes LOW. Thus, the arbitrator gave priority to the left port by indicating a busy signal to the right port. Thus in this example, the left port is the winner and the right port is the loser in the contention for the memory. Sooner or later the left port will finish its transaction at the contended location and change the address or its chip enable will go HIGH. Thus when the contention is over the Q output of the latch will become HIGH and BUSYR will go HIGH. A similar reasoning can be used to understand the operation of the left side. It should be clear then, in cases of contention, the arbiter will decide one port as the winner and the losing port must wait for the winner to complete the use of the memory. The winning port must indicate to the arbiter that it has completed its operation either by changing the address or making its chip enable input HIGH. Without such an indication, the arbiter will not remove the busy indication to the losing port.

Figure 1. Conceptual Arbitration Logic

#### Read/Write Operations

Performing read/write operations when there is no contention is relatively straightforward. The sequence of events for a read is listed below. The timing relationships between various signals can be found in later sections of this data sheet.

- Establish HIGH on the R/W and LOW on the CE input of the desired port.

- 2. Establish the desired address on the desired port address lines

- 3. Make the OE input of the desired port LOW.

- The I/O lines of the selected port will contain the data after the access time has elapsed.

- Make the output enable and chip enable inputs HIGH to complete the read operation.

Performing write operations when there is no contention is equally straightforward. The sequence of events for a write is listed below. The timing relationships between various signals can be found in later sections of this data sheet.

- 1. Establish LOW on the CE input of the desired port.

- Establish the desired address on the desired port address lines.

- 3. Establish the desired data on the I/O lines of the port.

- Make the R/W input of the port LOW and bring it HIGH after the specified amount of time.

- 5. Make the CE input HIGH to complete the operation.

When a read or write operation is initiated by a port and contention from the other port occurs, the implications are very simple. The losing port will see its BUSY line go LOW. The port must wait until a HIGH is indicated on the BUSY line. Thus in this case of contention, the operation did not really start when the port initiated it. Instead, the operation actually started when the BUSY line went HIGH. See the timing diagram for details.

#### Interrupts

Each port has an associated output called interrupt. The interrupt outputs are activated and deactivated by the on-chip logic when read and write operations occur with a particular address location. For example, if a write operation is performed by the left port with address (3FF)<sub>H</sub>, an on-chip latch is set. This latch drives the  $\overline{\text{INT}}_R$  output LOW. The latch is cleared only when a read operation from the right port using the address (3FF)<sub>H</sub> takes place. Similarly, if a write operation from the right port using the address (3FE)<sub>H</sub> occurs, a latch is set to drive the  $\overline{\text{INT}}_L$  output LOW. The  $\overline{\text{INT}}_L$  will go HIGH (latch is cleared) only after a read operation from the left port using the address (3FE)<sub>H</sub> occurs. As mentioned before, powering down a port to standby mode does not affect these outputs.

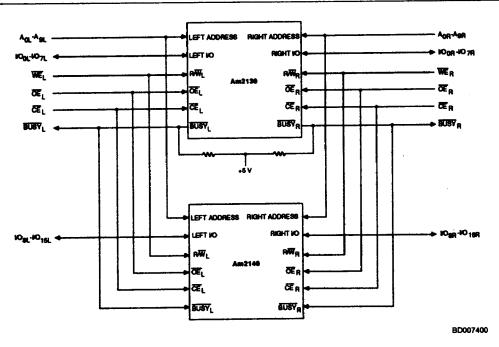

#### Depth Expansion Using Multiple Am2130s

The Am2130 has an intrinsic storage capacity of 1K bytes. However, it is simple to expand the storage capacity by using multiple devices. Figure 2 is a conceptual diagram of a 2K byte dual port memory system using two Am2130 devices. The principle behind such expansion is obvious: all that needs to be done is to decode the most significant system address to generate the individual  $\overline{\mathbb{CE}}$  inputs for the Am2130s. For

example in Figure 2,  $A_{10}$  is the most significant address bit. When this signal is LOW and  $\overline{\text{CE}}$  input is LOW, the chip enable input of the upper Am2130 goes LOW. Thus, the first 1K locations are selected for transactions. On the other hand, if  $A_{10}$  is HIGH and  $\overline{\text{CE}}$  is LOW, the chip enable input of the lower Am2130 goes LOW selecting the second 1K locations. As depicted in the figure, the address inputs of both Am2130 devices are bussed together. Similarly, the 1/O signals are also bussed to create the overall data bus. Also note that the other control signals are connected between the two devices.

In this example, we have not used the interrupt outputs. However, it should be noted that depth expansion using multiple devices does not change the operation of the interrupt outputs. The interrupt output of each device behaves as described before. Hence, the user must decide which interrupt output from which device will be used in his system.

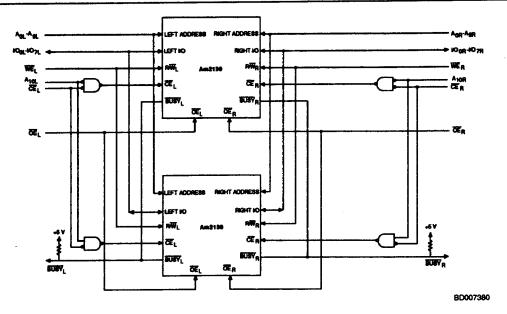

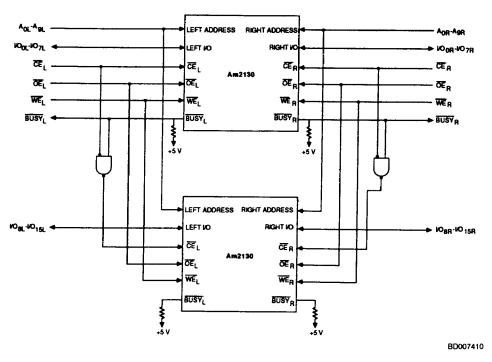

#### Width Expansion

The intrinsic width of the data word of the Am2130 is eight bits. However, it is possible to realize wider data words (multiples of 8) by using multiple devices. The instinctive solution of taking the required number of the devices and assigning the data bits to individual devices is potentially unreliable. As we know, the Am2130 has arbitration logic on the chip, and hence is called the master. When several of these masters are present, device-to-device variations and other factors may cause one device to give priority to one port, while another device gives priority to the other port. In essence both ports are busy! This is an undesirable situation and should not be allowed in operation. The most elegant way to avoid the situation is to allow only one device to arbitrate the contention. It is recommended that when expanding the width of the data words, the Am2130 be used as the master and a number of Am2140s be used as slave devices. The Am2140 does not have the arbitration capability; instead it accepts the BUSY outputs generated by the Am2130 as inputs.

Figure 3 is a conceptual diagram of a 16-bit system using one Am2130 and one Am2140. As can be seen, using master/ slave devices avoids external logic for expansion. For the sake of completeness of this discussion, it may be noted that it is indeed possible to expand the width using Am2130s only. However, external logic must be provided to prevent every device of the system from arbitrating. We want only one device to be the arbitrator. As explained in Figure 1, arbitration can be defeated by suitable control of the CE input of the Am2130.

Figure 4 shows a conceptual diagram of a 16-bit system using two Am2130s. Device 1 in this figure behaves as the master. The external logic shown in the figure ensures that the CE input of Device 2 is HIGH if the corresponding BUSY output of Device 1 is LOW. Thus the arbitration logic of Device 2 is prevented from taking part in resolving contention.

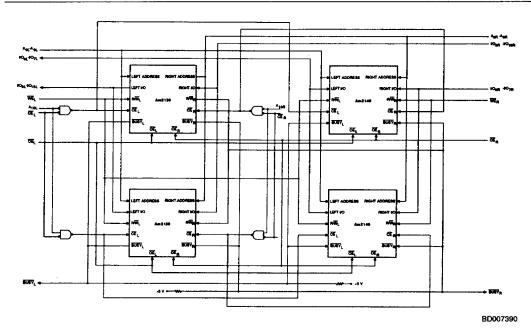

#### Simultaneous Width and Depth Expansion

By combining the depth and width expansion schemes discussed, it is possible to build systems with greater depth (multiples of 1K) and wider words (multiples of 8). Figure 5 shows a conceptual diagram of a 2K x 16 system. The operation of this scheme is understood by suitably combining the explanation of Figure 2 and Figure 3 and hence is not repeated here.

Figure 2. Conceptual Depth Expansion

Figure 3. Width Expansion with Master/Slave

Figure 4. Width Expansion with Master

Figure 5. Conceptual Diagram of a 2K x 16 System Using Master/Slave

TABLE 1. NON-CONTENTION READ/WRITE CONTROL

|      | Left | Port I | nputs                             |                  | Right P | ort Inp | nts       | Left I | lags | Right | Flags |                                                                                       |

|------|------|--------|-----------------------------------|------------------|---------|---------|-----------|--------|------|-------|-------|---------------------------------------------------------------------------------------|

| R/₩L | ČĒL  | ŌĒL    | A <sub>OL</sub> - A <sub>9L</sub> | R/W <sub>R</sub> | CER     | ŌĒR     | Aor - Aor | BUSYL  | INTL | BUSYR | INTR  | Function                                                                              |

| ×    | Н    | х      | ×                                 | х                | Х       | ×       | ×         | Н      | Х    | н     | X     | Left port in power-<br>down mode                                                      |

| ×    | ×    | х      | ×                                 | ×                | н       | ×       | x         | Н      | Х    | Н     | X     | Right part in power-<br>down mode                                                     |

| L    | L    | x      | ×                                 | х                | X       | ×       | ×         | Н      | Х    | х     | ×     | Data on left port<br>written to memory<br>location AoL - AgL                          |

| н    | L    | L      | х                                 | X                | ×       | ×       | х         | Н      | х    | х     | х     | Data in memory location A <sub>0L</sub> - A <sub>9L</sub> output on left port         |

| ×    | х    | ×      | x                                 | L                | L       | ×       | х         | ×      | х    | н     | х     | Data on right port<br>written to memory<br>location A <sub>OR</sub> - A <sub>SR</sub> |

| x    | х    | ×      | х                                 | н                | L       | L       | х         | ×      | X    | н     | X     | Data in memory<br>location Aon - Aon<br>output on right port                          |

| L    | L    | ×      | 3FF                               | х                | Х       | ×       | х         | н      | х    | Н     | L     | Left port flags right<br>port to read memory<br>location 3FF                          |

| x    | x    | ×      | x                                 | L                | L       | ×       | 3FE       | н      | L    | н     | ×     | Right port flags left<br>port to read memory<br>location 3FE                          |

### TABLE 2. BUSY ARBITRATION OF ADDRESS CONTENTION

| Left Port        |         |     |                                   | Right Port (Note |         |     | Right Port     |       |       |                           |  |

|------------------|---------|-----|-----------------------------------|------------------|---------|-----|----------------|-------|-------|---------------------------|--|

| R/₩ <sub>L</sub> | CEL     | ŌĒL | A <sub>OL</sub> - A <sub>OL</sub> | R/WR             | CEA     | ŌĒR | AoR - AgR      | BUSYL | BUSYR | Function                  |  |

| х                | L (LIV) | x   | Match                             | Х                | L       | х   | Match          | L     | Н     | Right-Port operation only |  |

| ×                | L       | Х   | Match<br>(LIV)                    | ×                | L       | х   | Match          | L     | н     | is permitted. (Note 3)    |  |

| ×                | L       | X   | Match                             | х                | L (LIV) | Х   | Match          | H     | L     | Left-port operation only  |  |

| ×                | L       | ×   | Match                             | х                | L       | Х   | Match<br>(LIV) | Н     | L     | is permitted. (Note 4)    |  |

#### TABLE 3. INTERRUPT FLAG

|                  |     | Left Po | ort                              |      |                  | ]              |     |                |      |                        |

|------------------|-----|---------|----------------------------------|------|------------------|----------------|-----|----------------|------|------------------------|

| R/W <sub>L</sub> | CEL | ŌĒL     | A <sub>0L</sub> -A <sub>9L</sub> | INTL | R/₩ <sub>R</sub> | Œ <sub>R</sub> | ŌĒR | Aor-Agr        | INTR | Function               |

|                  | _   | X       | 3FF                              | X    | X                | X              | Х   | Х1             | L    | Set INT <sub>R</sub>   |

| - <u>-</u>       | x   | X       | X <sub>1</sub>                   | ×    | н                | L              | L   | 3FF            | Н    | Reset INT <sub>R</sub> |

| ÷                | ~   | ×       | X <sub>1</sub>                   | 1    |                  | L              | ×   | 3FE            | х    | Set INT <sub>L</sub>   |

| Ĥ                |     | Ĺ       | 3FE                              | Н    | х                | X              | х   | X <sub>1</sub> | X    | Reset INTL             |

Key: H = HIGH

T = RIGH

L = LOW

LIV = Last Input Valid; meets t<sub>APS</sub> spec (Note 2)

X = Don't Care

X<sub>1</sub> = No Match, or

Same port deselected, or

Opposite port has priority

Notes: 1. INT Flags = X

- INT Flags = X

If LIV violates t<sub>APS</sub> spec then one of the two ports receives priority, and the remaining port's BUSY Flag goes LOW. However, there is an extremely rare metastable event which can occur when the arbitration circuitry cannot determine which port was "first" at the matching address. On this <u>rare</u> occurrence, both ports may momentarily receive BUSY = LOW signals until the metastable state is resolved (usually within a few nanoseconds). Thereafter, one port's BUSY remains LOW while the other completes its operation and resumes normal operation.

A Left-Port Read operation is also permitted if the Right-Port is also reading.

A Right-Port Read operation is also permitted if the Left-Port is also reading.

### **ABSOLUTE MAXIMUM RATINGS (Note 15)**

| Storage Temperature    | 65    | to | + 150 | °C |

|------------------------|-------|----|-------|----|

| Ambient Temperature    |       |    |       |    |

| with Power Applied     | 55    | to | + 125 | °C |

| Supply Voltage         |       |    |       |    |

| with Respect to Ground | – 0.5 | to | + 7.0 | V  |

| All Signal Voltages    | 3.5   | to | +7.0  | V  |

| Power Dissipation      |       |    |       |    |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES** (Note 8)

| Commercial (C) Devices Temperature (T <sub>A</sub> ) Supply Voltage (V <sub>CC</sub> ) | 0 to +70°C   |

|----------------------------------------------------------------------------------------|--------------|

| Military (M) Devices Temperature (T <sub>A</sub> ) Supply Voltage (V <sub>CC</sub> )   | 55 to +125°C |

Operating ranges define those limits between which the functionality of the device is guaranteed.

DC CHARACTERISTICS over operating range unless otherwise specified (for APL Products, Group A, Subgroups 1, 2, 3 are tested unless otherwise noted)

|                     |                                                              |                                                                                             |                                                                  | Am2130/ | /Am2140 |       |

|---------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------|---------|-------|

| Parameter<br>Symbol | Parameter Description Test Conditions                        |                                                                                             |                                                                  |         | Max.    | Units |

| lu                  | Input Load Current<br>(All Input Pins)                       | V <sub>CC</sub> = Max., V <sub>IN</sub> = GND to V <sub>CC</sub>                            | V <sub>CC</sub> = Max., V <sub>IN</sub> = GND to V <sub>CC</sub> |         |         | μΑ    |

| ILO                 | Output Leakage Current                                       | CE = V <sub>IH</sub> , V <sub>CC</sub> = Max.,<br>V <sub>OUT</sub> = GND to V <sub>CC</sub> |                                                                  |         | 10      | μА    |

|                     | Power Supply Current                                         | V <sub>CC</sub> = Max., CE = V <sub>IL</sub>                                                | C<br>Devices                                                     |         | 170     |       |

| loc                 | (Both Ports Active)                                          | Outputs Open                                                                                | M<br>Devices                                                     |         | 185     | mA    |

|                     | St                                                           | V <sub>CC</sub> = Min. to Max.,                                                             | C<br>Devices                                                     |         | 30      |       |

| ISB1                | Standby Current<br>(Both Ports Standby)                      | CEL and CER = VIH                                                                           | M<br>Devices                                                     |         | 40      | mA    |

|                     |                                                              | V <sub>CC</sub> = Max.,                                                                     | C<br>Devices                                                     |         | 110     |       |

| ISB2                | Standby Current<br>(One Port Standby)                        | CEL = VIL and CER = VIH or<br>CEL = VIH and CER = VIL                                       | M<br>Devices                                                     |         | 125     | mA    |

| VIL                 | Input LOW Voltage                                            |                                                                                             |                                                                  | -0.5    | 0.8     | ٧     |

| VIH                 | Input HIGH Voltage                                           |                                                                                             |                                                                  | 2.2     | 6.0     | ٧     |

| VOL1                | Output LOW Voltage<br>(I/O <sub>0</sub> – I/O <sub>7</sub> ) | I <sub>OL</sub> = 3.2 mA                                                                    |                                                                  |         | 0.4     | ٧     |

| V <sub>OL2</sub>    | Open-Drain Output LOW Voltage<br>(BUSY (Note 14), INT)       | I <sub>OL</sub> = 4 mA<br>(Note 7)                                                          |                                                                  |         | 0.5.    | ٧     |

| Voн                 | Output HIGH Voltage                                          | i <sub>OH</sub> = -1.0 mA<br>(Note 7)                                                       |                                                                  | 2.4     |         | ٧     |

#### **CAPACITANCE** (Note 9)

| Parameter<br>Symbol | Parameter<br>Description | Test Conditions | Min. | Max. | Units |

|---------------------|--------------------------|-----------------|------|------|-------|

| Cour                | Output Capacitance       |                 |      | 10   | ρF    |

| C <sub>IN</sub>     | input Capacitance        |                 |      | 10   | , P   |

Notes: See notes following Switching Waveforms.

**SWITCHING CHARACTERISTICS** over operating range unless otherwise specified (for APL Products, Group A, Subgroups 7, 8, 9, 10, 11 are tested unless otherwise noted)

|      |                     |                                                     |                    |                                                  |                                                  |      | An        | n2130    | /Am21    | 40   |          |       |

|------|---------------------|-----------------------------------------------------|--------------------|--------------------------------------------------|--------------------------------------------------|------|-----------|----------|----------|------|----------|-------|

|      |                     |                                                     |                    |                                                  | 55                                               |      | 70        | -        | 10       | _    | 12       |       |

| No.  | Parameter<br>Symbol | Parameter<br>Description                            | Test<br>Conditions | Min.                                             | Max.                                             | Min. | Max.      | Min.     | Max.     | Min. | Max.     | Units |

| READ | CYCLE (No           | ote 10)                                             |                    |                                                  |                                                  |      |           |          |          |      |          |       |

| 1    | t <sub>RC</sub>     | Read Cycle Time                                     |                    | 55                                               |                                                  | 70   |           | 100      | <u></u>  | 120  |          | пв    |

| 2    | taa                 | Address Access Time                                 |                    |                                                  | 55                                               |      | 70        |          | 100      | ļ    | 120      | ns    |

| 3    | †ACE                | Chip Enable Access Time                             |                    |                                                  | 55                                               |      | 70        |          | 100      |      | 120      | ns    |

| 4    | †AOE                | Output Enable Access Time                           |                    |                                                  | 30                                               |      | 35        | <u> </u> | 40       |      | 60       | ns    |

| 5    | ŧон                 | Output Hold from Address Change                     |                    | 5                                                |                                                  | 5    |           | 5        | <u> </u> | 5    | ļ        | ns    |

| 6    | 1LZ                 | Output Low Z Time                                   | (Notes 5 & 9)      | 5                                                |                                                  | 5    |           | 5        |          | 5    |          | ns    |

| 7    | 1 <sub>HZ</sub>     | Output High Z Time                                  | (Notes 5 & 9)      | 0                                                | 25                                               | 0    | 30        | 0        | 40       | 0    | 40       | ns    |

| 8    | t <sub>PU</sub>     | Chip Enable to Power Up Time                        | (Note 9)           | 0                                                | <u> </u>                                         | 0    |           | 0        |          | 0    | <u> </u> | ns    |

| 9    | t <sub>PD</sub>     | Chip Disable to Power Down Time                     | (Note 9)           |                                                  |                                                  | 35   | 35        |          | 50       |      | 60       | ns    |

| WRIT | E CYCLE (N          | lote 10)                                            |                    |                                                  |                                                  |      |           |          |          |      |          |       |

| 10   | twc                 | Write Cycle Time                                    |                    | 55                                               | 1                                                | 70   |           | 100      | 1        | 120  |          | ns    |

| 11   | tew                 | Chip Enable to End of Write                         |                    | 55                                               | <del></del>                                      | 65   |           | 90       |          | 100  |          | ns    |

| 12   | tAW                 | Address Valid to End of Write                       |                    | 50                                               | $\vdash$                                         | 65   | -         | 90       |          | 100  |          | ns    |

| 13   | tas                 | Address Setup Time                                  |                    | 0                                                |                                                  | 0    |           | 0        |          | 0    |          | ns    |

| 14   | twp                 | Write Pulse Width                                   |                    | 45                                               | <u> </u>                                         | 50   |           | 60       | <b>†</b> | 70   |          | ns    |

| 15   | twe                 | Write Recovery Time                                 |                    | 0                                                | †                                                | 0    |           | 0        |          | 0    |          | ns    |

| 16   | tDW t               | Data Valid to End of Write                          |                    | 30                                               | <del> </del>                                     | 35   | -         | 40       |          | 40   |          | ns    |

| 17   | t <sub>DH</sub>     | Data Hold Time                                      |                    | 0                                                |                                                  | 0    | <b></b>   | 0        | 1        | 0    |          | ns    |

| 18   | twz                 | Write Enabled to Output in High Z                   | (Notes 5 & 9)      | 0                                                | 25                                               | 0    | 30        | 0        | 40       | 0    | 50       | กร    |

| 19   | tow                 | Output Active from End of Write                     | (Notes 5 & 9)      | 0                                                | 1                                                | 0    |           | 0        |          | 0    | _        | ns    |

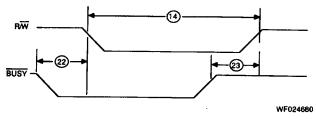

|      |                     | NG (Notes 7 & 14)                                   | <u></u>            |                                                  |                                                  | •    |           |          |          |      |          |       |

| 20   | tRC                 | Read Cycle Time                                     |                    | 55                                               | 1                                                | 70   | Ī         | 100      | Π        | 120  |          | ns    |

| 21   | twc                 | Write Cycle Time                                    |                    | 55                                               | <del> </del>                                     | 70   | <b>†</b>  | 100      | 1        | 120  | <b>†</b> | ns    |

| 22   | t <sub>BW</sub>     | BUSY to Write                                       | (Note 13)          | -5                                               | <del>                                     </del> | -5   | <b></b>   | -5       |          | -5   | <b>1</b> | ns    |

| 23   | \$WH                | Write Hold After BUSY                               | (Note 13)          | 20                                               |                                                  | 20   | <b>——</b> | 20       |          | 20   |          | ns    |

| 24   | †BAA                | BUSY Access Time to Address                         | (Note 9)           | <del>                                     </del> | 45                                               |      | 45        |          | 50       |      | 60       | ns    |

| 25   | †BDA                | BUSY Disable Time to Address                        | (Note 9)           | <u> </u>                                         | 40                                               |      | 45        |          | 50       |      | 60       | ns    |

| 26   | tBAC                | BUSY Access Time to Chip Enable or<br>Chip Select   | (Note 9)           |                                                  | 40                                               |      | 45        |          | 50       |      | 60       | ns    |

| 27   | †BDC                | BUSY Disable Time to Chip E nable or Chip<br>Select | (Note 9)           |                                                  | 40                                               |      | 45        |          | 50       |      | 60       | ns    |

| 28   | †APS                | Arbitration Priority Setup Time                     |                    | 10                                               |                                                  | 10   |           | 10       | Ī        | 10   |          | ns    |

| INTE | RRUPT TIMI          | NG (Note 7)                                         |                    |                                                  |                                                  |      |           |          |          |      |          |       |

| 29   | twins               | WE to Interrupt Set Time                            |                    |                                                  | 30                                               |      | 30        |          | 35       |      | 45       | ns    |

| 30   | teins               | CE to Interrupt Set Time                            |                    |                                                  | 50                                               |      | 55        |          | 60       |      | 70       | ns    |

| 31   | tins                | Address to Interrupt Set Time                       |                    | 1                                                | 50                                               |      | 55        |          | 60       |      | 70       | ns    |

| 32   | toinr               | Output Enable to Interrupt Reset Time               |                    | Τ                                                | 30                                               |      | 30        |          | 35       |      | 45       | ns    |

| 33   | tina                | Address to Interrupt Reset Time                     |                    |                                                  | 50                                               | 1    | 55        |          | 60       |      | 70       | ns    |

| 34   | tEINR               | Chip Enable to Interrupt Reset Time                 |                    |                                                  | 50                                               | T    | 55        |          | 60       |      | 70       | ns    |

Notes: See notes following Switching Waveforms.

#### SWITCHING TEST CIRCUITS

Test Loads A and B

Test Loads C and D

| TEST (        | TEST OUTPUT LOADS |  |  |  |  |  |  |  |

|---------------|-------------------|--|--|--|--|--|--|--|

| Test Load CAP |                   |  |  |  |  |  |  |  |

| Α             | 5 pF (Note 1)     |  |  |  |  |  |  |  |

| В             | 100 pF            |  |  |  |  |  |  |  |

| С             | 50 pF             |  |  |  |  |  |  |  |

| D             | 5 pF (Note 1)     |  |  |  |  |  |  |  |

Notes: 1. Includes Scope and Jig Capacitance.

### SWITCHING TEST WAVEFORM

| AC Test Conditions               |                             |  |  |  |  |  |

|----------------------------------|-----------------------------|--|--|--|--|--|

| Input Levels                     | GND to 3.0 V                |  |  |  |  |  |

| Input Rise and Fall Times        | 5 ns                        |  |  |  |  |  |

| Input Timing Reference<br>Levels | 1.5 V                       |  |  |  |  |  |

| Output Reference Levels          | 1.5 V                       |  |  |  |  |  |

| Test Output Load                 | See Test Output Loads Table |  |  |  |  |  |

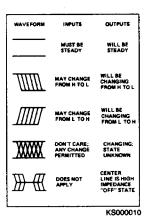

# SWITCHING WAVEFORMS KEY TO SWITCHING WAVEFORMS

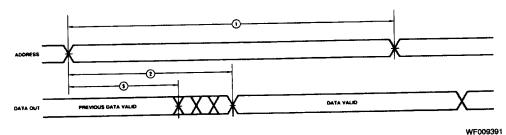

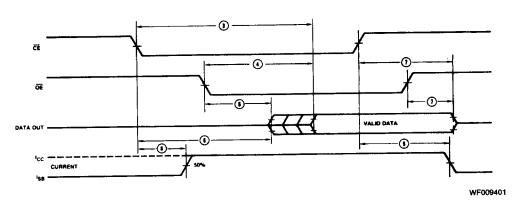

# READ CYCLE (Either Side)

Address Access (Notes 1 & 2)

CE and OE-Controlled Access (Notes 1 & 3)

# 4

# SWITCHING WAVEFORMS (Cont'd.)

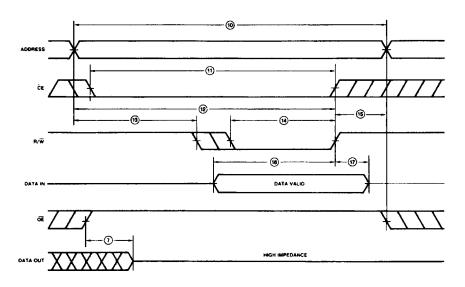

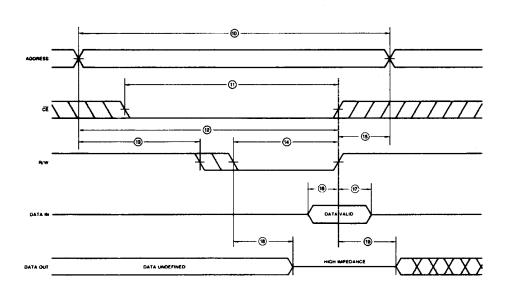

#### WRITE CYCLE (Either Side — Note 4)

WF009411

### **OE-Controlled Data Out**

WF009421

WE-Controlled Data Out (OE = V<sub>IL</sub>)

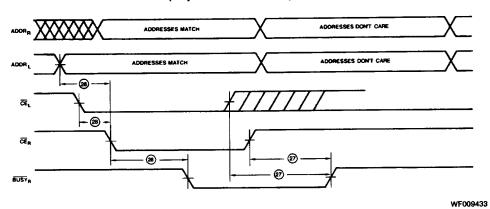

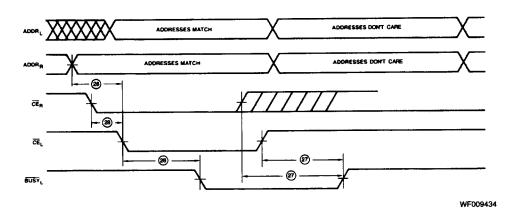

## BUSY FLAG TIMING (1 of 2) (Note 12) (Chip Enable Arbitration)

**CE<sub>R</sub> Valid Last**

CE<sub>L</sub> Valid Last

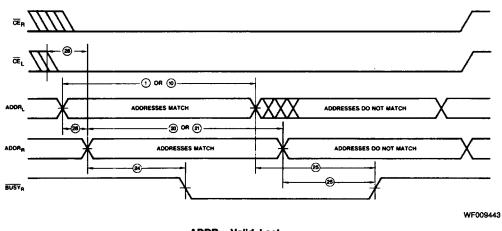

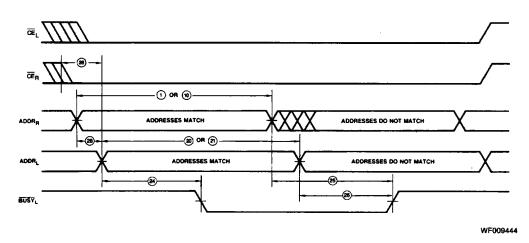

## BUSY FLAG TIMING (2 of 2) (Address Arbitration)

ADDR<sub>R</sub> Valid Last

ADDR<sub>L</sub> Valid Last

For Am2140 Only

# INTERRUPT TIMING (1 of 2) (Set INT Flag — Note 11)

Left Side Flags Right Side

Right Side Flags Left Side

# INTERRUPT TIMING (2 of 2) (Clear INT Flag)

Left Side Clears  $\overline{\text{INT}}_{L}$

Right Side Clears INTR

#### Notes\*

- 1. R/W is HIGH for Read Cycles.

- 2. Device is continuously enabled,  $\overline{CE} = V_{IL}$ ,  $\overline{OE} = V_{IL}$ .

- 3. Addresses valid prior to or coincident with CE transition LOW.

- 4. If CE and R/W go HIGH simultaneously, the outputs remain in the high-impedance state.

- 5. Transition is measured at 1.5 V on the input to VOH 500 mV and VOL + 500 mV on the outputs using the Load shown in Load A.

- 6. CEI = CER = VIL.

- 7. The BUSY and INT outputs are open drain. A pull-up resistor is required for system operation. For measurement purposes, Load C is used for HIGH-to-LOW transitions; output reference level is 1.5 V. Load D is used for LOW-to-HIGH transitions; output reference level is +500 mV from the output LOW voltage level.

- 8. For test and correlation purposes, ambient temperature is defined as the instant-on case temperature.

- 9. This parameter is guaranteed by design but is not 100% tested.

- 10. Except where indicated, I/O pins use Load B.

- 11. For a given port to Set or Clear an Interrupt Flag, 1) that port must have priority if addresses match and both  $\overline{CE}_L = \overline{CE}_R = LOW$ ; or 2) Addresses do not match.

- 12. If the last input valid transition, which would ordinarily cause a match, occurs at the same time that the opposite port address or CE changes to a no-match condition, then BUSY will remain HIGH (i.e., if there is never a match, then BUSY remains HIGH).

- 13. For Slave Am2140 only.

- 14. For Master Am2130 only.

- 15. Absolute Maximum Ratings are intended for user guidelines and are not tested.

- \* Notes listed correspond to reference made in the following sections: Operating Ranges

- DC Characteristics table

- Switching Characteristics table

- Switching Waveforms