## TYPES SN54176, SN54177, SN74176, SN74177 35-MHz PRESETTABLE DECADE AND BINARY COUNTERS/LATCHES

MAY 1971-REVISED DECEMBER 1983

- Reduced-Power Versions of SN54196, SN54197, SN74196, and SN74197 50-MHz Counters

- D-C Coupled Counters Designed to Replace Signetics 8280, 8281, 8290, and 8291 Counters in Most Applications

- Performs BCD, Bi-Quinary, or Binary Counting

- Fully Programmable

- Fully Independent Clear Input

- Guaranteed to Count at Input Frequencies from 0 to 35 MHz

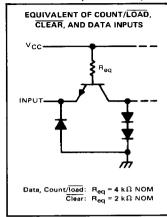

- Input Clamping Diodes Simplify System Design

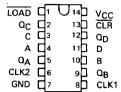

SN54176, SN54177 . . . J OR W PACKAGE SN74176, SN74177 . . . J OR N PACKAGE (TOP VIEW)

#### description

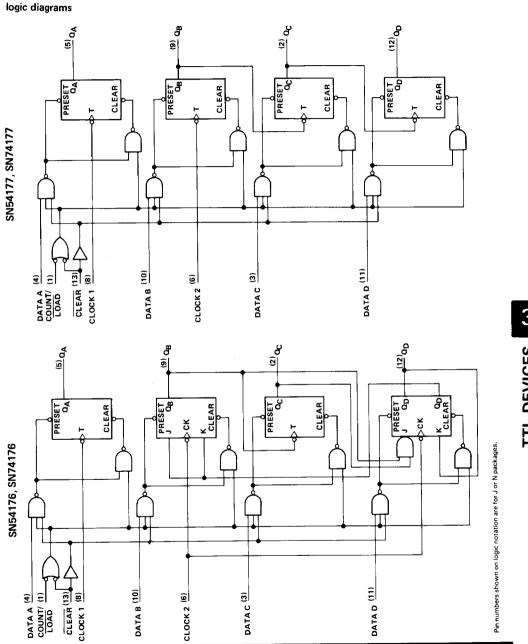

These high-speed monolithic counters consist of four d-c coupled master-slave flip-flops which are internally interconnected to provide either a divide-by-two and a divide-by-five counter (SN54176, SN74176) or a divide-by-two and a divide-by-eight counter (SN54177, SN74177). These counters are fully programmable; that is, the outputs may be preset to any state by placing a low on the count/load input and entering the desired data at the data inputs. The outputs will change to agree with the data inputs independent of the state of the clocks.

These counters may also be used as 4-bit latches by using the count/load input as the strobe and entering data at the data inputs. The outputs will directly follow the data inputs when the count/load is low, but will remain unchanged when the count/load is high and the clock inputs are inactive.

These high-speed counters will accept count frequencies of 0 to 35 megahertz at the clock-1 input and 0 to 17.5 megahertz at the clock-2 input. During the count operation, transfer of information to the outputs occurs on the negative-going edge of the clock pulse. The counters feature a direct clear which when taken low sets all outputs low regardless of the states of the clocks.

All inputs are diode-clamped to minimize transmission-line effects and simplify system design. The circuits are compatible with most TTL logic families. Typical power dissipation is 150 milliwatts. The SN54176 and SN54177 circuits are characterized for operation over the full military temperature range of  $-55^{\circ}$ C to  $125^{\circ}$ C; the SN74176 and SN74177 circuits are characterized for operation from  $0^{\circ}$ C to  $70^{\circ}$ C.

# typical count configurations

## SN54176 and SN74176

The output of flip-flop A is not internally connected to the succeeding flip-flops; therefore, the count may be operated in three independent modes:

- When used as a binary-coded-decimal decade counter, the clock-2 input must be externally connected to the QA output. The clock-1 input receives the incoming count, and a count sequence is obtained in accordance with the BCD count sequence function table shown at right.

- 2. If a symmetrical divide-by-ten count is desired for frequency synthesizers (or other applications requiring division of a binary count by a power of ten), the QD output must be externally connected to the clock-1 input. The input count is then applied at the clock-2 input and a divide-by-ten square wave is obtained at output QA in accordance with the bi-quinary function table.

#### FUNCTION TABLES SN54176, SN74176

DECADE (BCD) (See Note A) BI-QUINARY (5-2) (See Note B)

| COUNT |    | OUT                 | PUT                 |    |

|-------|----|---------------------|---------------------|----|

| COON  | αD | $\sigma^{\text{C}}$ | $\alpha_{\text{B}}$ | QA |

| 0     | L  | L                   | L                   | L  |

| 1     | L  | L                   | L                   | н  |

| 2     | L  | L                   | Н                   | L  |

| 3     | Ŀ  | L                   | н                   | н  |

| . 4   | L  | H                   | L                   | L  |

| 5     | L  | н                   | L                   | н  |

| 6     | L  | Н                   | Н                   | L  |

| 7     | L  | н                   | Н                   | н  |

| 8     | н  | L.                  | L                   | L  |

| 9     | н  | Ł                   | L                   | н  |

| ı | COUNT | OUTPUT |    |    |              |  |  |  |  |  |  |

|---|-------|--------|----|----|--------------|--|--|--|--|--|--|

| 1 | COUNT | QA     | αD | αc | $\sigma_{B}$ |  |  |  |  |  |  |

| ١ | 0     | Г      | L  | L  | L            |  |  |  |  |  |  |

|   | 1     | L      | L  | L  | н            |  |  |  |  |  |  |

|   | 2     | L.     | L  | Н  | L            |  |  |  |  |  |  |

|   | 3     | L      | L  | н  | Н            |  |  |  |  |  |  |

|   | 4     | L      | Н  | L  | L            |  |  |  |  |  |  |

|   | 5     | н      | L  | L  | L            |  |  |  |  |  |  |

|   | 6     | н      | L  | L  | Н            |  |  |  |  |  |  |

|   | 7     | н      | L  | Н  | L            |  |  |  |  |  |  |

|   | 8     | н      | L  | Н  | н            |  |  |  |  |  |  |

|   | 9     | н      | н  | L  | L            |  |  |  |  |  |  |

H = high level, L = low level

NOTES: A. Output QA connected to clock-2 input.

B. Output an connected to clock-1 input.

3. For operation as a divide-by-two counter and a divide-by-five counter, no external interconnections are required. Flip-flop A is used as a binary element for the divide-by-two function. The clock-2 input is used to obtain binary divide-by-five operation at the Q<sub>B</sub>, Q<sub>C</sub>, and Q<sub>D</sub> outputs. In this mode, the two counters operate independently; however, all four flip-flops are loaded and cleared simultaneously.

#### SN54177 and SN74177

The output of flip-flop A is not internally connected to the succeeding flip-flops, therefore the counter may be operated in two independent modes:

- When used as a high-speed 4-bit ripple-through counter, output Q<sub>A</sub> must be externally connected to the clock-2 input. The input count pulses are applied to the clock-1 input. Simultaneous divisions by 2, 4, 8, and 16 are performed at the Q<sub>A</sub>, Q<sub>B</sub>, Q<sub>C</sub>, and Q<sub>D</sub> outputs as shown in the function table at right.

- 2. When used as a 3-bit ripple-through counter, the input count pulses are applied to the clock-2 input. Simultaneous frequency divisions by 2, 4, and 8 are available at the QB, QC, and QD outputs. Independent use of flip-flop A is available if the load and clear functions coincide with those of the 3-bit ripple-through counter.

FUNCTION TABLE SN54177, SN74177

(See Note A)

| COUNT |                     | ουτ | PUT |                           |

|-------|---------------------|-----|-----|---------------------------|

| COUNT | $\sigma_{\text{D}}$ | αc  | αB  | $\mathbf{Q}_{\mathbf{A}}$ |

| 0     | L                   | L   | L   | L                         |

| 1     | L                   | L   | L   | н                         |

| 2     | L                   | L   | Н   | L                         |

| 3     | L                   | L   | н   | н                         |

| 4     | L                   | Н   | L   | L                         |

| 5     | L                   | н   | L   | н                         |

| 6     | L                   | Н   | Н   | L                         |

| 7     | L                   | Н   | Н   | н                         |

| 8     | н                   | L   | L   | L                         |

| 9     | н                   | L   | L   | н                         |

| 10    | н                   | L   | Н   | L                         |

| 11    | н                   | L   | н   | н                         |

| 12    | н                   | Н   | L   | L                         |

| 13    | н                   | н   | L   | н                         |

| 14    | н                   | Н   | н   | L                         |

| 15    | н                   | Н   | Н   | Н                         |

H = high level, L = low level

NOTE A: Output Q<sub>A</sub> connected

to clock-2 input.

## TYPES SN54176, SN54177, SN74176, SN74177 35-MHz PRESETTABLE DECADE AND BINARY COUNTERS/LATCHES

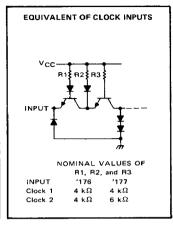

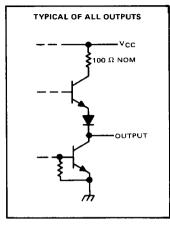

#### schematics of inputs and outputs

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1)      |    |     |     |    |    |     |     |    |     |    |     | ٠ |  |  |  |   |   |  |     |     |    | 7 V    |

|---------------------------------------|----|-----|-----|----|----|-----|-----|----|-----|----|-----|---|--|--|--|---|---|--|-----|-----|----|--------|

| Input voltage                         |    |     |     |    |    |     |     |    |     |    |     |   |  |  |  |   |   |  |     |     |    | 5.5 V  |

| Interemitter voltage (see Note 2)     |    |     |     |    |    |     |     |    |     |    |     |   |  |  |  |   |   |  |     |     |    |        |

| Operating free-air temperature range: | SN | 154 | 117 | 6, | S١ | 154 | 117 | 77 | Cir | cu | its |   |  |  |  | - | - |  | -55 | °C  | to | 125°C  |

|                                       |    |     |     |    |    |     |     |    |     |    |     |   |  |  |  |   |   |  |     |     |    | o 70°C |

| Storage temperature range             |    |     |     |    |    |     |     |    |     |    |     |   |  |  |  |   |   |  | -65 | °,C | to | 150°C  |

NOTES: 1. Voltage values are with respect to network ground terminal.

This is the voltage between two emitters of a multiple-emitter transistor. For this circuit, this rating applies between the clear and count/load inputs.

#### recommended operating conditions

|                                                      |                 | MIN     | NOM                                                                                        | MAX   | UNIT  |

|------------------------------------------------------|-----------------|---------|--------------------------------------------------------------------------------------------|-------|-------|

| 0 haden M                                            | SN54'           | 4.5     | 5                                                                                          | 5.5   | v     |

| Supply voltage, V <sub>CC</sub>                      | SN74'           | 4.75    | 5                                                                                          | 5.25  | ľ     |

| High-level output current, IOH                       |                 |         |                                                                                            | -800  | μА    |

| Low-level output current, IOL                        |                 |         |                                                                                            | 16    | mA    |

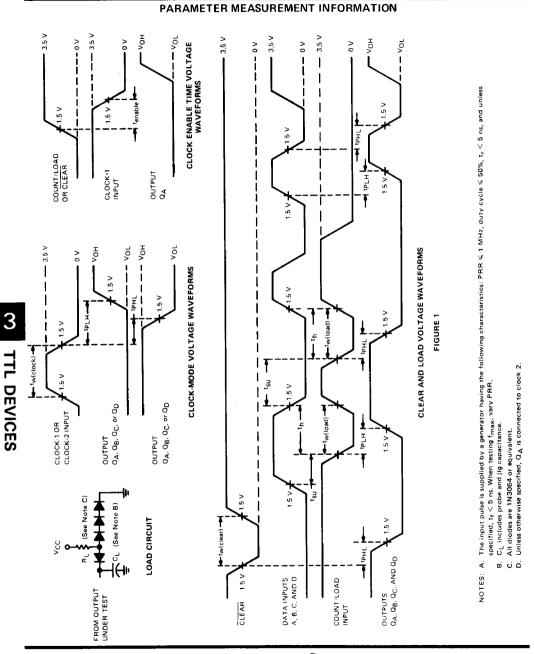

| 0 (                                                  | Clock-1 input   | 0       |                                                                                            | 35    | MHz   |

| Count frequency (see Figure 1)                       | Clock-2 input   | 0       |                                                                                            | 17.5  | IVIDZ |

|                                                      | Clock-1 input   | 14      |                                                                                            |       |       |

| Pulse width, t <sub>W</sub> (see Figure 1)           | Clock-2 input   | 28      |                                                                                            |       | 1     |

| Pulse width, t <sub>W</sub> (see Figure 1)           | Clear           | 20      |                                                                                            |       | ns    |

|                                                      | Load            | 25      |                                                                                            |       |       |

| A A hald since A                                     | High-level data | tw(load | d)                                                                                         |       |       |

| Input hold time, th (see Figure 1)                   | Low-level data  | tw(loa  | d)                                                                                         |       | ns    |

| · · · · · · · · · · · · · · · · · · ·                | High-level data | 15      |                                                                                            |       | ns    |

| Input setup time, t <sub>SU</sub> (see Figure 1)     | Low-level data  | 20      | 5 5 5.5<br>5 5 5.25<br>-800<br>16<br>0 35<br>0 17.5<br>4 8<br>0 5<br>load)<br>load)<br>5 0 | 1 ''' |       |

| Count enable time, tenable (see Note 3 and Figure 1) |                 | 25      |                                                                                            |       | ns    |

|                                                      | SN54'           | -55     |                                                                                            | 125   | °c    |

| Operating free-air temperature, TA                   | SN74'           | 0       |                                                                                            | 70    | ] [   |

NOTE 3: 'Minimum count enable time is the interval immediately preceding the negative-going edge of the clock pulse during which interval the count/load and clear inputs must both be high to ensure counting.

## TYPES SN54176, SN54177, SN74176, SN74177 35-MHz PRESETTABLE DECADE AND BINARY COUNTERS/LATCHES

#### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                  | DADAMETER                 |                  | T-0T                                               | CONDITIONS                                         |       | SN541 | 176, SN | 74176 | SN54 | 177, SN | 74177 |      |

|------------------|---------------------------|------------------|----------------------------------------------------|----------------------------------------------------|-------|-------|---------|-------|------|---------|-------|------|

|                  | PARAMETER                 |                  | 1681                                               | CONDITIONS.                                        |       | MIN   | TYP‡    | MAX   | MIN  | TYP‡    | MAX   | UNIT |

| VIH              | High-level input voltage  |                  |                                                    |                                                    |       | 2     |         |       | 2    |         |       | ٧    |

| VIL              | Low-level input voltage   |                  |                                                    |                                                    |       |       |         | 8.0   |      |         | 8,0   | ٧    |

| Vικ              | Input clamp voltage       |                  | V <sub>CC</sub> = MIN,                             | I <sub>J</sub> = -12 mA                            |       |       |         | -1.5  |      |         | -1.5  | ٧    |

| v <sub>OH</sub>  | High-level output voltage | )                | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, | V <sub>IH</sub> = 2 V,<br>I <sub>OH</sub> = -800 µ | ıΑ    | 2.4   | 3.4     |       | 2.4  | 3.4     |       | ٧    |

| v <sub>o</sub> L | Low-level output voltage  |                  | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, | V <sub>IH</sub> = 2 V,<br>I <sub>OL</sub> = 16 mA  | f     |       | 0.2     | 0.4   |      | 0.2     | 0.4   | ٧    |

| Ιį               | Input current at maximu   | m input voltage  | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 5.5 V                             |       |       |         | 1     |      |         | 1     | mA   |

|                  |                           | Data, count/load |                                                    |                                                    |       |       |         | 40    |      |         | 40    |      |

| ЯН               | High-level input current  | Clear, clock 1   | V <sub>CC</sub> = MAX,                             | $V_1 = 2.4 \text{ V}$                              |       |       |         | 80    |      |         | 80    | μΑ   |

|                  |                           | Clock 2          |                                                    |                                                    |       |       |         | 120   |      |         | 80    |      |

|                  |                           | Data, count/load |                                                    |                                                    |       |       |         | -1.6  |      |         | -1.6  |      |

| 1                | Low-level input current   | Clear            | V <sub>CC</sub> = MAX,                             | V. = 0.4 V                                         |       |       |         | -3.2  |      |         | -3.2  | mA   |

| ΊL               | Low-level input current   | Clock 1          | ACC - MAX,                                         | V  - 0.4 V                                         |       |       |         | -4.8  |      |         | -4.8  | """  |

|                  |                           | Clock 2          |                                                    |                                                    |       |       |         | -4.8  |      |         | -3.2  |      |

| 1                | Chart -init autot au-     | 2 ****           | V <sub>CC</sub> = MAX                              | ,                                                  | SN54' | -20   |         | -57   | -20  |         | -57   | mA   |

| los              | Short-circuit output curr | enra             | ACC = MAX                                          |                                                    | SN74' | -18   | ,       | -57   | -18  |         | -57   |      |

| Icc              | Supply current            |                  | V <sub>CC</sub> = MAX,                             | See Note 4                                         |       |       | 30      | 48    |      | 30      | 48    | mA   |

<sup>†</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operation conditions.

NOTE 4:  $I_{CC}$  is measured with all inputs grounded and all outputs open.

### switching characteristics, VCC = 5 V, R<sub>L</sub> = 400 $\Omega$ , C<sub>L</sub> = 15 pF, T<sub>A</sub> = 25°C, see figure 1

| PARAMETER <sup>♦</sup> | 70014 (INIDIAT) | TO (OUTPUT)                                                       | SN54 | 176, SN | 174176 | SN541 | UNIT |     |        |

|------------------------|-----------------|-------------------------------------------------------------------|------|---------|--------|-------|------|-----|--------|

|                        | FROM (INPUT)    | 10 (001701)                                                       | MIN  | TYP     | MAX    | MIN   | TYP  | MAX | UNI    |

| f <sub>max</sub>       | Clock 1         | QΑ                                                                | 35   | 50      |        | 35    | 50   |     | MHz    |

| <sup>t</sup> PLH       | Clock 1         | QA                                                                |      | 8       | 13     |       | 8    | 13  | ns     |

| tPHL                   | Cluck I         | G <sub>A</sub>                                                    |      | 11      | 17     |       | 11   | 17  | 1 '''  |

| tPLH .                 | Clock 2         | QB                                                                |      | 11      | 17     |       | 11   | 17  | ns     |

| tPHL                   | Clock 2         | αg                                                                |      | 17      | 26     |       | 17   | 26  | 1 '''  |

| <sup>t</sup> PLH       | Cłock 2         | 0.5                                                               |      | 27      | 41     |       | 27   | 41  | ns     |

| tPHL                   | CIOCK 2         | αc                                                                |      | 34      | 51     |       | 34   | 51  | '"     |

| tPLH .                 | Clock 2         | QD                                                                |      | 13      | 20     |       | 44   | 66  | ns     |

| tPHL                   | Cluck 2         | Ф                                                                 |      | 17      | 26     |       | 50   | 75  | 1 ''`  |

| tPLH                   | 4.0.00          | Q <sub>A</sub> , Q <sub>B</sub> , Q <sub>C</sub> , Q <sub>D</sub> |      | 19      | 29     |       | 19   | 29  | ns     |

| <sup>‡</sup> PHL       | A, B, C, D      | QA, GB, GC, GD                                                    |      | 31      | 46     |       | 31   | 46  | ] '''  |

| tPLH .                 | 1 1             | A                                                                 |      | 29      | 43     |       | 29   | 43  | ns     |

| tPHL                   | Load            | Any                                                               |      | 32      | 48     |       | 32   | 48  | ] '''s |

| tPHL                   | Clear           | Any                                                               |      | 32      | 48     |       | 32   | 48  | ns     |

$<sup>^{\</sup>lozenge}f_{max} \equiv maximum count frequency$

$<sup>\</sup>ddagger$  All typical values are at  $V_{CC}$  = 5 V,  $T_{A}$  =  $25^{\circ}C.$

<sup>¶</sup> QA outputs are tested at i<sub>OL</sub> = 16 mA plus the limit value of I<sub>IL</sub> for the clock-2 input. This permits driving the clock-2 input while fanning out to 10 Series 54/74 loads.

<sup>§</sup> Not more than one output should be shorted at a time.

tp\_H = propagation delay time, low-to-high-level output

$_{\text{tpHL}}^{-}\equiv$  propagation delay time, high-to-low-level output