FIE D

# **Micro Power Systems**

T-51-10-12 MP574A

Complete 12-Bit, 20µsec Analog-to-Digital Converter with Microprocessor Interface

### **FEATURES**

- Complete 12-Bit A/D Converter with Reference **Clock and Three-state Outputs**

- Full 8- or 16-Bit Microprocessor Bus Interface

- 200 ns Bus Access Time

- Guaranteed Linearity Over Temperature

- No Missing Codes Over Temperature

- ESD Protection: 1500 V Minimum

- Fast Conversion (20 μsec)

- Precision Reference for Long Term Stability and Low Gain T.C.

- Low Power: 240 mW typ.

- Guaranteed Performance at ±12 V and ±15 V

- PDIP, CDIP, SOIC & PLCC Packages Available

### GENERAL DESCRIPTION

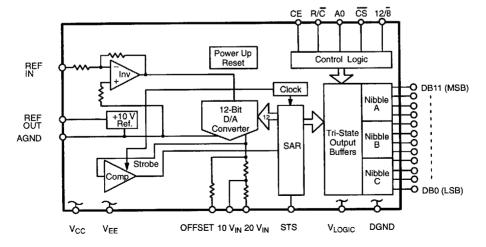

The MP574A is a complete 12-bit A/D converter with 3-state output buffers for direct interfacing to 8- and 16-bit microprocessor busses. Implemented in advanced BiCMOS, the converter combines a SAR, a 12-bit decoded D/A, a comparator and a precision reference with the appropriate control logic to achieve an accurate conversion in 20µs. The 12/8 mode control TTL is microprocessor compatible, such that users may switch freely between the full 12-bit and short cycled 8-bit formats.

A unique comparator input design reduces kickback noise to the source and the proprietary decoded D/A section assures no missing codes for all grades. The reference has enough output drive that no buffer is required at REF IN, even with 12 VDC operation. Precision thin film scaling and offset resistors are laser trimmed to provide the four calibrated ranges, 0 to +10 V and 0 to +20 V in the unipolar mode and ±5 V and ±10 V for bipolar applications.

Specified for operation over the commercial (0 to 70°C) and military (-55 to +125°C) temperature ranges, the MP574A is available in Plastic (PDIP) and Ceramic (CDIP) dual-in-line, Surface Mount (SOIC), and Plastic leaded chip carrier (PLCC) packages.

### SIMPLIFIED BLOCK DIAGRAM

### ORDERING INFORMATION

| Package<br>Type | Temperature<br>Range | Part No.      | INL<br>(LSB) | DNL<br>(LSB) | Gain Error<br>(% FSR) |

|-----------------|----------------------|---------------|--------------|--------------|-----------------------|

| Plastic Dip     | 0 to 70°C            | MP574AJN      | ±1           | ±1           | ±0.3                  |

| Plastic Dip     | 0 to 70°C            | MP574AKN      | 土1/2         | ±1           | ±0.3                  |

| SOIC            | 0 to 70°C            | MP574AJS      | ±1           | 土1           | ±0.3                  |

| SOIC            | 0 to 70°C            | MP574AKS      | ±1/2         | 土1           | ±0.3                  |

| PLCC            | 0 to 70°C            | MP574AJP      | ±1           | 土1           | ±0.3                  |

| PLCC            | 0 to 70°C            | MP574AKP      | ±1/2         | ±1           | ±0.3                  |

| Ceramic Dip     | -55 to +125°C        | MP574ASD/883* | ±1           | ±1           | ±0.3                  |

| Ceramic Dip     | -55 to +125°C        | MP574ATD*     | ±1           | 上1/2         | +0.3                  |

| Ceramic Dip     | -55 to +125°C        | MP574ATD/883* | ±1           | ±1/2         | ±0.3                  |

| Ceramic Dip     | –55 to +125°C        | MP574AUD*     | ±1           | ±1/2         | ±0.3                  |

| Ceramic Dip     | -55 to +125°C        | MP574AUD/883* | ±1           | ±1/2         | +0.3                  |

<sup>\*</sup>Contact factory for availability.

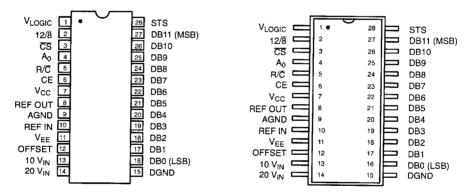

### **PIN CONFIGURATIONS**

28 Pin PDIP, CDIP (0.600") N28, D28

28 Pin SOIC, (Jedec, 0.300") S28

28 Pin PLCC P28

### **PIN OUT DEFINITIONS**

28

Status

### **DEFINING THE CONTROL FUNCTIONS**

| PIN NO. | NAME                | DESCRIPTION                                                 | FUNCTION   | DEFINITION             | FUNCTION                                                                                             |

|---------|---------------------|-------------------------------------------------------------|------------|------------------------|------------------------------------------------------------------------------------------------------|

| 1       | V <sub>LOGIC</sub>  | +5 V Logic Supply                                           | CE         | Chip Enable            | Typically used as clock synchronization with μp                                                      |

| 2       | 12/8                | Select format of Output Bits (8 or 12) (TTL-compatible.)    |            |                        | Must be high (1) for a conversion to start     Must be high (1) to read data on                      |

| 3       | CS                  | Chip Select. Enables conversion on falling clock edge.      |            |                        | the output 4. Transition may be used to initiate                                                     |

| 4       | A0                  | Access high 8 bits or low 4 bits plus 4 zeroes (read mode). | CS         | Chip Select            | conversion  1. Typically the address pin when                                                        |

| 5       | R/C                 | Read/Convert: main control for<br>Stand-Alone operation.    |            | Grap Goldon            | used with a microprocessor.  2. Must be low (0) for a conversion to start or read data at the output |

| 6       | CE                  | Chip Enable. Enables conversion on rising clock edge.       |            |                        | Transition may be used to initiate conversion                                                        |

| 7       | V <sub>CC</sub>     | +12 V to +15 V                                              | R/C        | Read/Convert           | 1. Unitiate conversion                                                                               |

| 8       | REF OUT             | Output from internal +10 V reference.                       |            |                        | 2. Tinitiate read                                                                                    |

| 9       | AGND                | Analog Ground                                               | A0         | Address                | Selects conversion mode 12 Bits if low (0) 8 Bits if high (1)                                        |

| 10      | REF IN              | Input for Voltage Reference                                 | 1          |                        | In read mode Ao selects the output<br>format. If low (0) then 8 MSBs                                 |

| 11      | VEE                 | -12 V to -15 V                                              | H          |                        | (high and middle byte) are enabled. If high (1) then the 4 LSBs are                                  |

| 12      | OFFSET              | Voltage input for Bipolar operation, or zero adjust         |            |                        | enabled.                                                                                             |

| 13      | 10 V <sub>IN</sub>  | Input for 0 to +10 V or -5 V to +5 V operation. *           | 12/8       | Output Format          | Usually hard-wired     Normal 12 Bit format if high (1)     8-Bit format as set by Ao if low (0)     |

| 14      | 20 V <sub>IN</sub>  | Input for 0 to +20 V or -10 V to +10 V operation            | * When not | I<br>in use, NC to avo | oid noise pick-up.                                                                                   |

| 15      | DGND                | Digital Ground                                              |            |                        |                                                                                                      |

| 16-27   | Output<br>Data Bits | DB0 (LSB) to DB11 (MSB)                                     |            |                        |                                                                                                      |

### **MP574A**

### **ELECTRICAL CHARACTERISTICS**

(@ +25°C with  $V_{CC}$  = +15 V,  $V_{LOGIC}$  = +5 V,  $V_{EE}$  = -15 V unless otherwise indicated)

| Description                                                                                                                                                                                                                                                                          | Min                 | MP574A  |                              |                     | MP574A  |                              |                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------|------------------------------|---------------------|---------|------------------------------|----------------------------------------------|

| RESOLUTION                                                                                                                                                                                                                                                                           |                     | Тур     | Max                          | Min                 | Тур     | Max                          | Units                                        |

|                                                                                                                                                                                                                                                                                      | 12                  |         |                              | 12                  |         |                              | Bits                                         |

| LINEARITY ERROR @ +25°C Tmin to Tmax                                                                                                                                                                                                                                                 |                     |         | ±1<br>±1                     |                     |         | ±1/2<br>±1/2                 | LSB<br>LSB                                   |

| DIFFERENTIAL LINEARITY ERROR<br>(Minimum resolution for which no missing<br>codes are guaranteed)<br>Tmin to Tmax                                                                                                                                                                    | 12                  |         |                              | 12                  |         |                              | Bits                                         |

| UNIPOLAR OFFSET (Adjustable to zero)                                                                                                                                                                                                                                                 |                     |         | <u>+</u> 2                   |                     |         | <u>+</u> 1                   | LSB                                          |

| BIPOLAR OFFSET (1) (Adjustable to zero)                                                                                                                                                                                                                                              | 1                   |         | <u>±</u> 4                   |                     |         | <u>±</u> 4                   | LSB                                          |

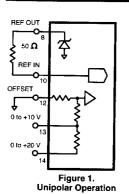

| FULL-SCALE CALIBRATION ERROR (with fixed 50Ω resistor from REF OUT to REF IN) (Adjustable to zero)                                                                                                                                                                                   |                     |         | <u>+</u> 0.3                 |                     |         | ±0.3                         | % of Fs                                      |

| TEMPERATURE RANGE                                                                                                                                                                                                                                                                    | 0                   |         | +70                          | 0                   |         | +70                          | °c                                           |

| TEMPERATURE COEFFICIENTS (using internal reference) Tmin to Tmax Unipolar Offset Bipolar Offset Full-Scale Calibration                                                                                                                                                               |                     |         | ±2(10)<br>±2(10)<br>±9(50)   |                     |         | ±1(5)<br>±1(5)<br>±5(27)     | LSB(ppm/°C)*<br>LSB(ppm/°C)*<br>LSB(ppm/°C)* |

| POWER SUPPLY REJECTION  Max change in Full Scale Calibration $V_{CC} = 15 \text{ V} \pm 1.5 \text{ V} \text{ or } 12 \text{ V} \pm 0.6 \text{ V}$ $V_{LOGIC} = 5 \text{ V} \pm 0.5 \text{ V}$ $V_{EE} = -15 \text{ V} \pm 1.5 \text{ V} \text{ or } -12 \text{ V} \pm 0.6 \text{ V}$ |                     |         | ±2<br>±1/2<br>±2             |                     |         | ±1<br>±1/2<br>±1             | LSB<br>LSB<br>LSB                            |

| ANALOG INPUT Input Ranges Bipolar, 10 V <sub>IN</sub> 20 V <sub>IN</sub> Unipolar, 10 V <sub>IN</sub> 20 V <sub>IN</sub> input Impedance 10 V <sub>IN</sub> 20 V <sub>IN</sub>                                                                                                       | -5<br>-10<br>0<br>0 | 5<br>10 | +5<br>+10<br>+10<br>+20<br>7 | -5<br>-10<br>0<br>0 | 5<br>10 | +5<br>+10<br>+10<br>+20<br>7 | V<br>V<br>V<br>V<br>kΩ<br>kΩ                 |

| DIGITAL CHARACTERISTICS (2) Inputs (CE, CS, R/C, A0, 12/8) Logic "1" Voltage Logic "0" Voltage Current Capacitance                                                                                                                                                                   | +2.0<br>-0.5<br>-5  | 5       | +5.5<br>+0.8<br>+5           | +2.0<br>-0.5<br>-5  | 5       | +5.5<br>+0.8<br>+5           | V<br>V<br>μ <b>Α</b><br>pF                   |

| Outputs (DB11-DB0, STS) Logic "1" Voltage (I <sub>SOURCE</sub> ≤ 500μA) Logic "0" Voltage (I <sub>SINK</sub> ≤ 1.6mA) Leakage (DB11-DB0, High-Z State) Capacitance                                                                                                                   | +2.4<br>-5          | 5       | +0.4<br>+5                   | +2.4<br>-5          | 5       | +0.4<br>+5                   | V<br>V<br>μA<br>pF                           |

<sup>\*</sup> ppm information for reference only.

Specifications subject to change without notice

### **ELECTRICAL CHARACTERISTICS (CON'T)**

|                                                                                                                              | MP574AJN/P             |             |                                   | Ĭ                      |             |                                   |                         |

|------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------|-----------------------------------|------------------------|-------------|-----------------------------------|-------------------------|

| Description                                                                                                                  | Min                    | Тур         | Max                               | Min                    | Тур         | Max                               | Units                   |

| POWER SUPPLIES Operating Range VLOGIC VCC VEE Operating Current ILOGIC ICC IEE                                               | +4.5<br>+11.4<br>-11.4 | 3<br>7<br>8 | +5.5<br>+16.5<br>-16.5<br>6<br>10 | +4.5<br>+11.4<br>-11.4 | 3<br>7<br>8 | +5.5<br>+16.5<br>-16.5<br>6<br>10 | V<br>V<br>V<br>mA<br>mA |

| POWER DISSIPATION                                                                                                            |                        | 240         | 360                               |                        | 240         | 360                               | mW                      |

| INTERNAL REFERENCE VOLTAGE Output current (available for external loads) (External load should not change during conversion) | 9.95<br>1.5            | 10.0<br>5   | 10.05                             | 9.95<br>1.5            | 10.0<br>5   | 10.05                             | V<br>mA                 |

### NOTES:

Bipolar offset zero transition.

Detailed timing specifications appear in the timing section.

Specifications subject to change without notice

### ABSOLUTE MAXIMUM RATINGS (1, 2) (TA = +25°C unless otherwise noted)

| V <sub>CC</sub> to DGND 0 to +16.5 V                                                | 20 V <sub>IN</sub> to AGND                                            |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| V <sub>EE</sub> to DGND 0 to -16.5 V                                                | REF OUT Indefinite short to DGND,  Momentary short to V <sub>CC</sub> |

| V <sub>LOGIC</sub> to DGND 0 to +7 V                                                | Package Power Dissipation Rating to 75°C                              |

| AGND to DGND                                                                        | PDIP, CDIP, SOIC, PLCC 1000mW                                         |

| Control Inputs (CE, CS, A0, 12/8, R/C)<br>to DGND0.5 V to V <sub>LOGIC</sub> +0.5 V | Derates above 75°C 14mW/°C                                            |

|                                                                                     | Lead Temperature, Soldering +300°C, 10 Sec                            |

| Analog Inputs (REF IN, OFFSET, 10 V <sub>IN</sub> ) to AGND ±16.5 V                 | Storage Temperature –65°C to +150°C                                   |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at or above this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Any input pin which can see a value outside the absolute maximum ratings should be protected by Schottky diode clamps (HP5082-2835) from input pin to the supplies.

### **APPLICATION DATA**

The MP574A is a complete A/D converter system, with its own built-in reference and clock. It may be used by itself ("standalone" operation), or it may be interfaced with a microprocessor which can control both conversion and formatting of output.

Successful application of the MP574A requires careful attention to four main areas:

- 1) Physical layout.

- Connection/Trimming according to mode of operation.

- Conditioning of input signals.

- Controlling and Timing considerations.

### **Physical Layout**

The 12-bit accuracy of the MP574A represents a dynamic range of 72dB. In order that this be preserved, thorough precautions must be taken to avoid any interfering signals, whether conducted or radiated. It is therefore recommended that one:

- Avoid placing the chip and its analog signals near logic traces. In general, using a double sided printed circuit card with a good ground plane on the component side is recommended. Routing analog signals between ground traces will help isolate digital control logic. If these lines cross, do so at right angles.

- Power supplies should be quiet and well regulated. Grounds should be tied together at the package and back to the system ground with a single path. Bypass the supplies at the device with a 0.01 to 0.1  $\mu F$  ceramic cap and a 10-47 µF tantalum type, in parallel.

- Use well-regulated and filtered power supplies.

### Connection/Trimming

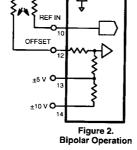

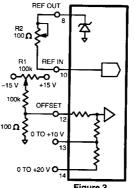

There are two modes of operation, each with two submodes. Unipolar, 0 to +10 V or 0 to +20 V; and Bipolar, -5 V to +5 V or -10V to +10 V. If the accuracy of the MP574A as supplied is sufficient for the application, connect the device as shown in Figure 1.and Figure 2.

If greater accuracy is required, the part may be trimmed. The procedure is as follows:

Unipolar Mode: Connect MP574A as shown in Figure 3. R1 is used to adjust the converter offset so that an input voltage equivalent to 1/2 LSB will produce the first change in the output codes (0000 0000 0000 to 0000 0000 0001). This input is 1.22 mV for the 10 V scale (pin 13) or 2.44 mV for the 20 V scale (pin 14). Using one of these inputs, R1 should be adjusted until the output flickers between the above code values.

Having trimmed zero scale (adjusted the offset), the all -"1"s level can be set using R2 (gain adjust). Apply an input of 9.9963V to pin 13 (or 19.9927V to pin 14). This is 1.5 or 1 1/2 LSB less than 10 V (20 V). Adjust R2 until the output flickers between codes 1111 1111 1110 and 1111 1111 1111.

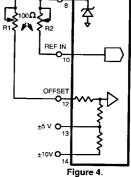

Bipolar Mode: In the bipolar mode the user can either adjust the  $\pm$  full scale limits, or adjust the zero transition and gain (+ full scale), as is best suited to the end application.

- To set ± full scale: Connect MP574A as shown in Figure 4. Apply -4.9988 V to pin 13 (or -9.9976 V to pin 14) and adjust R1 for flicker between output codes 0000 0000 0000 and 0000 0000 0001. Then apply +4.9963 V to pin 13 (or +9.9927 V to pin 14) and adjust R2 for flicker between output codes 1111 1111 1110 and 1111 1111 1111.

- To set Zero Transition and Gain: Connect MP574A as shown in Figure 4. Apply 0.0000V to pin 13 (for +5 V full scale applications) or pin 14 (for +10 V full scale systems) and adjust R1 until the output code flickers between 0111 1111 1111 and 1000 0000 0000. Then apply +4.9963 V to pin 13 (or +9.9927 V to pin 14) and adjust R2 for flicker between output codes 1111 1111 1111 and 1111 1111 1110.

REF OU

Figure 3. **Unipolar Operation** with Trim Adjustments

**Bipolar Operation** with Trim Adjustments

### **MP574A**

### **Control and Timing Considerations**

The MP574A can be operated in the stand-alone mode, with one line for control and everything else hard-wired; or under microprocessor control, where changes can be made dynamically. There are 5 control lines: CE, CS, R/C Ao and 12/8 with their functions described in the box "Defining the Control Functions". The role each line plays in control is shown in the MP574A Truth Table.

### TRUTH TABLE

| CONTROL INPUTS |               |     | NPUT | s  | MP574A OPERATION                        |

|----------------|---------------|-----|------|----|-----------------------------------------|

| CE             | <del>cs</del> | R/C | 12/8 | Αo |                                         |

| 0              | х             | х   | x    | х  | No Operation                            |

| х              | 1             | Х   | Х    | Х  | No Operation                            |

| 1              | 0             | ↓   | х    | 0  | Initiates 12-Bit Conversion             |

| 1              | 0             | ↓   | x    | 1  | Initiates 8-Bit Conversion              |

| 1              | 0             | 0   | х    | 0  | Initiates 12-Bit Conversion             |

| 1              | 0             | 0   | x    | 1  | Initiates 8-Bit Conversion              |

| 1              | ↓             | 0   | x    | 0  | Initiates 12-Bit Conversion             |

| 1              | ↓             | 0   | x    | 1  | Initiates 8-Bit Conversion              |

| 1              | 0             | 1   | 1    | Х  | Enables 12-Bit Parallel Output          |

| 1              | 0             | 1   | 0    | 0  | Enables 8 MSB's                         |

| 1              | 0             | 1   | 0    | 1  | Enables 4 LSB's and 4 Trailing<br>Zeros |

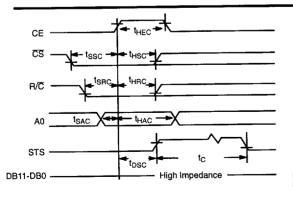

### TIMING

The MP574A is easily interfaced to a wide variety of microprocessors and other digital systems. Discussion of the timing requirements of the MP574A control signals will provide the system designer with useful insight into the operation of the device.

Figure 5. shows a complete timing diagram for the MP574A convert start operation. R/C should be low before both CE and CS are asserted; If R/C is high, a read operation will momentarily occur, possibly resulting in system bus contention.

Either CE or CS may be used to initiate a conversion. We recommend using CE, however, as it includes one less propagation delay than CS. As shown in Figure 5., CE is used. If CS is used to trigger the conversion the specified set-up times will be longer.

Once a conversion is started and the STS line goes high, convert start commands will be ignored until the conversion cycle is completed. The output data buffers cannot be enabled during conversion. However, all inputs and outputs which change during conversion can introduce noise.

### **CONVERT START TIMING - FULL CONTROL** MODE

| Symbol           | Parameter                                      | Min     | Тур     | Max      | Units    |

|------------------|------------------------------------------------|---------|---------|----------|----------|

| t <sub>DSC</sub> | STS Delay from CE                              | _       | 80      | 200      | ns       |

| t <sub>HEC</sub> | CE Pulse Width                                 | 50      | 40      | -        | ns       |

| tssc             | CS to CE Setup                                 | 50      | 20      | -        | ns       |

| tHSC             | ੋਂ Low During CE High                          | 50      | 25      | -        | ns       |

| t <sub>SRC</sub> | R/C to CE Setup                                | 50      | 0       | -        | ns       |

| tHRC             | R/C Low During CE<br>High                      | 50      | 25      | -        | ns       |

| tsac             | Ao CE Setup                                    | 0       | 0       | -        | пѕ       |

| tHAC             | Ao Valid During CE<br>High                     | 50      | 30      | -        | ns       |

| tc               | Conversion Time<br>8-Bit Cycle<br>12-Bit Cycle | 6<br>12 | 9<br>16 | 15<br>20 | μs<br>μs |

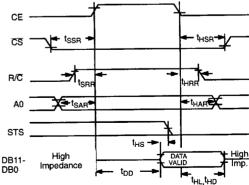

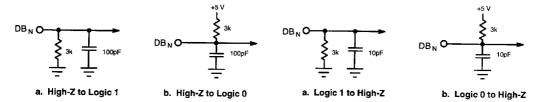

Figure 6. shows the timing for data read operations. The MP574A features fast access times and short data latency times. This simplifies the interface to faster microprocessors. During data read operations, access time is measured from the point where CE and R/C both are high (assuming CS is already low).

Figure 5. Convert Start Timing

Figure 6. Read Cycle Timing

### **READ TIMING - FULL CONTROL MODE**

| Symbol            | Parameter               | Min | Тур | Max | Units |

|-------------------|-------------------------|-----|-----|-----|-------|

| t <sub>DD</sub> 1 | Access Time (from CE)   | _   | 80  | 150 | ns    |

| t <sub>HD</sub>   | Data Valid after CE Low | 25  | 35  | l – | ns    |

| t <sub>HL</sub> 2 | Output Float Delay      | ] - | 60  | 150 | ns    |

| tssa              | CS to CE Setup          | 50  | 0   | -   | пѕ    |

| tsrr              | R/C to CE Setup         | 0   | 0   |     | ns    |

| tSAR              | A0 to CE Setup          | 50  | 25  | -   | ns    |

| t <sub>HSR</sub>  | CS Valid After CE Low   | 0   | 0   | _   | ns    |

| tHRR              | R/C High After CE Low   | 0   | 0   | _   | ns    |

| thar              | A0 Valid After CE Low   | 50  | 25  | _   | ns    |

- 1. t<sub>DD</sub> is measured with the load circuit of Figure 7. and defined as the time required for an output to cross 0.4 V or 2.4 V.

- t<sub>HL</sub> is defined as the time required for the data lines to change 0.5 V when loaded with the circuit of Figure 8.

Figure 7. Load Circuit for Access Time Test

Figure 8. Load Circuit for Output Float Delay Test

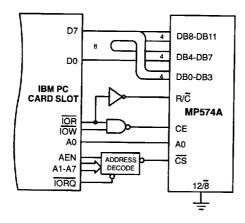

### **IBM PC - MP574A INTERFACE**

### **MP574A**

### "STAND-ALONE" OPERATION

The MP574A can be used in a "stand-alone" mode, which is useful in systems not requiring full computer bus interface capability.

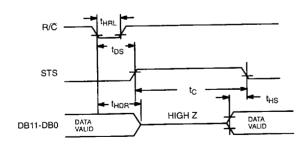

In this mode, CE and 12/8 are wired high, CS and A0 are wired low, and conversion is controlled by R/C. The three-state buffers are enabled when R/C is high and a conversion starts when R/C goes low. This gives rise to two possible control signals - a high pulse or a low pulse. Operation with a low pulse is shown in Figure 9. In this case, the outputs are forced into the high impedance state in response to the falling edge of R/C and return to valid logic levels after the conversion cycle is completed. The STS line goes high 300 ns after R/C goes low and returns low 300 ns after data is valid.

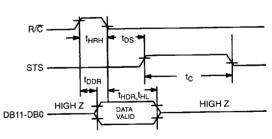

If conversion is initiated by a high pulse as shown in Figure 10., the data lines are enabled during the time when R/C is high. The falling edge of R/C starts the next conversion and the data lines return to tri-state (and remain three-state) until the next high pulse of R/C.

### CONDITIONING OF INPUT SIGNALS

It is important that the signal being applied to the MP574A input not change during a conversion cycle (it should be stable to within 1/2 LSB). During the successive approximation process (12 iterations), the output of the internal DAC cycles at approximately 600 kHz, until a final value is reached. Since the DAC output is tied to the device inputs (see Block Diagram), the input buffer should have low impedance at 600 kHz.

### STAND-ALONE MODE TIMING

| Symbol           | Parameter                                 | Min | Тур      | Max  | Units    |

|------------------|-------------------------------------------|-----|----------|------|----------|

| t <sub>HRL</sub> | Low R/C Pulse Width<br>STS Delay from R/C | 50  | 30<br>60 | 200  | ns<br>ns |

| t <sub>DS</sub>  | Data Valid After R/C                      | 20  | 25       | _    | ns       |

| t <sub>HL</sub>  | Output Float Delay                        | _   | 100      | 150  | ns       |

| t <sub>HS</sub>  | STS Delay After Data<br>Valid             | 300 | -        | 1000 | ns       |

| t <sub>HRH</sub> | High R/C Pulse Width                      | 150 | 50       | -    | ns       |

| toon             | Data Access Time                          | - ' | 90       | 150  | ns       |

Figure 9. Low Pulse for R/C -**Outputs Enabled After Conversion**

Figure 10. High Pulse for R/C -Outputs Enabled While R/C High, Otherwise High-Z