## 512Kx8 PLASTIC SRAM

### PLASTIC PLUS® FEATURES

- Access Times of 15, 20, 25ns

- Standard Commercial Off-The-Shelf (COTS) Memory Devices for Extended Temperature Range

- JEDEC Standard 36 pin Plastic SOJ Package

- Electrical and Speed Characteristics for:

- Military Temperature (-55°C to +125°C)

- Industrial Temperature (-40°C to +85°C)

- Burn-in and Temperature Cycling Available

- Organized as 512K x 8

- Center Power/Ground Pins (Revolutionary)

- 5 Volt Power Supply

- Low Power ("L") Version Available

- Battery Back-Up Operation

- \* This product is subject to change without notice.

### **PIN CONFIGURATION FOR WPS512K8X-XRJX**

| Top View                                                                   |                                                                                  |  |

|----------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|

| <b>Top View</b> 1   2   3   4   5   6   7   8   9   10   11   12   13   14 | 36<br>35<br>34<br>33<br>32<br>31<br>30<br>29<br>28<br>27<br>26<br>25<br>24<br>23 |  |

| 15<br>16<br>17<br>18                                                       | 22<br>21<br>20<br>19                                                             |  |

### **PIN DESCRIPTION**

| A0-18    | Address Inputs    |  |  |  |

|----------|-------------------|--|--|--|

| I/0A0-19 | Data Input/Output |  |  |  |

| WE#      | Chip Select       |  |  |  |

| CS#      | Output Enable     |  |  |  |

| OE#      | Write Enable      |  |  |  |

| Vcc      | +5.0V Power       |  |  |  |

| Vss      | Ground            |  |  |  |

| NC       | Not Connected     |  |  |  |

White Electronic Designs

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                      | Symbol | Min  | Мах                   | Unit |

|--------------------------------|--------|------|-----------------------|------|

| Operating Temperature (Mil.)   | TA     | -55  | +125                  | °C   |

| Operating Temperature (Ind.)   | TA     | -40  | +85                   | °C   |

| Storage Temperature            | Tstg   | -65  | +150                  | °C   |

| Signal Voltage Relative to Vss | VG     | -0.5 | V <sub>CC</sub> + 0.5 | V    |

| Supply Voltage                 | Vcc    | -0.5 | 7.0                   | V    |

#### NOTES:

- Minimum DC voltage is -0.5V on input/output pins. During transitions, this level may undershoot to -2.0V for periods <20ns. Maximum DC voltage on input/output pins is Vcc + 0.5V which, during transitions, may overshoot to Vcc + 2.0V for periods <20ns.</li>

- Minimum DC input voltage on pins A9, OE#, and RESET is -0.5V. During voltage transitions, A9, OE#, and RESET may undershoot Vss to -2.0V for periods of up to 20ns. See Figure 6. Maximum DC input voltage on pin A9 is +12.5V which may overshoot to +13.5V for periods up to 20ns.

- Output shorted for no more than one second. No more than one output shorted at a time.

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a Stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **RECOMMENDED OPERATING CONDITIONS**

| Parameter              | Symbol | Min  | Мах                   | Unit |

|------------------------|--------|------|-----------------------|------|

| Supply Voltage         | Vcc    | 4.5  | 5.5                   | V    |

| Input High Voltage     | Vih    | 2.2  | V <sub>CC</sub> + 0.5 | V    |

| Input Low Voltage      | VIL    | -0.3 | +0.8                  | V    |

| Operating Temp. (Mil.) | TA     | -55  | +125                  | °C   |

| Operating Temp. (Ind.) | TA     | -40  | +85                   | °C   |

### CAPACITANCE

TA = +25°C

| Parameter          | Symbol | Conditions                        | Мах | Unit |

|--------------------|--------|-----------------------------------|-----|------|

| Input capacitance  | CIN    | VIN = 0V, f = 1.0 MHz             | 6   | рF   |

| Output capacitance | Соит   | V <sub>IN</sub> = 0V, f = 1.0 MHz | 8   | pF   |

This parameter is guaranteed by design but not tested.

#### **TRUTH TABLE**

| CS | WE# | OE# | Mode        | I/O Pin | VCC Current     |

|----|-----|-----|-------------|---------|-----------------|

| Н  | Х   | Х   | Power Down  | High-Z  | I <sub>SB</sub> |

| L  | Н   | Н   | Out Disable | High-Z  | lcc             |

| L  | Н   | L   | Read        | Dout    | lcc             |

| L  | L   | Х   | Write       | DIN     | lcc             |

### **DC CHARACTERISTICS**

Vcc = 5.0V, Vss = 0V, TA = -55 +125°C

| Parameter                  | Symbol | Conditions                                                        | Min | Мах | Unit |

|----------------------------|--------|-------------------------------------------------------------------|-----|-----|------|

| Input Leakage Current      | lu     | Vcc = 5.5, VIN = Vss to Vcc                                       |     | 10  | μA   |

| Output Leakage Current     | ILO    | CS = VIH, OE = VIH, VOUT = VSS to VCC                             |     | 10  | μA   |

| Vcc Read Current (1, 2)    | lcc    | CS = V <sub>IL</sub> , OE = V <sub>IH</sub> , f = 5MHz, Vcc = 5.5 |     | 180 | mA   |

| Vcc Standby Current (2, 5) | IBS    | CS = V <sub>IH</sub> , OE = V <sub>IH</sub> , f = 5MHz, Vcc = 5.5 |     | 15  | μA   |

| Output Low Voltage         | Vol    | Iol = 8.0MA, Vcc = 4.5                                            |     | 0.4 | V    |

| Output High Voltage        | Vон    | Іон = -4.0мА, Vcc = 4.5                                           | 2.4 |     | V    |

NOTES: DC test conditions: VIL = 0.3V, VIH = Vcc -0.3V

### Data Retention Characteristics (WPS512K8L-XRJX Only)

$(TA = -55^{\circ}C TO + 125^{\circ}C)$

| Parameter                     | Symbol | Conditions                            | Min | Тур | Мах | Unit |

|-------------------------------|--------|---------------------------------------|-----|-----|-----|------|

| Data Retention Supply Voltage | lu     | Vcc = 5.5, VIN = Vss to Vcc           | 2.0 |     | 5.5 | V    |

| Low Power Data Retention      | Ilo    | CS = VIH, OE = VIH, VOUT = VSS to VCC |     | 300 | 800 | μA   |

# White Electronic Designs \_

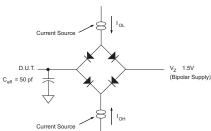

### **AC CHARACTERISTICS**

(V<sub>CC</sub> = 5.0V, V<sub>SS</sub> = 0V, TA = -55°C TO +125°C)

| Parameter                          | Symbol            | -1  | 5+  | -:  | 20  | -:  | 25  | Unit |

|------------------------------------|-------------------|-----|-----|-----|-----|-----|-----|------|

|                                    |                   | Min | Max | Min | Max | Min | Max |      |

| Read Cycle Time                    | trc               | 15  |     | 20  |     | 25  |     | ns   |

| Address Access Time                | taa               |     | 15  |     | 20  |     | 25  | ns   |

| Output Hold from Address Change    | toн               | 0   |     | 0   |     | 0   |     | ns   |

| Chip Select Access Time            | tacs              |     | 15  |     | 20  |     | 25  | ns   |

| Output Enable to Output Valid      | toe               |     | 8   |     | 10  |     | 12  | ns   |

| Chip Select to Output in Low Z     | tcLZ <sup>1</sup> | 3   |     | 3   |     | 3   |     | ns   |

| Output Enable to Output in Low Z   | toLZ <sup>1</sup> | 0   |     | 0   |     | 0   |     | ns   |

| Chip Disable to Output in High Z   | tcHz <sup>1</sup> |     | 7   |     | 8   |     | 10  | ns   |

| Output Disable to Output in High Z | tонz <sup>1</sup> |     | 7   |     | 8   |     | 10  | ns   |

\* 15ns bit available in the lower power option

NOTES:

1. This parameter is guaranteed by design but not tested

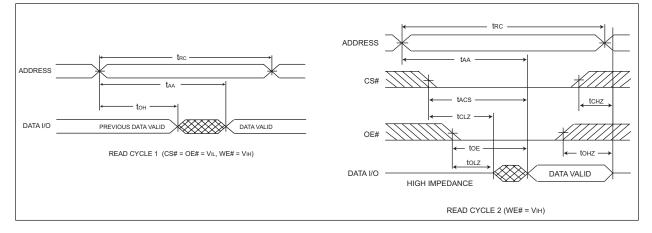

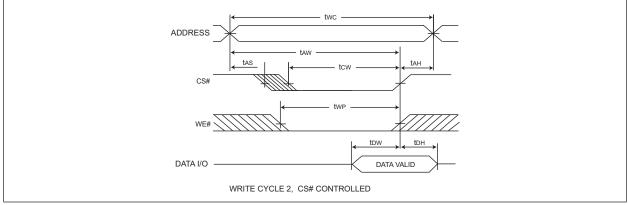

### **AC CHARACTERISTICS**

$V_{CC} = 5.0V$ , GND = 0V, -55°C  $\leq T_A \leq +125$ °C

| Parameter                        | Symbol            | -1  | 5⁺  | -2  | 20  | -2  | 25  | Unit |

|----------------------------------|-------------------|-----|-----|-----|-----|-----|-----|------|

|                                  |                   | Min | Max | Min | Max | Min | Max |      |

| Write Cycle Time                 | twc               | 15  |     | 20  |     | 25  |     | ns   |

| Chip Select to End of Write      | tcw               | 12  |     | 12  |     | 15  |     | ns   |

| Address Valid to End of Write    | taw               | 12  |     | 12  |     | 15  |     | ns   |

| Data Valid to End of Write       | tow               | 8   |     | 9   |     | 10  |     | ns   |

| Write Pulse Width                | twp               | 12  |     | 13  |     | 15  |     | ns   |

| Address Setup Time               | tas               | 0   |     | 0   |     | 0   |     | ns   |

| Address Hold Time                | tан               | 0   |     | 0   |     | 0   |     | ns   |

| Output Active from End of Write  | tow <sup>1</sup>  | 0   |     | 0   |     | 0   |     | ns   |

| Write Enable to Output in High Z | twHz <sup>1</sup> |     | 8   |     | 8   |     | 10  | ns   |

| Data Hold Time                   | tон               | 0   |     | 0   |     | 0   |     | ns   |

\* 15ns bit available in the lower power option

NOTES:

1. This parameter is guaranteed by design but not tested

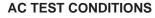

### AC TEST CONDITIONS

| Parameter                        | Тур                | Unit |

|----------------------------------|--------------------|------|

| Input Pulse Levels               | VIL = 0, VIH = 3.0 | V    |

| Input Rise and Fall              | 5                  | ns   |

| Input and Output Reference Level | 1.5                | V    |

| Output Timing Reference Level    | 1.5                | V    |

Notes:

VZ is programmable from -2V to +7V.

IOL & IOH programmable from 0 to 16mA.

Tester Impedance Z0 = 75  $\Omega$ .

VZ is typically the midpoint of VOH and VOL.

IOL & IOH are adjusted to simulate a typical resistive load circuit.

ATE tester includes jig capacitance.

### **TIMING WAVEFORM - READ CYCLE**

### WRITE CYCLE - WE# CONTROLLED

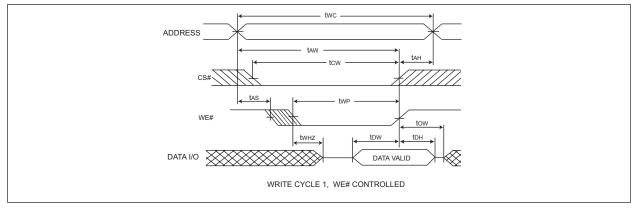

### WRITE CYCLE - CS# CONTROLLED

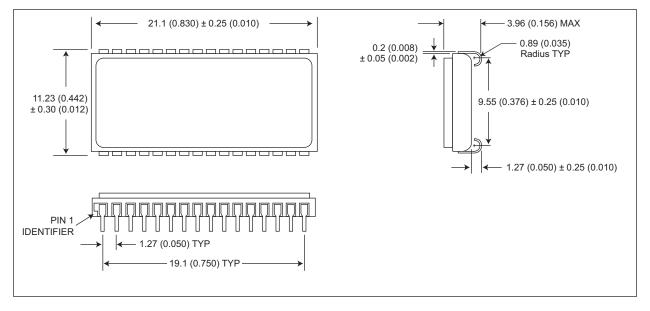

# WHITE ELECTRONIC DESIGNS

### PACKAGE 101: 32 LEAD, CERAMIC SOJ

### **ORDERING INFORMATION**

| SRAM                                                                                             |  |

|--------------------------------------------------------------------------------------------------|--|

| ORGANIZATION, 512K x 8                                                                           |  |

| Blank = Standard Power                                                                           |  |

| L = Low Power                                                                                    |  |

| IMPROVEMENT MARK:<br>B = Burn-in<br>T = Temperature Cycling<br>C = Burn-in and Temperature Cycle |  |

| ACCESS TIME (ns):                                                                                |  |

| PACKAGE:<br>RJ = Revolutionary                                                                   |  |

| DEVICE GRADE:M = Military Temperature-55°C to +125°CI = Industrial Temperature-40°C to +85°C     |  |