# 512Kx8 Plastic Monolithic SRAM CMOS

# FEATURES

- 512Kx8 bit CMOS Static

- Random Access Memory

- Access Times of 17, 20, 25ns

- Data Retention Function (LPA version)

- Extended Temperature Testing

- Data Retention Functionality Testing

- 36 lead JEDEC Approved Revolutionary Pinout

- Plastic SOJ (Package 319)

- Single +5V (±10%) Supply Operation

- RoHS compliant

WEDC's ruggedized plastic 512Kx8 SRAM that allows the user to capitalize on the cost advantage of using a plastic component while not sacrificing all of the reliability available in a full military device.

Extended temperature testing is performed with the test patterns developed for use on WEDC's fully compliant 512Kx8 SRAMs. WEDC fully characterizes devices to determine the proper test patterns for testing at temperature extremes. This is critical because the operating characteristics of device change when it is operated beyond the commercial guarantee a device that operates reliably in the field at temperature extremes. Users of WEDC's ruggedized plastic benefit from WEDC's extensive experience in characterizing SRAMs for use in military systems.

WEDC ensures Low Power devices will retain data in Data Retention mode by characterizing the devices to determine the appropriate test conditions. This is crucial for systems operating at -40°C or below and using dense memories such as 512Kx8s.

WEDC's ruggedized plastic SOJ is footprint compatible with WEDC's full military ceramic 36 pin SOJ.

## **FIGURE 1 – PIN CONFIGURATION**

|                                                                                                                      | TOP VIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                      |                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| A0<br>A1<br>A2<br>A3<br>A4<br>CS#<br>I/O0<br>I/O1<br>Vcc<br>Vss<br>I/O2<br>I/O3<br>WE#<br>A5<br>A6<br>A7<br>A8<br>A9 | 1 C<br>2 C<br>3 C<br>4 C<br>5 C<br>6 C<br>7 C<br>8 C<br>9 C<br>10 C<br>11 C<br>12 C<br>13 C<br>14 C<br>13 C<br>14 C<br>15 C<br>16 C<br>17 C<br>18 | 36   35   34   33   32   31   30   29   26   25   24   23   21   20   121   120   19 | NC<br>A18<br>A17<br>A16<br>A15<br>OE#<br>I/O7<br>I/O6<br>Vss<br>Vcc<br>I/O5<br>I/O4<br>A14<br>A13<br>A12<br>A11<br>A10<br>NC |

Microsemi Corporation reserves the right to change products or specifications without notice.

#### PIN Description

| I/O0-7 | Data Inputs/Outputs |

|--------|---------------------|

| A0-18  | Address Inputs      |

| WE#    | Write Enables       |

| CS#    | Chip Selects        |

| OE#    | Output Enable       |

| Vcc    | Power (+5V ±10%)    |

| Vss    | Ground              |

| NC     | Not Connected       |

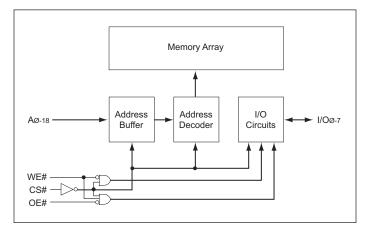

#### **BLOCK DIAGRAM**

Power

Icc2, Icc3

lcc1

lcc1

lcc1

Unit

V

V

V

V

Max

5.5

0

Vcc + 0.5

+0.8

Output

High Z

High Z

Data Out

Data In

Тур

5.0

0

\_

\_

**TRUTH TABLE**

**RECOMMENDED OPERATING CONDITIONS**

Min

4.5

0

2.0

-0.5

Mode

Standby

Output Deselect

Read

Write

Symbol

Vcc

Vss

VIH

VIL

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                          |             | Unit |

|------------------------------------|-------------|------|

| Voltage on any pin relative to Vss | -0.5 to 7.0 | V    |

| Operating Temperature TA (Ambient) |             |      |

| Commercial                         | 0 to +70    | °C   |

| Industrial                         | -40 to +85  | °C   |

| Military                           | -55 to +125 | °C   |

| Storage Temperature, Plastic       | -65 to +150 | °C   |

| Power Dissipation                  | 1.5         | W    |

| Output Current                     | 20          | mA   |

| Junction Temperature, TJ           | 175         | °C   |

NOTE:

Stress greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions greater than those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## CAPACITANCE

#### TA = +25°C

| Parameter     | Symbol | Condition                    | Max | Unit |

|---------------|--------|------------------------------|-----|------|

| Address Lines | CI     | VIN = Vcc or Vss, f = 1.0MHz | 8   | pF   |

| Data Lines    | CO     | VIN = Vcc or Vss, f = 1.0MHz | 8   | рF   |

These parameters are sampled, not 100% tested.

#### DC CHARACTERISTICS

OE#

Х

Н

L

Х

Parameter

Supply Voltage

Supply Voltage

Input High Voltage

Input Low Voltage

CS#

Н

L

L

L

WE#

Х

Н

Н

L

#### $V_{CC}$ = 5V, $V_{SS}$ = 0V, -55°C $\leq$ T<sub>A</sub> $\leq$ +125°C

| Parameter                | Symbol | Conditions                                                                      | Min | Мах | Units |

|--------------------------|--------|---------------------------------------------------------------------------------|-----|-----|-------|

| Input Leakage Current    | lu     | $V_{CC}$ = 5.5, $V_{IN}$ = $V_{SS}$ to $V_{CC}$                                 |     | 10  | μΑ    |

| Output Leakage Current   | ILO    | CS# = VIL, OE# = VIH, VOUT = Vss to Vcc                                         |     | 10  | μΑ    |

| Operating Supply Current | lcc    | CS# = V <sub>IL</sub> , OE# = V <sub>IH</sub> , f = 5MHz, V <sub>CC</sub> = 5.5 |     | 180 | mA    |

| Standby Current          | lsв    | CS# = VIH, OE# = VIH, f = 5MHz, Vcc = 5.5                                       |     | 15  | mA    |

| Output High Volltage     | Vон    | юн = -4.0mA, Vcc = 4.5                                                          | 2.4 |     | V     |

| Output Low Voltage       | Vol    | IoL = 8.0mA, Vcc = 4.5                                                          |     | 0.4 | V     |

NOTE: DC test conditions:  $V_{IL}$  = 0.3V,  $V_{IH}$  =  $V_{CC}$  -0.3V

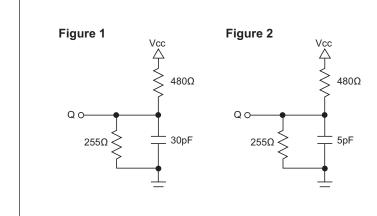

# AC TEST CONDITIONS

| Input Pulse Levels             | Vss to 3.0V |

|--------------------------------|-------------|

| Input Rise and Fall Times      | 5ns         |

| Input and Output Timing Levels | 1.5V        |

| Output Load                    | Figure 1    |

NOTE: For t<sub>EHQZ</sub>, t<sub>GHQZ</sub> and t<sub>WLQZ</sub>, CL = 5pF (Figure 2)

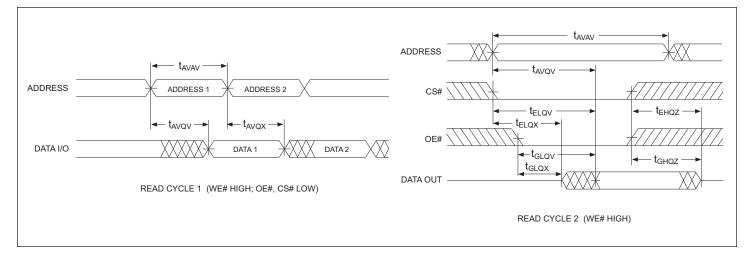

## AC CHARACTERISTICS – READ CYCLE

| Vcc = 5.0V, | $V_{SS} = 0V, 0^{\circ}C \le T_A \le +70^{\circ}C$ |

|-------------|----------------------------------------------------|

|-------------|----------------------------------------------------|

| Parameter                             | Syn<br>JEDEC  | nbol<br>Alt. | 17<br>Min | 'ns<br>Max | 20<br>Min | )ns<br>Max | 25<br>Min | ins<br>Max | Units |

|---------------------------------------|---------------|--------------|-----------|------------|-----------|------------|-----------|------------|-------|

| Read Cycle Time                       | tavav         | trc          | 17        |            | 20        |            | 25        |            | ns    |

| Address Access Time                   | tavqv         | taa          |           | 17         |           | 20         |           | 25         | ns    |

| Chip Enable Access Time               | telqv         | tacs         |           | 17         |           | 20         |           | 25         | ns    |

| Chip Enable to Output in Low Z (1)    | telqx         | tcLz         | 3         |            | 3         |            | 3         |            | ns    |

| Chip Disable to Output in High Z (1)  | <b>t</b> EHQZ | tснz         | 0         | 7          | 0         | 8          | 0         | 10         | ns    |

| Output Hold from Address Change       | tavqx         | tон          | 0         |            | 0         |            | 0         |            | ns    |

| Output Enable to Output Valid         | tglqv         | toe          |           | 8          |           | 10         |           | 12         | ns    |

| Output Enable to Output in Low Z (1)  | tGLQX         | tolz         | 0         |            | 0         |            | 0         |            | ns    |

| Output Disable to Output in High Z(1) | tgнqz         | tонz         | 0         | 7          | 0         | 8          | 0         | 10         | ns    |

1. This parameter is guaranteed by design but not tested.

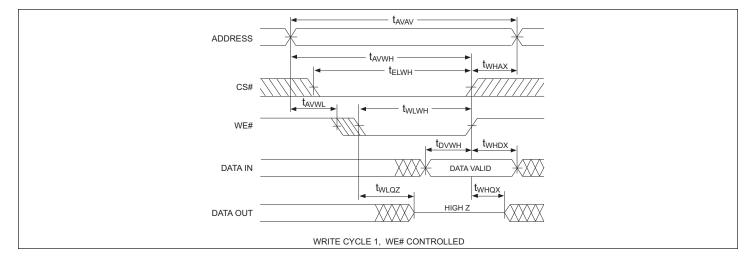

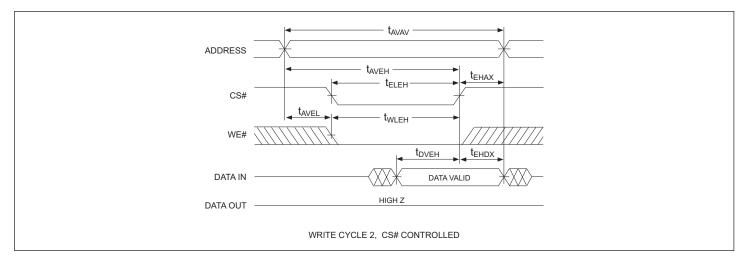

## AC CHARACTERISTICS – WRITE CYCLE

|                                     | Syn            | nbol       |          | 7ns |          | ns  |          | ns  |          |

|-------------------------------------|----------------|------------|----------|-----|----------|-----|----------|-----|----------|

| Parameter                           | JEDEC          | Alt.       | Min      | Max | Min      | Max | Min      | Max | Units    |

| Write Cycle Time                    | tavav          | twc        | 17       |     | 20       |     | 25       |     | ns       |

| Chip Enable to End of Write         | tегмн<br>tеген | tcw<br>tcw | 14<br>14 |     | 15<br>15 |     | 17<br>17 |     | ns<br>ns |

| Address Setup Time                  | tavwl<br>tavel | tas<br>tas | 0<br>0   |     | 0<br>0   |     | 0<br>0   |     | ns<br>ns |

| Address Valid to End of Write       | tavwн<br>taveн | taw<br>taw | 14<br>14 |     | 15<br>15 |     | 17<br>17 |     | ns<br>ns |

| Write Pulse Width                   | twlwн<br>twleн | twp<br>twp | 14<br>14 |     | 15<br>15 |     | 17<br>17 |     | ns<br>ns |

| Write Recovery Time                 | twнах<br>teнах | twr<br>twr | 0<br>0   |     | 0<br>0   |     | 0<br>0   |     | ns<br>ns |

| Data Hold Time                      | twнdx<br>teнdx | tон<br>tон | 0<br>0   |     | 0<br>0   |     | 0<br>0   |     | ns<br>ns |

| Write to Output in High Z (1)       | twLqz          | twнz       | 0        | 8   | 0        | 8   | 0        | 10  | ns       |

| Data to Write Time                  | tovwн<br>toveн | tow<br>tow | 8<br>8   |     | 10<br>10 |     | 12<br>12 |     | ns<br>ns |

| Output Active from End of Write (1) | twнqx          | twLz       | 0        |     | 0        |     | 0        |     | ns       |

$V_{CC}$  = 5.0V,  $V_{SS}$  = 0V, 0°C  $\leq$  TA  $\leq$  +70°C

1. This parameter is guaranteed by design but not tested.

## FIGURE 2 – TIMING WAVEFORM — READ CYCLE

FIGURE 3 – WRITE CYCLE — WE# CONTROLLED

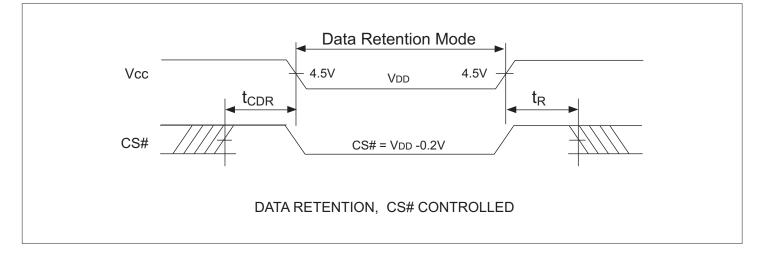

#### DATA RETENTION CHARACTERISTICS (EDI88512LPA ONLY)

$-55^\circ C \leq T_A \leq +125^\circ C$

| Characteristic<br>Low Power Version only                       | Sym                                | Conditions                                            | Min        | Тур | Мах     | Units    |

|----------------------------------------------------------------|------------------------------------|-------------------------------------------------------|------------|-----|---------|----------|

| Data Retention Voltage<br>Data Retention Quiescent Current     | Vdd<br>Iccdr                       | V <sub>DD</sub> = 2.0V<br>CS# ≥ V <sub>DD</sub> -0.2V | 2<br>-     | -   | -<br>15 | V<br>mA  |

| Chip Disable to Data Retention Time<br>Operation Recovery Time | T <sub>CDR</sub><br>T <sub>R</sub> | $V_{IN} \ge V_{DD} - 0.2V$<br>or $V_{IN} \le 0.2V$    | 0<br>Tavav | -   | -       | ns<br>ns |

#### FIGURE 5 – DATA RETENTION — CS# CONTROLLED

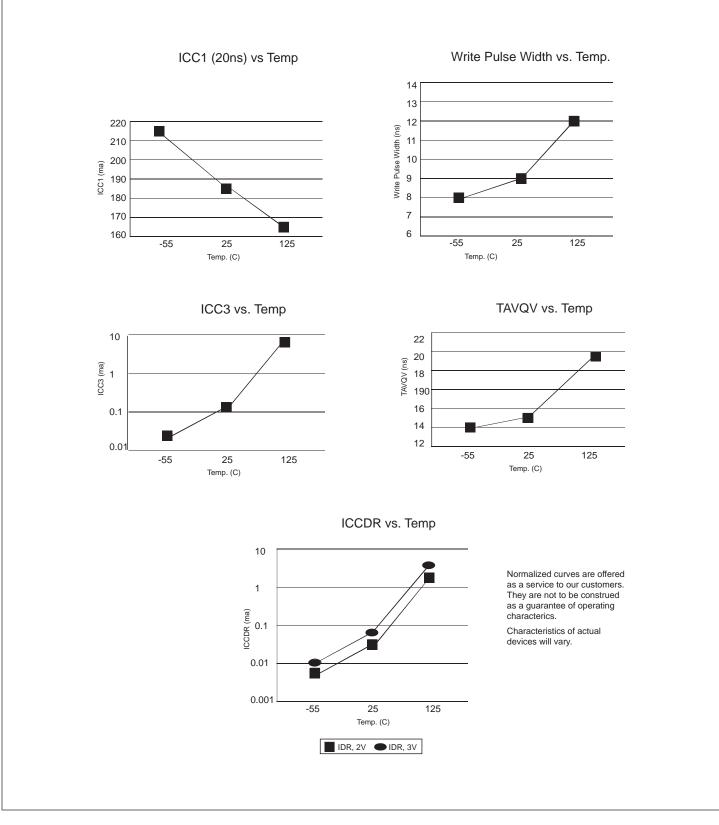

#### FIGURE 6 – NORMALIZED OPERATING GRAPHS

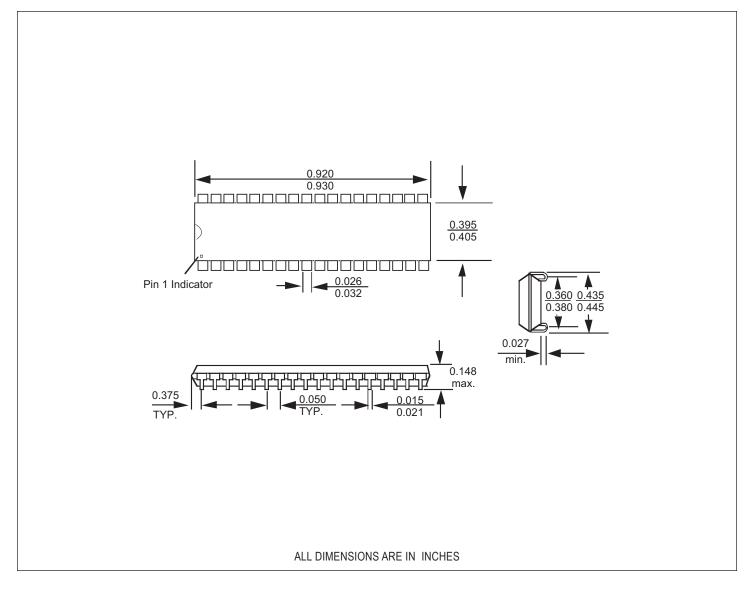

#### PACKAGE 319: 36 LEAD, PLASTIC SMALL OUTLINE J-LEAD (SOJ)

#### **ORDERING INFORMATION**

|                                                                                                                                                                                                                        | EDI 8 8512 CA - X X X G |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|                                                                                                                                                                                                                        |                         |

| SRAM:                                                                                                                                                                                                                  |                         |

| ORGANIZATION, 512Kx8:                                                                                                                                                                                                  |                         |

| TECHNOLOGY:<br>CA = CMOS Standard Power<br>LPA = Low Power                                                                                                                                                             |                         |

| ACCESS TIME (ns):                                                                                                                                                                                                      |                         |

| PACKAGE TYPE:<br>M = 36 lead Plastic SOJ<br>RJ = Relvoutionary                                                                                                                                                         |                         |

| <b>DEVICE GRADE:</b><br>B = MIL-STD-883 Compliant<br>M = Military Screened $-55^{\circ}$ C to $+125^{\circ}$ C<br>I = Industrial $-40^{\circ}$ C to $+85^{\circ}$ C<br>C = Commercial $0^{\circ}$ C to $+70^{\circ}$ C |                         |

| RoHS COMPLIANT:                                                                                                                                                                                                        |                         |

#### **ORDERING INFORMATION**

| PLASTIC PLUS®:                                                                                         |  |  |

|--------------------------------------------------------------------------------------------------------|--|--|

| SRAM:                                                                                                  |  |  |

| ORGANIZATION, 512K x 8:                                                                                |  |  |

| POWER:<br>Blank = Standard Power<br>L = Low Power                                                      |  |  |

| IMPROVEMENT MARK:<br>B = Burn-in<br>T = Temperature Cycling<br>C = Burn-in and Temperature Cycle       |  |  |

| ACCESS TIME (ns):                                                                                      |  |  |

| PACKAGE:<br>RJ = Revolutionary                                                                         |  |  |

| DEVICE GRADE:<br>M = Military Temperature -55°C to +125°C<br>I = Industrial Temperature -40°C to +85°C |  |  |

| RoHS COMPLIANT:                                                                                        |  |  |

Microsemi Corporation reserves the right to change products or specifications without notice.

February 2011 © 2011 Microsemi Corporation. All rights reserved. Rev. 10

# **Document Title**

512K x 8 Plastic Monolithic SRAM CMOS

# **Revision History**

| Rev #  | History                                                                                                                                                   | Release Date  | Status |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------|

| Rev 7  | Added RoHS compliance                                                                                                                                     | November 2008 | Final  |

| Rev 8  | Changes (Pg. 2, 8)<br>8.1 Add solder dipped to package options<br>8.2 Change CI to 8pF<br>8.3 Change V <sub>IH</sub> to 2.0V and V <sub>IL</sub> to -0.5V | February 2009 | Final  |

| Rev 9  | Changes (Pg. 9)<br>9.1 Change document title: 512K x 8 Plastic Monolithic SRAM CMOS                                                                       | March 2009    | Final  |

| Rev 10 | Changes (Pg. 1-9)<br>10.1 Change document layout from White Electronic Designs to Microsemi                                                               | February 2011 | Final  |