# 256K x 36 SSRAM

Flow-Through, Synchronous Burst SRAM

## FEATURES

- Organized 256K x 36

- Fast Clock and OE\ access times

- Single +3.3V + 0.3V/-0.165V power supply (V<sub>DD</sub>)

- SNOOZE MODE for reduced-power standby

- Common data inputs and data outputs

- Individual BYTE WRITE control and GLOBAL WRITE

- Three chip enables for simple depth expansion and address pipelining

- Clock-controlled and registered addresses, data I/Os and control signals

- Internally self-timed WRITE cycle

- Burst control (interleaved or linear burst)

- Automatic power-down for portable applications

- Low capacitive bus loading

- 100-lead TQFP package for high density, high speed

- RoHs compliant options available

## OPTIONS MARKING

| • Timing           |      |

|--------------------|------|

| 7.5ns/8.5ns/117MHz | -7.5 |

| 8.5ns/10ns/100MHz  | -8.5 |

| 10ns/15ns/66MHz    | -10  |

- Packages TQFP DQ No. 1001

- Operating Temperature Ranges Military (-55°C to +125°C) /XT Enhanced (-40°C to +105°C) /ET Industrial (-40°C to +85°C) /IT

### **GENERAL DESCRIPTION**

The AS5SS256K36 employs high-speed, low-power CMOS designs that are fabricated using an advanced CMOS process.

This 8Mb Synchronous Burst SRAM integrates a 256K x 36 SRAM core with advanced synchronous peripheral circuitry and a 2-bit burst counter. All synchronous inputs pass through registers controlled by a positive-edge-triggered single-clock input (CLK). The synchronous inputs include all addresses, all data inputs, active LOW chip enable (CE\), two additional chip enables for easy depth expansion (CE2\, CE2), burst control inputs (ADSC\, ADSP\, ADV\), byte write enables (BWx\) and global write (GW\).

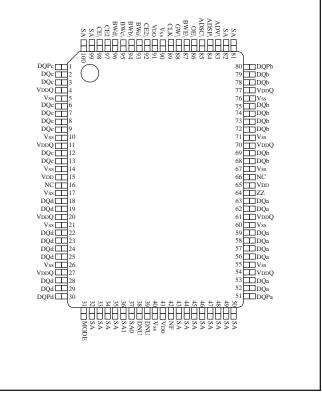

## PIN ASSIGNMENT

(Top View)

### 100-pin TQFP (DQ)

For more products and information please visit our web site at *www.micross.com*

# SSRAM AS5SS256K36

### **GENERAL DESCRIPTION (continued)**

Asynchronous inputs include the output enable (OE\), clock (CLK) and snooze enable (ZZ). There is also a burst mode input (MODE) that selects between interleaved and linear burst modes. The data-out (Q), enabled by OE\, is also asynchronous. WRITE cycles can be from one to four bytes wide as controlled by the write control inputs.

Burst operation can be initiated with either address status processor (ADSP\) or address status controller (ADSC\) inputs. Subsequent burst addresses can be internally generated as controlled by the burst advance input (ADV\).

Address and write control are registered on-chip to

simplify WRITE cycles. This allows self-timed WRITE cycles. Individual byte enables allow individual bytes to be written. During WRITE cycles on the x18 device, BWa\ controls DQa's and DQPa; BWb\ controls DQb's and DQPb; BWc\ controls DQc's and DQPc; BWd\ controls DQd's and DQPd. GW\ LOW causes all bytes to be written. Parity bits are also featured on this device.

This 8Mb Synchronous Burst SRAM operates from a  $+3.3V V_{DD}$  power supply, and all inputs and outputs are TTL-compatible. The device is ideally suited for 486, Pentium<sup>®</sup>, 680x0 and PowerPC<sup>TM</sup> systems and those systems that benefit from a wide synchronous data bus.

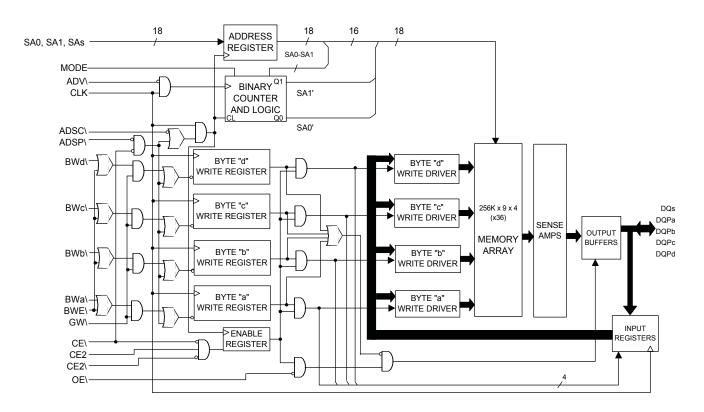

# FUNCTIONAL BLOCK DIAGRAM

**NOTE:** Functional Block Diagrams illustrate simplified device operation. See Truth Table, Pin Descriptions for detailed information.

and time diagrams

# **PIN DESCRIPTION**

| Pin Number                                            | SYMBOL                       | TYPE  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------|------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37<br>36<br>32-35, 44-50,<br>81, 82, 99,<br>100<br>43 | SA0<br>SA1<br>SA             | Input | Synchronous Address Inputs: These inputs are registered and must meet<br>the setup and hold times around the rising edge of CLK. Two different<br>pinouts are available for the TQFP packages.                                                                                                                                                                                                                            |

| 93<br>94<br>95<br>96                                  | BWa\<br>BWb\<br>BWc\<br>BWd\ | Input | Synchronous Byte Write Enables: These active LOW inputs allow individual bytes to be written and must meet the setup and hold times around the rising edge of CLK. A byte write enable is LOW for a WRITE cycle and HIGH for a READ cycle. Bwa\ controls DQa pins and DQPa; Bwb\ controls DQb pins and DQPb; Bwc\ controls DQc pins and DQPc; Bwd\ controls DQd pins and DQPd. Parity bits are featured on this device.   |

| 87                                                    | BWE\                         | Input | Byte Write Enable: This active LOW input permits BYTE WRITE operations and must meet the setup and hold items around the rising edge of CLK.                                                                                                                                                                                                                                                                              |

| 88                                                    | GW\                          | Input | Global Write: This active LOW input allows a full 36-bit WRITE to occur independent of the BWE\ and BWx\ lines and must meet the setup and hold times around the rising edge of CLK.                                                                                                                                                                                                                                      |

| 89                                                    | CLK                          | Input | Clock: CLK registers address, data, chip enable, byte write enables and<br>burst control inputs on its rising edge. All synchronous inputs must meet<br>setup and hold times around the clock's rising edge.                                                                                                                                                                                                              |

| 98                                                    | CE/                          | Input | Synchronous Chip Enable: This active LOW input is used to enable the device and conditions the internal use of ADSP\. CE\ is sampled only when a new external address is loaded.                                                                                                                                                                                                                                          |

| 92                                                    | CE2\                         | Input | Synchronous Chip Enable: This active LOW input is used to enable the device and is sampled only when a new external address is loaded.                                                                                                                                                                                                                                                                                    |

| 97                                                    | CE2                          | Input | Synchronous Chip Enable: This active HIGH input is used to enable the device and is sampled only when a new external address is loaded.                                                                                                                                                                                                                                                                                   |

| 86                                                    | OE\                          | Input | Output Enable: This active LOW, asynchronous input enables the data I/O output drivers.                                                                                                                                                                                                                                                                                                                                   |

| 83                                                    | ADV\                         | Input | Synchronous Address Advance: This active LOW input is used to<br>advance the internal burst counter, controlling burst access after the<br>external address is loaded. A HIGH on this pin effectively causes wait<br>states to be generated (no address advance). To ensure use of correct<br>address during a WRITE cycle, ADV\ must be HIGH at the rising edge of<br>the first clock after an ADSP\ cycle is initiated. |

| 85                                                    | ADSC\                        | Input | Synchronous Address Status Controller: This active LOW input interrupts any ongoing burst, causing a new external address to be registered. A READ or WRITE is performed using the new address if CE\ is LOW. ADSC\ is also used to place the chip into power-down state when CE\ is HIGH.                                                                                                                                |

# **PIN DESCRIPTION (continued)**

| Pin Number                                                                                                                                                         | SYMBOL                                   | TYPE             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 84                                                                                                                                                                 | ASDP\                                    | Input            | Synchronous Address Status Processor: This active LOW inputs interrupts any ongoing burst, causing a new external address to be registered. A READ is performed using the new address, independent of the byte write enables and ADSC but dependent upon CE CE2 and CE2\. ADSP\ is ignored if CE\ is HIGH. Power-down state is entered if CE2 is LOW or CE2\ is HIGH. |

| 31                                                                                                                                                                 | MODE                                     | Input            | MODE: This inputs selects the burst sequence. A LOW on this pin select<br>"linear burst." NC or HIGH on this pin selects "interleaved burst." Do not<br>alter input state while device is operating.                                                                                                                                                                  |

| 64                                                                                                                                                                 | ZZ                                       | Input            | Snooze Enable: This active HIGH, asynchronous input causes the device to enter a low-power standby mode in which all data in the memory array is retained. When ZZ is active, all other inputs are ignored.                                                                                                                                                           |

| <ul> <li>(a) 52, 53, 56-59,<br/>62, 63</li> <li>(b) 68, 69, 72-75,<br/>78, 79</li> <li>(c) 2, 3, 6-9, 12,<br/>13</li> <li>(d) 18, 19, 22-25,<br/>28, 29</li> </ul> | DQa<br>DQb<br>DQc<br>DQd                 | Input/<br>Output | SRAM Data I/O's: Byte "a" is DQa pins; Byte "b" is DQb pins; Byte "c" is DQc pins; Byte "d" is DQd pins. Input data must meet setup and hold times around the rising edge of CLK.                                                                                                                                                                                     |

| 51<br>80<br>1<br>30                                                                                                                                                | NC/DQPa<br>NC/DQPb<br>NC/DQPc<br>NC/DQPd | NC/ I/O          | Parity Data I/Os: Byte "a" parity is DQPa; Byte "b" parity is DQPb; Byte<br>"c" parity is DQPc; Byte "d" parity is DQPd.                                                                                                                                                                                                                                              |

| 15, 41, 65, 91                                                                                                                                                     | V <sub>DD</sub>                          | Supply           | Power Supply: See DC Electrical Characteristics and Operating<br>Conditions for range.                                                                                                                                                                                                                                                                                |

| 4, 11, 20, 27, 54,<br>61, 70, 77                                                                                                                                   | $V_{DD}Q$                                | Supply           | Isolated Output Buffer Supply: See DC Electrical Characteristics and<br>Operating Conditions for range.                                                                                                                                                                                                                                                               |

| 5, 10, 14, 17, 21,<br>26, 40, 55, 60, 67,<br>71, 76, 90                                                                                                            | Vss                                      | Supply           |                                                                                                                                                                                                                                                                                                                                                                       |

| 38, 39                                                                                                                                                             | DNU                                      |                  | Do Not Use: These signals may either be unconnected or wired to GND to improve package heat dissipation.                                                                                                                                                                                                                                                              |

| 16, 66                                                                                                                                                             | NC                                       |                  | No Connect: These signals are not internally connected and may be connected to GND to improve package heat dissipation.                                                                                                                                                                                                                                               |

| 42                                                                                                                                                                 | NF                                       |                  | No Function: These pins are internally connected to the die and have the capacitance of an input pin. It is allowable to leave these pins unconnected or driven by signals. Pin 42 is reserved as an address upgrade pin for the 16Mb Synchronous Burst.                                                                                                              |

## INTERLEAVED BURST ADDRESS TABLE (MODE = NC OR HIGH)

| FIRST ADDRESS (EXTERNAL) | SECOND ADDRESS (INTERNAL) | THIRD ADDRESS (INTERNAL) | FOURTH ADDRESS (INTERNAL) |

|--------------------------|---------------------------|--------------------------|---------------------------|

| XX00                     | XX01                      | XX10                     | XX11                      |

| XX01                     | XX00                      | XX11                     | XX10                      |

| XX10                     | XX11                      | XX00                     | XX01                      |

| XX11                     | XX10                      | XX01                     | XX00                      |

## LINEAR BURST ADDRESS TABLE (MODE = LOW)

| FIRST ADDRESS (EXTERNAL) | SECOND ADDRESS (INTERNAL) | THIRD ADDRESS (INTERNAL) | FOURTH ADDRESS (INTERNAL) |

|--------------------------|---------------------------|--------------------------|---------------------------|

| XX00                     | XX01                      | XX10                     | XX11                      |

| XX01                     | XX10                      | XX11                     | XX00                      |

| XX10                     | XX11                      | XX00                     | XX01                      |

| XX11                     | XX00                      | XX01                     | XX10                      |

### PARTIAL TRUTH TABLE FOR WRITE COMMANDS

| FUNCTION        | GW\ | BWE\ | BWa\ | BWb\ | BWc\ | BWd\ |

|-----------------|-----|------|------|------|------|------|

| READ            | Н   | Н    | Х    | Х    | Х    | Х    |

| READ            | Н   | L    | Н    | Н    | Н    | Н    |

| WRITE Byte "a"  | Н   | L    | L    | Н    | Н    | Н    |

| WRITE All Bytes | Н   | L    | L    | L    | L    | L    |

| WRITE All Bytes | L   | Х    | Х    | Х    | Х    | Х    |

transforming specialty electronics

# **TRUTH TABLE**

| OPERATION                    | ADDRESS<br>USED | CE\ | CE2\ | CE2 | zz | ADSP\ | ADSC\ | ADV\ | WRITE\ | OE\ | CLK | DQ     |

|------------------------------|-----------------|-----|------|-----|----|-------|-------|------|--------|-----|-----|--------|

| Deselected Cycle, Power-Down | None            | Н   | Х    | Х   | L  | Х     | L     | Х    | Х      | Х   | L-H | High-Z |

| Deselected Cycle, Power-Down | None            | L   | Х    | L   | L  | L     | Х     | Х    | Х      | Х   | L-H | High-Z |

| Deselected Cycle, Power-Down | None            | L   | Н    | Х   | L  | L     | Х     | Х    | Х      | Х   | L-H | High-Z |

| Deselected Cycle, Power-Down | None            | L   | Х    | L   | L  | Н     | L     | Х    | Х      | Х   | L-H | High-Z |

| Deselected Cycle, Power-Down | None            | L   | Н    | Х   | L  | Н     | L     | Х    | Х      | Х   | L-H | High-Z |

| SNOOZE MODE, Power-Down      | None            | Х   | Х    | Х   | Н  | Х     | Х     | Х    | Х      | Х   | Х   | High-Z |

| READ Cycle, Begin Burst      | External        | L   | L    | Н   | L  | L     | Х     | Х    | Х      | L   | L-H | Q      |

| READ Cycle, Begin Burst      | External        | L   | L    | Н   | L  | L     | Х     | Х    | Х      | Н   | L-H | High-Z |

| WRITE Cycle, Begin Burst     | External        | L   | L    | Н   | L  | Н     | L     | Х    | L      | Х   | L-H | D      |

| READ Cycle, Begin Burst      | External        | L   | L    | Н   | L  | Н     | L     | Х    | Н      | L   | L-H | Q      |

| READ Cycle, Begin Burst      | External        | L   | L    | Н   | L  | Н     | L     | Х    | Н      | Н   | L-H | High-Z |

| READ Cycle, Continue Burst   | Next            | Х   | Х    | Х   | L  | Н     | Н     | L    | Н      | L   | L-H | Q      |

| READ Cycle, Continue Burst   | Next            | Х   | Х    | Х   | L  | Н     | Н     | L    | Н      | Н   | L-H | High-Z |

| READ Cycle, Continue Burst   | Next            | Н   | Х    | Х   | L  | Х     | Н     | L    | Н      | L   | L-H | Q      |

| READ Cycle, Continue Burst   | Next            | Н   | Х    | Х   | L  | Х     | Н     | L    | Н      | Н   | L-H | High-Z |

| WRITE Cycle, Continue Burst  | Next            | Х   | Х    | Х   | L  | Н     | Н     | L    | L      | Х   | L-H | D      |

| WRITE Cycle, Continue Burst  | Next            | Н   | Х    | Х   | L  | Х     | Н     | L    | L      | Х   | L-H | D      |

| READ Cycle, Suspend Burst    | Current         | Х   | Х    | Х   | L  | Н     | Н     | Н    | Н      | L   | L-H | Q      |

| READ Cycle, Suspend Burst    | Current         | Х   | Х    | Х   | L  | Н     | Н     | Н    | Н      | Н   | L-H | High-Z |

| READ Cycle, Suspend Burst    | Current         | Н   | Х    | Х   | L  | Х     | Н     | Н    | Н      | L   | L-H | Q      |

| READ Cycle, Suspend Burst    | Current         | Н   | Х    | Х   | L  | Х     | Н     | Н    | Н      | Н   | L-H | High-Z |

| WRITE Cycle, Suspend Burst   | Current         | Х   | Х    | Х   | L  | Н     | Н     | Н    | L      | Х   | L-H | D      |

| WRITE Cycle, Suspend Burst   | Current         | Н   | Х    | Х   | L  | Х     | Н     | Н    | L      | Х   | L-H | D      |

### NOTE:

- 1. X means "Don't Care." \ means active LOW. H Means logic HIGH. L means logic LOW.

- 2. For WRITE\, L means any one or more byte write enable signals (BWa\, BWb\, BWc\, or BWd\) and BWE\ are LOW or GW\ is LOW. WRITE\ = H for all BWx\, BWE\, GW\ HIGH.

- 3. BWa\ enables WRITEs to DQa pins, DQPa. BWb\ enables WRITEs to DQb pins, DQPb. BWc\ enables WRITEs to DQc pins, DQPc. BWd\ enables WRITEs to DQd pins, DQPd.

- 4. All inputs except OE\ and ZZ must meet setup and hold times around the rising edge (LOW to HIGH) of CLK.

- 5. Wait states are inserted by suspending burst.

- 6. For a WRITE operation following a READ operation, OE\ must be HIGH before the input data setup time and held HIGH throughout the input data hold time.

- 7. This device contains circuitry that will ensure the outputs will be High-Z during power-up.

- 8. ADSP\ LOW always initiates an internal READ at the L-H edge of CLK. A WRITE is performed by setting one or more byte write enable signals and BWE\ LOW or GW\ LOW for the subsequent L-H edge of CLK. Refer to WRITE timing diagram for clarification.

# SSRAM AS5SS256K36

### **ABSOLUTE MAXIMUM RATINGS\***

| Storage Temperature (Plastics)         | 55°C to +150°C          |

|----------------------------------------|-------------------------|

| Storage Temperature (Ceramics)         | 55°C to +125°C          |

| Short Circuit Output Current (per I/O) | 100mA                   |

| Voltage on any Pin Relative to Vss     | 0.5V to +4.6 V          |

| Max Junction Temperature**             | +150°C                  |

| V <sub>IN</sub> (DQx)                  | 0.5V to $V_{DD}Q$ +0.5V |

| V <sub>IN</sub> (inputs)               | 0.5V to $V_{DD}$ +0.5V  |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

\*\* Junction temperature depends upon package type, cycle time, loading, ambient temperature and airflow, and humidity.

## 3.3V I/O DC ELECTRICAL CHARACTERISTICS AND OPERATING CONDITIONS

(-55°C to +125°C, -40°C to +105°C or -40°C to +85°C;  $V_{DD}$ ,  $V_{DD}Q = +3.3V + 0.3V/-0.165V$  unless otherwise noted)

| PARAMETER                     | CONDITION                                       | SYMBOL            | MIN   | MAX                  | UNITS | NOTES |

|-------------------------------|-------------------------------------------------|-------------------|-------|----------------------|-------|-------|

| Input High (Logic 1) Voltage  |                                                 | V <sub>IH</sub>   | 2.2   | V <sub>CC</sub> +0.3 | V     | 1, 2  |

| Input Low (Logic 0) Voltage   |                                                 | V <sub>IL</sub>   | -0.3  | 0.8                  | V     | 1, 2  |

| Input Leakage Current         | OV <u>&lt;</u> V <sub>IN</sub> <u>&lt;</u> Vcc  | IL <sub>I</sub>   | -5    | 5                    | μΑ    | 3     |

| Output Leakage Current        | Output(s) disabled, OV < V <sub>OUT</sub> < Vcc | ILo               | -5    | 5                    | μΑ    |       |

| Output High Voltage           | I <sub>OH</sub> = -4.0 mA                       | V <sub>OH</sub>   | 2.4   |                      | V     | 1, 4  |

| Output Low Voltage            | I <sub>OL</sub> = 8.0 mA                        | V <sub>OL</sub>   |       | 0.4                  | V     | 1, 4  |

| Supply Voltage                |                                                 | V <sub>DD</sub>   | 3.135 | 3.6                  | V     | 1     |

| Isolated Output Buffer Supply |                                                 | V <sub>DD</sub> Q | 3.135 | 3.6                  | V     | 1, 5  |

# THERMAL RESISTANCE

|           |                                             |                                                                                      | DQ      | DQC     |      |

|-----------|---------------------------------------------|--------------------------------------------------------------------------------------|---------|---------|------|

| Parameter | Description                                 | Test Conditions                                                                      | Package | Package | Unit |

| ΘJA       | Thermal Resistance (Junction to<br>Ambient) | Test conditions follow standard test methods<br>and procedures for measuring thermal | 29.41   | 30.2    | °C/W |

| ΘJC       | Thermal Resistance (Junction to Case)       | 1 0                                                                                  | 6.31    | 6.5     | °C/W |

### NOTES:

- 1. All voltages referenced to Vss (GND).

- $\begin{array}{ll} \mbox{2. Overshoot: } V_{IH} \leq +4.6V \mbox{ for } t \leq t_{KC}/2 \mbox{ for } I \leq 20mA \\ \mbox{ Undershoot: } V_{IL} \geq -0.7V \mbox{ for } t \leq t_{KC}/2 \mbox{ for } I \leq 20mA \\ \mbox{ Power-up: } V_{IH} < +3.6V \mbox{ and } V_{_{DD}} < 3.135V \mbox{ for } t < 200ms \\ \end{array}$

- 3. MODE and ZZ pins have internal pull-up resistors, and input leakage =  $\pm 10\mu$ A

- 4. The load used for V<sub>OH</sub>, V<sub>OL</sub> testing is shown in Figure 2 for 3.3V I/O. AC load current is higher than the stated DC values. AC I/O curves are available upon request.

- 5.  $V_{_{DD}}Q$  should never exceed  $V_{_{DD}}$ .  $V_{_{DD}}$  and  $V_{_{DD}}Q$  can be connected together.

- 6. This parameter is sampled.

# I<sub>DD</sub> OPERATING CONDITIONS AND MAXIMUM LIMITS (-55°C to +125°C or -40°C to +85°C)

|                                    |                                                                                                                                                                               |                  |      | MAX  |     |       |         |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|------|-----|-------|---------|

| DESCRIPTION                        | CONDITIONS                                                                                                                                                                    | SYM              | -7.5 | -8.5 | -10 | UNITS | NOTES   |

| Power Supply<br>Current: Operating | Device selected; all inputs $\leq V_{IL}$<br>or $\geq V_{IH}$ ; Cycle time $\geq t^{KC}$ MIN;<br>$V_{DD}$ = MAX; Outputs open                                                 | I <sub>DD</sub>  | 250  | 225  | 200 | mA    | 1, 2, 3 |

| Power Supply<br>Current: Idle      | Device selected; $V_{DD}$ = MAX;<br>ADSC ADSP ADV GW BWx\<br>$\geq V_{IH}$ ; All inputs $\leq V$ ss+ 0.2 or $\geq V_{DD}$ -0.2;<br>Cycle time $\leq t_{KC}$ MIN; Outputs open | I <sub>DD1</sub> | 160  | 150  | 140 | mA    | 1, 2, 3 |

| CMOS Standby                       | Device deselected; $V_{DD} = MAX$ ;<br>All inputs $\leq Vss + 0.2$ or $\geq V_{DD} - 0.2$ ;<br>All inputs static; CLK frequency = 0                                           | I <sub>SB2</sub> | 90   | 90   | 90  | mA    | 2, 3    |

| TTL Standby                        | Device deselected; $V_{DD}$ = MAX;<br>All inputs $\leq V_{IL}$ or $\geq V_{IH}$ ;<br>All inputs static; CLK frequency = 0                                                     | I <sub>SB3</sub> | 130  | 130  | 130 | mA    | 2, 3    |

# CAPACITANCE

| DESCRIPTION              | CONDITIONS                       | SYM | MAX | UNITS | NOTES |

|--------------------------|----------------------------------|-----|-----|-------|-------|

| Input Capacitance        | T <sub>A</sub> = 25°C; f = 1MHz; | CI  | 6   | pF    | 4     |

| Input/Output Capacitance | V <sub>DD</sub> = 3.3V           | Co  | 8   | pF    | 4     |

### NOTES:

1.  $I_{DD}$  is specified with no output current and increases with faster cycle times.  $I_{DD}Q$  increases with faster cycle times and greater output loading.

2. "Device deselected" means device is in power-down mode as defined in the truth table. "Device selected" means device is active (not in power-down mode).

3. A typical value is measured at 3.3V, 25°C and 15ns cycle time.

4. This parameter is sampled.

## ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS

(Note 1) (-55°C to +125°C or -40°C to +85°C)

| DESCRIPTION                             | SYMBOL            | -75 |     | -8.5 |     | -10  |      | UNITS | NOTES       |

|-----------------------------------------|-------------------|-----|-----|------|-----|------|------|-------|-------------|

|                                         |                   | MIN | MAX | MIN  | MAX | MIN  | MAX  | UNITS | NOTES       |

| CLOCK                                   |                   |     |     |      |     |      |      |       |             |

| Clock cycle time                        | t <sub>KC</sub>   | 8.5 |     | 10.0 |     | 15.0 |      | ns    |             |

| Clock frequency                         | t <sub>KF</sub>   |     | 117 |      | 100 |      | 66   | MHz   |             |

| Clock HIGH time                         | t <sub>KH</sub>   | 2.5 |     | 3.0  |     | 4.0  |      | ns    | 2           |

| Clock LOW time                          | t <sub>KL</sub>   | 2.5 |     | 3.0  |     | 4.0  |      | ns    | 2           |

| OUTPUT TIMES                            |                   |     |     |      |     |      |      |       |             |

| Clock to output valid                   | t <sub>KQ</sub>   | 7.5 |     |      | 8.5 |      | 10.0 | ns    |             |

| Clock to output invalid                 | t <sub>KQX</sub>  | 2.5 |     | 2.5  |     | 2.5  |      | ns    | 3           |

| Clock to output in Low-Z                | t <sub>KQLZ</sub> | 2.5 |     | 2.5  |     | 2.5  |      | ns    | 3, 4, 5, 6, |

| Clock to output in High-Z               | t <sub>KQHZ</sub> |     | 4.0 |      | 5.0 |      | 5.0  | ns    | 3, 4, 5, 6, |

| OE\ to output valid                     | t <sub>OEQ</sub>  |     | 3.4 |      | 4.4 |      | 5.0  | ns    | 7           |

| OE\ to output in Low-Z                  | t <sub>OELZ</sub> | 0   |     | 0    |     | 0    |      | ns    | 3, 4, 5, 6, |

| OE\ to output in High-Z                 | t <sub>OEHZ</sub> |     | 3.5 |      | 4.4 |      | 5.0  | ns    | 3, 4, 5, 6, |

| SETUP TIMES                             |                   |     |     |      |     |      |      |       |             |

| Address                                 | t <sub>AS</sub>   | 1.5 |     | 1.8  |     | 2.0  |      | ns    | 8, 9        |

| Address status (ADSC ADSP\)             | t <sub>ADSS</sub> | 1.5 |     | 1.8  |     | 2.0  |      | ns    | 8, 9        |

| Address advance (ADV\)                  | t <sub>AAS</sub>  | 1.5 |     | 1.8  |     | 2.0  |      | ns    | 8, 9        |

| Byte write enables (BWa\ - BWd GW BWE\) | t <sub>WS</sub>   | 1.5 |     | 1.8  |     | 2.0  |      | ns    | 8, 9        |

| Data-in                                 | t <sub>DS</sub>   | 1.5 |     | 1.8  |     | 2.0  |      | ns    | 8, 9        |

| Chip enable (CE\)                       | t <sub>CES</sub>  | 1.5 |     | 1.8  |     | 2.0  |      | ns    | 8, 9        |

| HOLD TIMES                              |                   |     |     |      |     |      |      |       |             |

| Address                                 | t <sub>AH</sub>   | 0.5 |     | 0.5  |     | 0.5  |      | ns    | 8, 9        |

| Address status (ADSC ADSP\)             | t <sub>ADSH</sub> | 0.5 |     | 0.5  |     | 0.5  |      | ns    | 8, 9        |

| Address advance (ADV\)                  | t <sub>AAH</sub>  | 0.5 |     | 0.5  |     | 0.5  |      | ns    | 8, 9        |

| Byte write enables (BWa\ - BWd GW BWE\) | t <sub>WH</sub>   | 0.5 |     | 0.5  |     | 0.5  |      | ns    | 8, 9        |

| Data-in                                 | t <sub>DH</sub>   | 0.5 |     | 0.5  |     | 0.5  |      | ns    | 8, 9        |

| Chip enable (CE\)                       | t <sub>CEH</sub>  | 0.5 |     | 0.5  |     | 0.5  |      | ns    | 8, 9        |

#### NOTE:

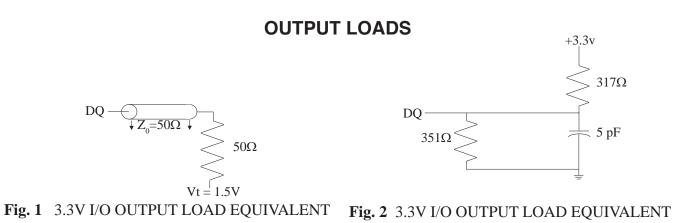

1. Test conditions as specified with the output loading shown in Figure 1 unless otherwise noted.

- 2. Measured as HIGH above  $\boldsymbol{V}_{IH}$  and LOW below  $\boldsymbol{V}_{IL}.$

- 3. This parameter is measured with the output loading shown in Figure 2 for 3.3V I/O.

- 4. This parameter is sampled.

- 5. Transition is measured  $\pm$ 500mV from steady state voltage.

- 6. Refer to Technical Note TN-58-09, "Synchronous SRAM Bus Contention Design Considerations," for a more thorough discussion on these parameters.

- 7. OE\ is a "Don't Care" when a byte write enable is sampled LOW.

8. A READ cycle is defined by byte write enables all HIGH or ADSP\LOW for the required setup and hold times. A WRITE cycle is defined by at

least one byte write enable LOW and ADSP\ HIGH for the required setup and hold times.

9. This is a synchronous device. All addresses must meet the specified setup and hold times for all rising edges of CLK when either ADSP\ or ADSC\ is LOW and chip enabled. All other synchronous inputs must meet the setup and hold times with stable logic levels for all rising edges of clock (CLK) when the chip is enabled. Chip enable must be valid at each rising edge of CLK when either ADSP\ or ADSC\ is LOW to remain enabled.

## **AC TEST CONDITIONS**

| Input Pulse Levels            | 0V to 3.0V      |

|-------------------------------|-----------------|

| Input rise and fall times     | 1.5ns           |

| Input timing reference levels | 1.5V            |

| Output reference levels       | 1.5V            |

| Output loadSee F              | figures 1 and 2 |

|                               |                 |

**NOTE:** SRAM timing is dependent upon the capacitive loading on the outputs.

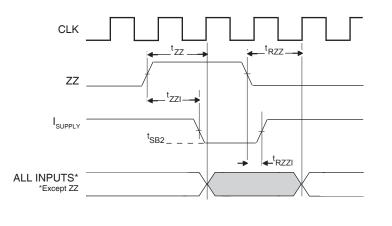

### SNOOZE MODE

SNOOZE MODE is a low-current, "power-down" mode in which the device is deselected and current is reduced to

$I_{SB2Z}$ . The duration of SNOOZE MODE is dictated by the length of time ZZ is in a HIGH state. After the device enters SNOOZE MODE, all inputs except ZZ become gated inputs and are ignored.

ZZ is an asynchronous, active HIGH input that causes the device to enter SNOOZE MODE. When ZZ becomes a logic

HIGH,  $I_{SB2Z}$  is guaranteed after the setup time  $t_{ZZ}$  is met. Any READ or WRITE operation pending when the device enters SNOOZE MODE is not guaranteed to complete successfully. Therefore, SNOOZE MODE must not be initiated until valid pending operations are completed.

## SNOOZE MODE ELECTRICAL CHARACTERISTICS

| DESCRIPTION                        | CONDITIONS      | SYM               | MIN               | MAX               | UNITS | NOTES |

|------------------------------------|-----------------|-------------------|-------------------|-------------------|-------|-------|

| Current during SNOOZE MODE         | $ZZ \ge V_{IH}$ | I <sub>SB2Z</sub> |                   | 80                | mA    |       |

| ZZ active to input ignored         |                 | t <sub>ZZ</sub>   |                   | 2t <sub>cyc</sub> | ns    | 1     |

| ZZ inactive to input sampled       |                 | t <sub>RZZ</sub>  | 2t <sub>cyc</sub> |                   | ns    | 1     |

| ZZ active to snooze current        |                 | t <sub>ZZI</sub>  |                   | 2t <sub>cyc</sub> | ns    | 1     |

| ZZ inactive to exit snooze current |                 | t <sub>RZZI</sub> | 0                 |                   | ns    | 1     |

**NOTE:** 1. This parameter is sampled.

# SNOOZE MODE WAVEFORM

transforming specialty electronics

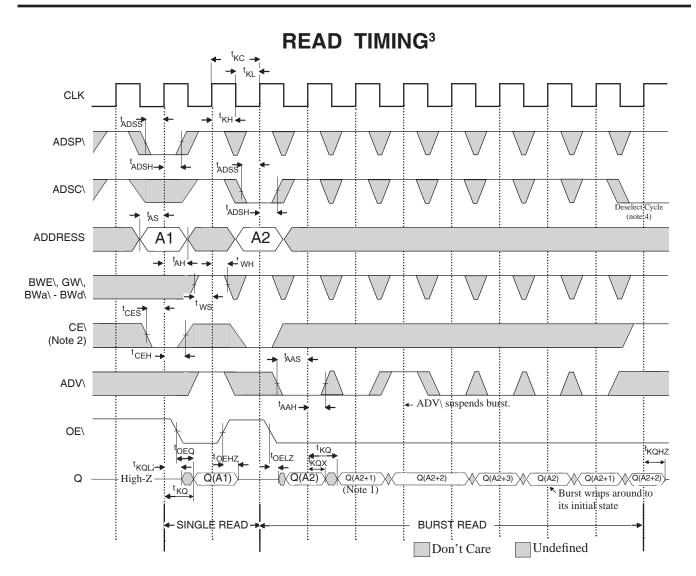

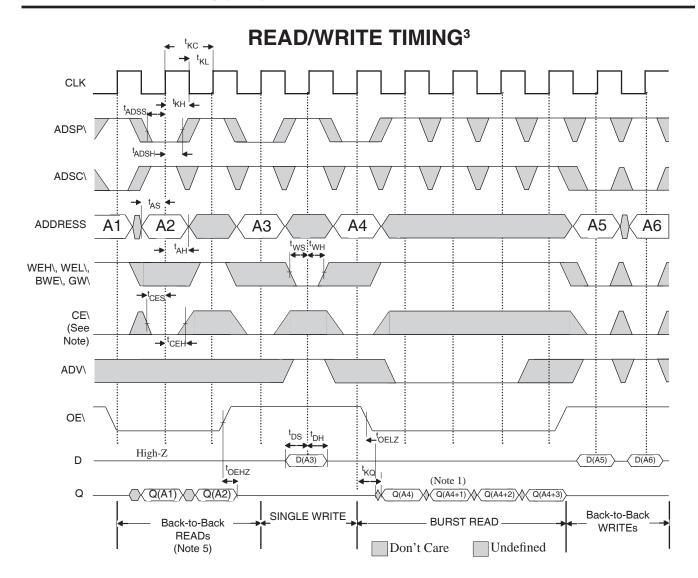

NOTE: 1. Q(A2) refers to output from address A2. Q(A2+1) refers to output from the next internal burst address following A2.

- 2. CE2\ and CE2 have timing identical to CE $\$ . On this diagram, when CE $\$  is LOW, CE2 $\$  is LOW and CE2 is HIGH. When CE $\$  is HIGH, CE2 $\$  is HIGH and CE2 is LOW.

- 3. Timing is shown assuming that the device was not enabled before entering into this sequence.

- 4. Outputs are disabled t<sub>KQHZ</sub> after deselect.

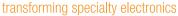

NOTE: 1. D(A2) refers to output from address A2. D(A2+1) refers to output from the next internal burst address following A2.

2. CE2\ and CE2 have timing identical to CE\. On this diagram, when CE\ is LOW, CE2\ is LOW and CE2 is HIGH. When CE\ is HIGH, CE2\ is HIGH and CE2 is LOW.

3. OE\ must be HIGH before the input data setup and held HIGH throughout the data hold time. This prevents input/output data contention for the time period prior to the byte write enable inputs being sampled.

- 4. ADV must be HIGH to permit a WRITE to the loaded address.

- 5. Full-width WRITE can be initiated by GW\ LOW; or GW\ HIGH and BEW\, BWa\ BWd\ LOW.

transforming specialty electronics

NOTE: 1. Q(A4) refers to output from address A. Q(A4+1) refers to output from the next internal burst address following A4.

- 2. CE2\ and CE2 have timing identical to CE\. On this diagram, when CE\ is LOW, CE2\ is LOW and CE2 is HIGH. When CE\ is HIGH, CE2\ is HIGH and CE2 is LOW.

- The data bus (Q) remains in High-A following a WRITE cycle unless an ADSP\, ADSC\ or ADV\ cycle is performed.

GW\ is HIGH.

Back-to-back READs may be controlled by either ADSP\ or ADSC\.

transforming specialty electronics

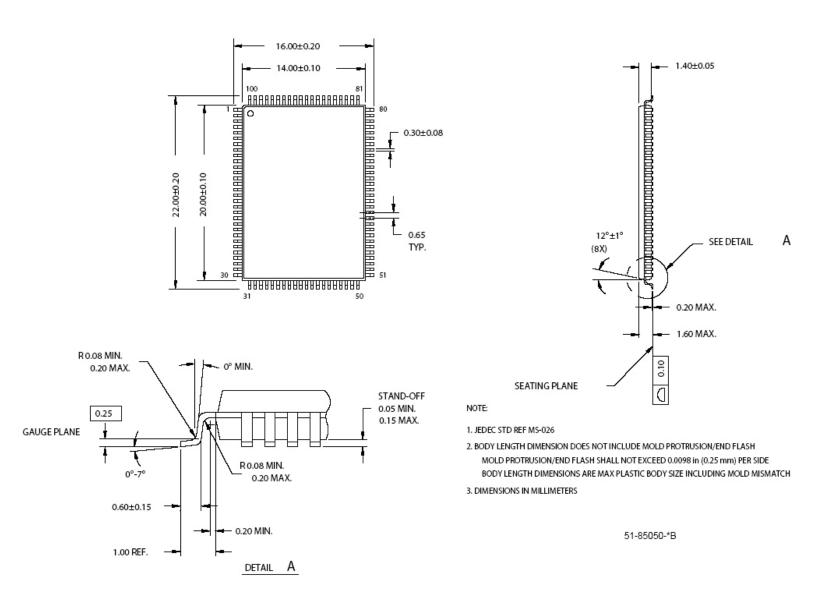

# **MECHANICAL DEFINITION** 100-Pin TQFP (Package Designator DQ)

# **ORDERING INFORMATION**

### TQFP

EXAMPLE: AS5SS256K36DQ-10/IT

| Device Number | Package<br>Type | Speed ns | Process |  |

|---------------|-----------------|----------|---------|--|

| AS5SS256K36   | DQ              | -8.5     | /*      |  |

| AS5SS256K36   | DQ              | -10      | /*      |  |

### **\*AVAILABLE PROCESSES**

| IT = Industrial Temperature Range | -40°C to +85°C                    |

|-----------------------------------|-----------------------------------|

| ET = Enhanced Temperature Range   | -40°C to +105°C                   |

| XT = Military Temperature Range   | $-55^{\circ}C$ to $+125^{\circ}C$ |

# DOCUMENT TITLE 256K x 36 SSRAM Flow-Through, Synchronous Burst SRAM

## **REVISION HISTORY**

| <u>Rev #</u><br>4.0 | <u>History</u><br>Removed "A" Version                                                                                                                                                                                                                                                        |            | Release Date<br>November 2009 | <u>Status</u><br>Release |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------|--------------------------|

| 4.1                 | Updated Micross Information                                                                                                                                                                                                                                                                  |            | January 2010                  | Release                  |

| 4.2                 | $\begin{array}{cccccc} t_{_{KQX}} min & 3.0ns & 2 \\ t_{_{KQLZ}} min & 3.0ns & 2 \\ t_{_{OEQ}} \& t_{_{OEHZ}} max & 5.0ns & 4 \\ I_{_{DD}} max (-8.5) & 325mA & 2 \\ & (-10) & 250mA & 2 \\ I_{_{DD1}} max (-8.5) & 85mA & 1 \\ & (-10) & 65mA & 1 \\ I_{_{SB2}} max & 15mA & 9 \end{array}$ | and<br>SpF | A<br>A<br>A                   | Release                  |

| 4.3                 | Added DQC package on the Thern Resistance table, page 7.                                                                                                                                                                                                                                     | nal        | September 2011                | Release                  |

| 4.4                 | Removed Cu-lead frame option                                                                                                                                                                                                                                                                 |            | October 2013                  | Release                  |