# Fast Dual Bi-Directional Bus Buffer with Hot Insertion Logic

#### 1 FEATURES

- · Dual, bi-directional unity gain isolating buffer

- Hot insertion logic prevents data and clock bus corruption for live backplane applications

- Pre-charge minimises data corruption on live insertion

- Supports I<sup>2</sup>C<sup>(1)</sup> bus (standard and fast modes), SMBus (standard and high power modes) and PMbus

- · Open-collector Ready output.

- Fast switching times allow operation in excess of 1MHz

- · Enable allows bus segments to be disconnected

- · Low current stand-by mode when not enabled

- · High impedance ports when IC unpowered

- 4 mA (static) pull-down capability

- · Low noise susceptibility

- Supports the connection of several buffers in series.

- Level shift bus voltages from 1.8 V to 15 V

#### 2 APPLICATIONS

- Backplane Management / Interconnect

- · Telecommunications Systems including ATCA

- Desktop and Portable Computers including RAID

- (1) I<sup>2</sup>C is a trademark of NXP B.V.

#### 3 GENERAL DESCRIPTION

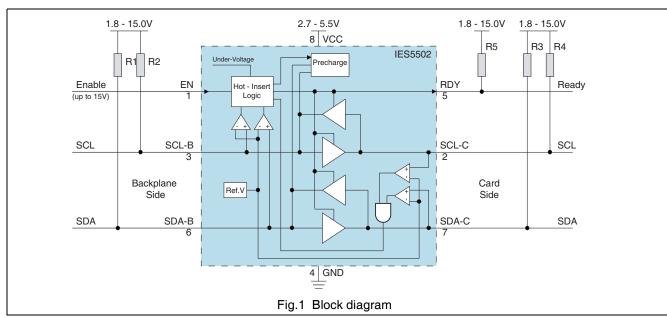

The IES5502 is a monolithic bipolar integrated circuit for bus buffering in applications including I<sup>2</sup>C, SMBus, PMbus, and other systems based on similar principles.It extends the functionality of the IES5501 to include hot-insertion logic for detecting stop and idle conditions, making it ideal for live insertion into backplanes. The buffer extends the bus load limit by buffering both the SCL and SDA lines.

Hot insertion logic allows the IC to be plugged into live backplanes without causing data corruption on the bus. The open-collector READY signal indicates when the connection has been made. Precharging of the backplane ports minimises disruptions to the bus during hot insertion.

The enable function allows sections of the bus to be isolated. Individual parts of the system can be brought on-line successively. Bus level translation between a very wide range of bus voltages, from 1.8 V to 15 V, is supported. These features provide enormous flexibility in interfacing systems of different technologies, operating speeds and loads.

The unique operation of the IES5502 provides one of the fastest response times of such bi-directional buffers. It does this without the need for "rise-time accelerators" which, combined with low noise margins, may cause glitches outside of the  $I^2C$  specification.

#### 4 BLOCK DIAGRAM

© 2008 Hendon Semiconductors Pty. Ltd., all rights reserved.

Contents are subject to the Disclaimer

### **Fast Dual Bi-Directional Bus Buffer** with Hot Insertion Logic

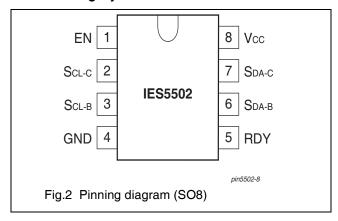

#### PINNING INFORMATION

#### 5.1 Pinning layout

Pin description

5.2

| SYMBOL            | PIN | DESCRIPTION                 |  |

|-------------------|-----|-----------------------------|--|

| EN                | 1   | Enable                      |  |

| S <sub>CL-C</sub> | 2   | SCL Buffer, Card* Side      |  |

| S <sub>CL-B</sub> | 3   | SCL Buffer, Backplane* Side |  |

| GND               | 4   | Supply Ground               |  |

| RDY               | 5   | Ready                       |  |

| S <sub>DA-B</sub> | 6   | SDA Buffer, Backplane* Side |  |

| S <sub>DA-C</sub> | 7   | SDA Buffer, Card* Side      |  |

| $V_{CC}$          | 8   | Positive supply             |  |

<sup>\*</sup>For device family compatability, please note: Backplane Side is equivalent to SCL<sub>IN</sub> / SDA<sub>IN</sub> Card Side is equivalent to SCL<sub>OUT</sub> / SDA<sub>OUT</sub>

#### **FUNCTIONAL DESCRIPTION**

#### 6.1 V<sub>CC</sub>, GND - DC supply pins

The IES5502 can be driven from voltage supplies ranging from 2.7 V to 5.5 V. The threshold level below which the output will begin to match the input is 33% of V<sub>CC</sub>. Hence, the operating voltage should be chosen with the required bus voltage, switching threshold, and noise margins, in mind.

#### 6.2 $S_{CL-B}$ , $S_{CL-C}$ , $S_{DA-B}$ , $S_{DA-C}$ - Buffer inputs/outputs

The two buffers (S<sub>CL</sub> and S<sub>DA</sub>) are identical and symmetrical. The buffers can be driven from either direction, with the same buffering response. However, the hot insertion logic is determined from the "backplane"  $(S_{xx-B})$  sides of the buffers. When the one side of (e.g.  $S_{xx-B}$ ) of the buffer is being driven low (<0.3 $V_{CC}$ ) by another device on the bus, the other side (e.g. Sxx-C) will be driven low by the IC to provide the buffered output.

The "control" or "input" side is determined by the lowest externally driven signal. Therefore if the "input" is externally pulled to  $V_{Sxx-B} = 250 \text{ mV}$ , and the "output" is externally pulled to  $V_{Sxx-C} = 500 \text{ mV}$ , the buffer will pull the "output" down further such that it becomes  $V_{Sxx-C} = V_{Sxx-B} + V_{OFFSET}$ . Should the "output"

subsequently become lower than the "input" by means of an external device pulling it low  $(V_{Sxx-C} < V_{Sxx-B})$ , control of the buffering operation will switch sides. The voltage at the "input" will then become  $V_{Sxx-B} = V_{Sxx-C} + V_{OFFSET}$ . Many

bus buffers are prone to causing glitches during control transition, but the IES5502 shows negligible glitching even under the worst operating conditions.

#### 6.3 **Enable (EN) - Activate Buffer Operations**

The enable input (EN) is used to disable the buffer, for the purpose of isolating sections of the bus. The IC should only be disabled when the bus is idle, to prevent truncation of commands which may confuse other devices on the bus.

Upon receiving a valid Enable signal, the IC will wait to detect either a bus STOP condition, or an IDLE condition as described in the I<sup>2</sup>C<sup>(1)</sup> and SMBus<sup>(2)</sup> specifications. This ensures that truncated transmissions are not communicated along the newly enabled bus segment.

Enable may be used to progressively activate sections of the bus during system start-up. Bus sections slow to respond on power-up can be kept isolated from the main system to avoid interference and collisions.

The Enable pin may be pulled up higher than the Vcc of the buffer, further enhancing the capability of the IES5502 in a level shifting role. For example, a microprocessor could drive Enable, S<sub>CL-B</sub> and S<sub>DA-B</sub> at 5V, while the buffer V<sub>CC</sub>,  $S_{CL-C}$  and  $S_{DA-C}$  ports are at 3.3V.

Similarly, the threshold level of the Enable pin allows a 1.8V device to enable an IES5502 with a  $V_{CC}$  of 3.3V.

<sup>&</sup>quot;UM10204: I2C-bus Specification and User Manual", Rev 03, 19 June 2007, NXP B.V.

<sup>(2) &</sup>quot;System Management Bus (SMBus) Specification", Version 2.0, August 3, 2000, SBS Implementers Forum.

# Fast Dual Bi-Directional Bus Buffer with Hot Insertion Logic

#### 6.4 Ready (RDY) - Buffer Connected Indicator

The ready output (RDY) indicates that the buffer has met it's enable conditions, and that communication will now occur. This is an open-collector transistor which is switched off when ready, allowing the voltage at the pin to be pulled high by a pull-up resistor.

#### 6.5 Start-up

During power-up or live insertion into backplanes, the IES5502 will start-up in an under voltage lock-out state (UVLO) where any activity on the input-output ports will be ignored. This is to ensure that the IES5502 does not try to operate when there is not enough voltage on the supply.

During this time, the pre-charge circuit will charge all  $S_{CL-B}/S_{DA-B}$  backplane ports to a typically 0.73V. This will minimise any voltage difference between the ports and hence minimises disruptions to the bus during hot insertion into backplanes.

When the supply increases above the UVLO state, the IES5502 will then monitor the bus for either stop bit or bus idle condition. When a stop bit condition is detected and  $S_{CL\text{-}C}/S_{DA\text{-}C}$  are both idle or when all  $S_{CL}/S_{DA}$  ports idle for a time period of typically  $95\mu S$ , then the IES5502 will activate the input-output connection circuitry. The pre-charge circuitry is switched off. The voltage at the READY pin is pulled high by an external pull-up resistor to indicate the input-output connection has been made.

#### 7 LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134) Voltages are specified with respect to pin 4 (GND)

| SYMBOL             | PARAMETER                                                                                      | CONDITIONS | MIN. | MAX. | UNIT |

|--------------------|------------------------------------------------------------------------------------------------|------------|------|------|------|

| V <sub>CC</sub>    | Supply voltage range (V <sub>CC</sub> )                                                        |            | -0.3 | +7   | ٧    |

| V <sub>Sxx-x</sub> | Voltage range (S <sub>CL-B</sub> , S <sub>CL-C</sub> , S <sub>DA-B</sub> , S <sub>DA-C</sub> ) |            | -0.3 | +16  | V    |

| V <sub>EN</sub>    | Voltage range (EN)                                                                             |            | -0.3 | +16  | V    |

| 1                  | DC current (any pin)                                                                           |            | _    | 20   | mA   |

| P <sub>tot</sub>   | total power dissipation                                                                        |            | _    | 300  | mW   |

| T <sub>stg</sub>   | storage temperature                                                                            |            | -55  | +125 | °C   |

| T <sub>amb</sub>   | operating ambient temperature                                                                  |            | -40  | +85  | °C   |

#### **8 CHARACTERISTICS**

All specifications apply over the full operating temperature range of  $T_{amb} = -40$ °C to +85°C; Voltages are specified with respect to pin 4 (GND)

| SYMBOL           | PARAMETER                      | CONDITIONS                                                | MIN. | TYP.               | MAX. | UNIT |  |  |

|------------------|--------------------------------|-----------------------------------------------------------|------|--------------------|------|------|--|--|

| Power supp       | Power supply                   |                                                           |      |                    |      |      |  |  |

| V <sub>CC</sub>  | supply voltage (operating)     |                                                           | 2.7  | _                  | 5.5  | V    |  |  |

| I <sub>CC</sub>  | supply current (operating)     | V <sub>CC</sub> = V <sub>EN</sub> = 5.5V                  | _    | 6.1                | _    | mA   |  |  |

|                  | supply current (stand-by)      | $V_{CC} = 5.5V, V_{EN} = 0V$                              | _    | 580                | _    | μΑ   |  |  |

| Startup circ     | Startup circuitry              |                                                           |      |                    |      |      |  |  |

| UVLO             | under voltage lock-out level   | V <sub>CC</sub> = V <sub>EN</sub>                         | _    | 2.2                | _    | V    |  |  |

| V <sub>PRE</sub> | precharge voltage level        | $V_{xxx-B}$ floating, $V_{CC} = 3.3V$ , $V_{EN} > 1.2V$   | _    | 0.73               | _    | V    |  |  |

| I <sub>PRE</sub> | precharge current level        | $V_{xxx-B} > V_{PRE}$ , $V_{CC} = 3.3V$ , $V_{EN} > 1.2V$ | _    | 20                 | _    | μА   |  |  |

| V <sub>THR</sub> | logic input threshold voltage  |                                                           | _    | 0.5V <sub>CC</sub> | _    | V    |  |  |

|                  | logic output threshold voltage |                                                           | _    | 0.5V <sub>CC</sub> | _    | V    |  |  |

# Fast Dual Bi-Directional Bus Buffer with Hot Insertion Logic

| SYMBOL               | PARAMETER                            | CONDITIONS                                               | MIN.                | TYP.                | MAX.                | UNIT |  |

|----------------------|--------------------------------------|----------------------------------------------------------|---------------------|---------------------|---------------------|------|--|

| Buffer Ports         |                                      |                                                          |                     |                     |                     |      |  |

| V <sub>Sxx-x</sub>   | Bus voltage                          |                                                          | 1.8                 | _                   | 15                  | ٧    |  |

| V <sub>TL</sub>      | Input low threshold voltage          |                                                          | 0.30V <sub>CC</sub> | 0.33V <sub>CC</sub> | 0.41V <sub>CC</sub> | ٧    |  |

| I <sub>IL</sub>      | Input low current                    | V <sub>Sxx-x</sub> < V <sub>CC</sub>                     | _                   | _                   | -10                 | μΑ   |  |

| I <sub>OL</sub>      | Output low sink current              | $V_{Sx-xx(in)} = 0V$                                     | 4                   | _                   | _                   | mA   |  |

| V <sub>OFFSET</sub>  | Input-output offset voltage          | $I_{OL} = 4 \text{ mA}, V_{Sxx-x(in)} = 50\text{mV}$     | _                   | 200                 | 250                 | mV   |  |

|                      | $(V_{CC} = 3.3V)$                    | $I_{OL} = 500 \mu A, V_{Sxx-x(in)} = 50 mV$              | _                   | 80                  | 100                 | mV   |  |

|                      |                                      | $I_{OL} = 1.2 \text{mA}, V_{Sxx-x(in)} = 200 \text{mV}$  | _                   | 85                  | 125                 | mV   |  |

| I <sub>LEAK</sub>    | Leakage current                      | $V_{Sxx-x} = V_{CC}$                                     | _                   | _                   | ±5                  | μΑ   |  |

| Enable               |                                      |                                                          |                     |                     |                     |      |  |

| V <sub>EN</sub>      | Enable active voltage                |                                                          | 1.2                 | _                   | _                   | ٧    |  |

| V <sub>DISABLE</sub> | Disable (stand-by) voltage           |                                                          | _                   | _                   | 0.8                 | ٧    |  |

| I <sub>EN</sub>      | Enable Pin Current                   | V <sub>EN</sub> > 1.2V                                   | 1                   | _                   | 5                   | μΑ   |  |

| Ready                |                                      |                                                          |                     |                     |                     |      |  |

| V <sub>RL</sub>      | Ready low voltage                    | I <sub>RDY</sub> = 3mA                                   | _                   | _                   | 400                 | mV   |  |

| I <sub>leak</sub>    | leakage current                      | $V_{RDY} = V_{CC}$                                       | _                   | _                   | ±5                  | μΑ   |  |

| Timing Chai          | Timing Characteristics (note 1)      |                                                          |                     |                     |                     |      |  |

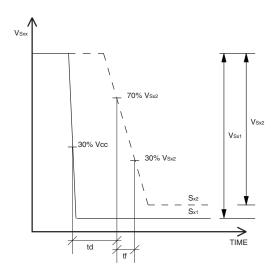

| td                   | Response Delay                       | 0.3V <sub>CC</sub> to 0.7V <sub>Sxx-x(out)</sub>         | _                   | 45                  | _                   | ns   |  |

| tf                   | Fall Time                            | 0.7V <sub>Sxx-x(out)</sub> to 0.3V <sub>Sxx-x(out)</sub> | _                   | 40                  | _                   | ns   |  |

| f <sub>Sxx</sub>     | Operating Frequency                  |                                                          | 0                   | 400                 | _                   | kHz  |  |

| t <sub>idle</sub>    | Bus Idle Time                        | $V_{Sxxx-x} = V_{EN} = V_{CC} = 3.3V$                    | 50                  | 95                  | 150                 | μs   |  |

|                      |                                      | $V_{Sxxx-x} = V_{EN} = V_{CC} = 5.5V$                    | 50                  | 75                  | 120                 | μs   |  |

| t <sub>ENLH</sub>    | ENABLE High to READY off             |                                                          | _                   | 95                  | _                   | μs   |  |

| t <sub>ENHL</sub>    | ENABLE Low to READY on               |                                                          | _                   | 1                   |                     | μs   |  |

| t <sub>RDYLH</sub>   | READY High to V <sub>Sxxx-x</sub> on |                                                          |                     | 1                   |                     | μs   |  |

| t <sub>RDYHL</sub>   | READY Low to V <sub>Sxxx-x</sub> off |                                                          | _                   | 1.1                 |                     | μs   |  |

#### Note

1. Guaranteed by design (not subject to test), except for  $t_{\text{idle}}$

# Fast Dual Bi-Directional Bus Buffer with Hot Insertion Logic

Fig.3 Timing Parameters

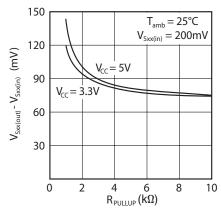

Fig.4 Offset Voltage, Vout - Vin

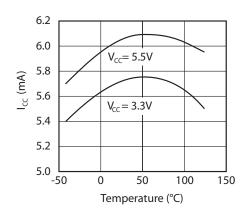

Fig.5 Supply Current vs Temperature

# Fast Dual Bi-Directional Bus Buffer with Hot Insertion Logic

#### 9 APPLICATION INFORMATION

#### 9.1 Design Considerations

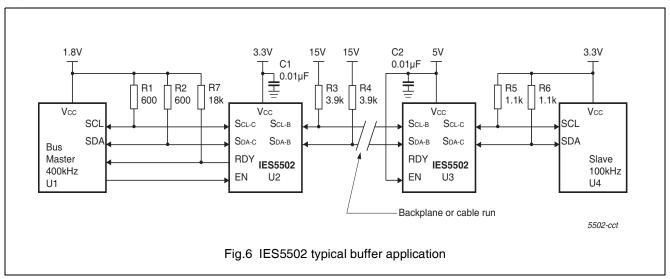

Figure 6 shows a typical application for the IES5502. The IC can level shift between various bus voltages, without the need for additional external components. Higher bus voltages and currents outside the range of the standard I<sup>2</sup>C bus specification can be catered for, providing a longer range capability and higher noise immunity.

The enable pin can be used to interface buses of different operating frequencies. When enabled, the bus frequency is limited to the maximum 100 kHz of the slave device. When disabled, the slave is isolated, and the remaining bus can be run at 400 kHz. The timing performance and current sinking capability will allow it to run well in excess of the 400 kHz maximum limit of the I<sup>2</sup>C fast mode.

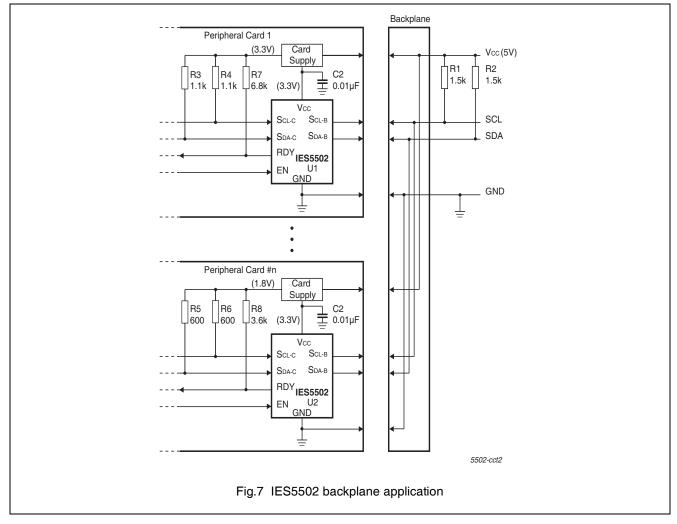

Figure 7 shows the IES5502 used in a backplane application. Peripheral cards and backplanes operating at a range of voltages can be interfaced together using a minimum of components. In this example, cards are running at 1.8 V and 3V, while the backplane is at 5V. Cards operating buses between 1.8 V and 15 V can be catered for in the same system.

Each card can be safely isolated from the system by disabling the IES5502 at the interface to the backplane. The Hot-Insertion logic on the IES5502 protects against corrupted or truncated data transmissions on start-up of buffer operations.

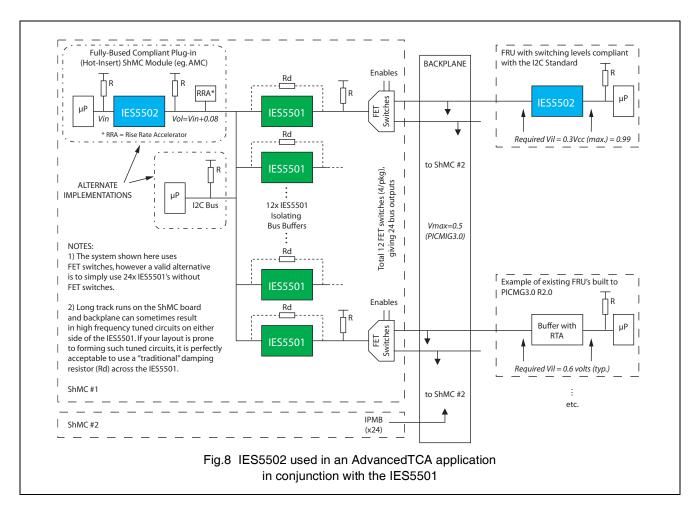

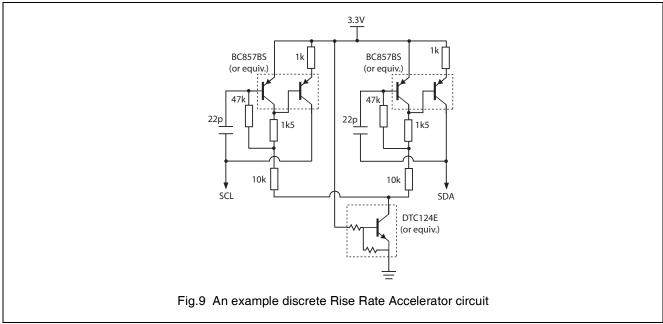

An ideal backplane application for the IES5502 is the Advanced Telecom Computing Architecture (AdvancedTCA) as shown in Figure 8. The IES5502 is well suited to placement on "Field Replaceable Units" (FRUs) used in either a conventional fully-bused arrangement (not shown) or in the low cost high noise margin radial architecture example as shown in Figure 9. It is fully interoperable with existing systems and components. If required, Figure 9 shows a simple low-cost circuit for use at the Shelf Manager for accelerating the rise in bused systems.

In each of these examples, the buffers are intended to extend total system capacitance above 400pF, so anticipate high capacitance on each side. When loading on one side is small, adding 47pF is suggested to avoid any waveform ripple, should it occur.

#### 9.2 Input to Output Offset Voltage Calculation

The offset voltage between the side acting as the output  $(S_{xx(out)})$  and the side acting as the input  $(S_{xx(in)})$  of the IES5502 can be calculated using the relationship:

$$V_{Sxx(out)} = V_{Sxx(in)} + 69mV + (V_{BUS}/R) \bullet 15[\Omega]$$

This calculation is valid for  $V_{Sxx(in)} \ge 200 \text{mV}$ , as below this point the saturation voltage of the open collector output drive transistor will begin to affect the characteristic. Input and output voltages are shown in millivolts,  $V_{BUS}$  (the supply voltage to the bus) is in volts, and R is in ohms.

An example calculation for VBUS = 3.3V,  $V_{SA1}$  = 200mV, the resistance R pulling up  $S_{A2}$  is 2k, then the voltage on  $S_{A2}$  is typically:

$$V_{SA2} = 200 \text{mV} + 69 \text{mV} + (3.3/2000) \bullet 15$$

= 294 mV

This can be compared with the offset characteristic shown in Figure 4.

# Fast Dual Bi-Directional Bus Buffer with Hot Insertion Logic

#### **Application circuits**

# Fast Dual Bi-Directional Bus Buffer with Hot Insertion Logic

# Fast Dual Bi-Directional Bus Buffer with Hot Insertion Logic

#### 10 ORDERING INFORMATION

| TYPE     | PACKAGE |                                                           |          |       |

|----------|---------|-----------------------------------------------------------|----------|-------|

| NUMBER   | NAME    | DESCRIPTION                                               | VERSION  | ROHS  |

| IES5502T | SO8     | plastic small outline package; 8 leads; body width 3.9 mm | SOT96-1  | Yes 🧀 |

| IES5502D | MSOP-8L | micro small outline package; 8 leads; body width 3.0 mm   | SOT505-1 | Yes 🧀 |

Other package options are available - contact Hendon Semiconductors for details. For more information on packages, please refer to the document "Integrated Circuit Packaging and Soldering Information" on the Hendon Semiconductors web site.

#### 11 ESD CAUTION

Electrostatic Discharge (ESD) sensitive device. ESD can cause permanent damage or degradation in the performance of this device. This device contains ESD protection structures aimed at minimising the impact of ESD. However, it is the users responsibility to ensure that proper ESD precautions are observed during the handling, placement and operation of this device.

#### 12 DOCUMENT HISTORY

| REVISION | DATE     | DESCRIPTION                                                                        |

|----------|----------|------------------------------------------------------------------------------------|

| 1.0      | 20080320 | Product Specification                                                              |

| 1.1      | 20080421 | Pre-charge condition update                                                        |

| 1.2      | 20080513 | Fix pre-charge condition typo                                                      |

| 1.3      | 20080526 | Note to table in Section 5.2                                                       |

| 1.4      | 20080724 | Change from commercial to industrial temperature; update section 8 characteristics |

# Fast Dual Bi-Directional Bus Buffer with Hot Insertion Logic

#### 13 DEFINITIONS

| Data sheet status              |                                                                                                                                                                                                                       |  |  |  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Engineering sample information | This contains draft information describing an engineering sample provided to demonstrate possible function and feasibility. Engineering samples have no guarantee that they will perform as described in all details. |  |  |  |

| Objective specification        | This data sheet contains target or goal specifications for product development.  Engineering samples have no guarantee that they will function as described in all details.                                           |  |  |  |

| Preliminary specification      | This data sheet contains preliminary data; supplementary data may be published later. Products to this data may not yet have been fully tested, and their performance fully documented.                               |  |  |  |

| Product specification          | This data sheet contains final product specifications.                                                                                                                                                                |  |  |  |

| Limiting values                |                                                                                                                                                                                                                       |  |  |  |

#### **Limiting values**

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

#### **Application information**

Where application information is given, it is advisory and does not form part of the specification.

#### 14 COMPANY INFORMATION

HENDON SEMICONDUCTORS PTY. LTD. ABN 17 080 879 616

Postal address:

Hendon Semiconductors

PO Box 2226

Port Adelaide SA 5015

**AUSTRALIA**

Street Address:

Hendon Semiconductors

1 Butler Drive Hendon SA 5014 AUSTRALIA

Telephone: +61 8 8348 5200 Facsimile: +61 8 8243 1048

World Wide Web: www.hendonsemiconductors.com

www.bus-buffer.com

Email: hendon.info@hendonsemiconductors.com

# Fast Dual Bi-Directional Bus Buffer with Hot Insertion Logic

#### 15 DISCLAIMER

Hendon Semiconductors Pty. Ltd. ABN 17 080 879 616 ("Hendon") reserves the right to make changes to both its products and product data without notice.

Hendon makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Hendon assume any liability arising out of the use or application of any Hendon product. Hendon specifically disclaims any and all liability, including without limitation incidental or consequential damages. It is the responsibility of the customer to ensure that in all respects the application in which Hendon goods are used is suited to the purpose of the end user.

Typical performance figures, where quoted may depend on the application and therefore must be validated by the customer in each particular application. It is the responsibility of customers to ensure that any designs using Hendon products comply with good practice, applicable standards and approvals. Hendon accepts no responsibility for incorrect or non-compliant use of its products, failure to meet appropriate standards and approvals in the application of Hendon products, or for the correct engineering choice of other connected components, layout and operation of Hendon products.

Any customer purchasing or using Hendon product(s) for an unintended or unauthorised application shall indemnify and hold Hendon and its officers, employees, related companies, affiliates and distributors harmless against all claims, costs, damages, expenses, and reasonable legal fees arising out of, directly or indirectly, any claim of loss, personal injury or death associated with such unintended or unauthorised use, even if such claim alleges that Hendon was negligent regarding the design or manufacture of the relevant product(s).

#### Life Support Applications

Products of Hendon Semiconductors (Hendon) are not designed for use in life support appliances, devices or systems, where malfunction can result in personal injury. Customers using or selling Hendon products for use in such applications do so at their own risk and agree to fully indemnify Hendon for any damages resulting from such improper use or sale.