### Description

The  $\mu$ PD4363B is a 16,384-word by 4-bit static RAM fabricated with advanced silicon-gate technology. A unique design using CMOS peripheral circuits and N-channel memory cells with polysilicon resistors makes the  $\mu$ PD4363B a high-speed device that requires very low power and no clock or refreshing.

The  $\mu$ PD4363B is packaged in a standard 300-mil, 24-pin plastic DIP and 24-pin plastic SOJ.

### **Features**

- □ Single + 5-volt power supply

- Fully static operation—no clock or refreshing

- □ TTL-compatible inputs and outputs

- □ Common I/O capability

- □ OE eliminates the need for external bus buffers

- □ Three-state outputs

- Low power dissipation

- 130 mA max (active)

- -2 mA max (standby)

- Standard 300-mil, 24-pin plastic DIP and 24-pin plastic SOJ packaging

### Ordering Information

| Part Number   | Access Time (max) | Package            |  |  |

|---------------|-------------------|--------------------|--|--|

| μPD4363BCR-12 | 12 ns             | 24-pin plastic DIP |  |  |

| CR-15         | 15 ns             | •                  |  |  |

| CR-20         | 20 ns             | -                  |  |  |

| μPD4363BLA-12 | 12 ns             | 24-pin plastic SO  |  |  |

| LA-15         | 15 ns             | _                  |  |  |

| LA-20         | 20 ns             | •                  |  |  |

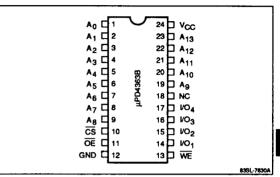

### Pin Configuration

#### 24-Pin Plastic DIP or SOJ

### Pin Identification

| Address inputs          |

|-------------------------|

|                         |

| Data inputs and outputs |

| Chip select             |

| Output enable           |

| Write enable            |

| Ground                  |

| +5-volt power supply    |

| No connection           |

|                         |

**Absolute Maximum Ratings**

| Supply voltage, V <sub>CC</sub>                     | - 0.5 to + 7.0 V                |

|-----------------------------------------------------|---------------------------------|

| Input and output voltages, V <sub>IN</sub> (Note 1) | -0.5 to V <sub>CC</sub> + 0.5 V |

| Operating temperature, T <sub>OPR</sub>             | 0 to +70°C                      |

| Storage temperature, T <sub>STG</sub>               | - 55 to + 125°C                 |

| Power dissipation, PD                               | 1.0 W                           |

Exposure to Absolute Maximum Ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should be operated within the limits specified under DC and AC Characteristics.

#### Notes:

(1)  $V_{\text{IN}}$  (min) = -3.0 V for 10 ns pulse.

### Capacitance

$T_A = 25^{\circ}C$ ; f = 1 MHz;  $V_{IN}$  and  $V_{OUT} = 0$  V (Note 1)

| Parameter          | Symbol            | Min | Тур | Max | Unit |

|--------------------|-------------------|-----|-----|-----|------|

| Input capacitance  | CIN               |     |     | 6   | pF   |

| Output capacitance | C <sub>DOUT</sub> |     |     | 8   | pF   |

#### Notes:

(1) This parameter is sampled and not 100% tested.

## **Recommended Operating Conditions**

| Parameter             | Symbol          | Min   | Тур | Max                   | Unit |  |

|-----------------------|-----------------|-------|-----|-----------------------|------|--|

| Supply voltage        | Vcc             | 4.5   | 5.0 | 5.5                   | ٧    |  |

| Input voltage, high   | VIH             | 2.2   |     | V <sub>CC</sub> + 0.3 | ٧    |  |

| Input voltage, low    | V <sub>IL</sub> | - 0.5 |     | 0.8                   | ٧    |  |

| Operating temperature | TA              | 0     |     | 70                    | °C   |  |

#### Notes:

(2)  $V_{IL} = -3.0 \text{ V}$  for 10 ns pulse.

### **Truth Table**

| Function                  | CS | WE | ŎĔ | Input/Output     | lcc     |

|---------------------------|----|----|----|------------------|---------|

| Not selected              | Н  | Х  | Х  | High-Z           | Standby |

| Read                      | L  | Н  | L  | D <sub>OUT</sub> | Active  |

| D <sub>OUT</sub> disabled | L  | Н  | Н  | High-Z           | Active  |

| Write                     | L  | L  | X  | D <sub>IN</sub>  | Active  |

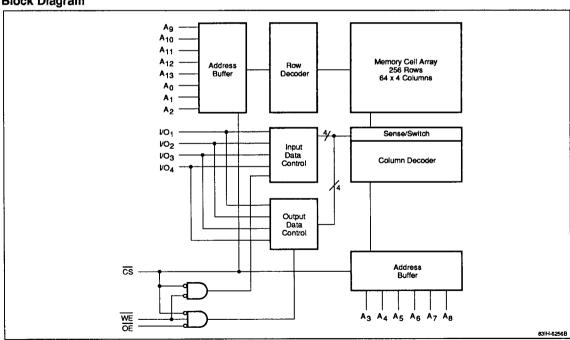

**Block Diagram**

#### **DC Characteristics**

$T_A = 0 \text{ to } +70^{\circ}\text{C}; V_{CC} = +5.0 \text{ V } \pm 10\%$

| Symbol           | Min                                                                              | Тур | Max | Unit            | Test Conditions                                                                                                                                                       |

|------------------|----------------------------------------------------------------------------------|-----|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ILI              | -2                                                                               |     | 2   | μΑ              | V <sub>IN</sub> = 0 V to V <sub>CC</sub> ; V <sub>CC</sub> = max                                                                                                      |

| lιο              | -2                                                                               |     | 2   | μΑ              | V <sub>OUT</sub> = 0 V to V <sub>CC</sub> ; $\overline{\text{CS}}$ or $\overline{\text{OE}}$ = V <sub>IH</sub> ; V <sub>CC</sub> = max                                |

| Isa              |                                                                                  |     | 20  | mA              | CS = VIH                                                                                                                                                              |

| l <sub>SB1</sub> |                                                                                  |     | 2   | mA              | $\overline{\text{CS}} = V_{\text{CC}} - 0.2 \text{V}; V_{\text{IN}} \le 0.2 \text{V or} \ge V_{\text{CC}} - 0.2 \text{V}$                                             |

| VoL              |                                                                                  |     | 0.4 | ٧               | l <sub>OL</sub> = 8.0 mA                                                                                                                                              |

| V <sub>он</sub>  | 2.4                                                                              |     |     | V               | I <sub>OH</sub> = -4.0 mA                                                                                                                                             |

|                  | I <sub>LI</sub> I <sub>LO</sub> I <sub>SB</sub> I <sub>SB1</sub> V <sub>OL</sub> | L1  |     | I <sub>L1</sub> | I <sub>L1</sub> -2     2     μA       I <sub>LO</sub> -2     2     μA       I <sub>SB</sub> 20     mA       I <sub>SB1</sub> 2     mA       V <sub>OL</sub> 0.4     V |

## **AC Characteristics**

$T_A = 0 \text{ to } +70^{\circ}\text{C}; V_{CC} = +5.0 \text{ V } \pm 10\%$

| Parameter                          | Symbol          | μPD4363B-12 |             | μPD4363B-15 |     | μPD4363B-20 |     |      |                                                 |

|------------------------------------|-----------------|-------------|-------------|-------------|-----|-------------|-----|------|-------------------------------------------------|

|                                    |                 | Min         | Max         | Min         | Max | Min         | Max | Unit | Test Conditions                                 |

| Read Operation                     |                 |             |             |             |     |             |     |      |                                                 |

| Operating supply current           | lcc             |             | 130         |             | 120 |             | 110 | mΑ   | CS = V <sub>IL</sub> ; I <sub>DOUT</sub> = 0 mA |

| Read cycle time                    | tRC             | 12          |             | 15          |     | 20          |     | ns   | (Note 2)                                        |

| Address access time                | t <sub>AA</sub> |             | 12          |             | 15  | -           | 20  | ns   |                                                 |

| Chip select access time            | tacs            |             | 12          |             | 15  |             | 20  | ns   |                                                 |

| Output hold from address change    | tон             | 2           |             | 3           |     | 3           |     | ns   |                                                 |

| Chip select to output in low-Z     | t <sub>LZ</sub> | 2           |             | 3           |     | 3           |     | ns   | (Note 3)                                        |

| Chip deselect to output in high-Z  | tHZ             | 0           | 7           | 0           | 7   | 0           | 8   | ns   | (Note 4)                                        |

| Output enable access time          | †0E             |             | 8           |             | 9   |             | 10  | ns   |                                                 |

| Output enable to output in low-Z   | toLZ            | 0           |             | 0           |     | 0           |     | ns   | (Note 3)                                        |

| Output disable to output in high-Z | tонz            | 0           | 7           | 0           | 7   | 0           | 8   | ns   | (Note 4)                                        |

| Chip select to power-up time       | t <sub>PU</sub> | 0           |             | 0           |     | 0           |     | ns   |                                                 |

| Chip deselect to power-down time   | t <sub>PD</sub> | 0           | 7           | 0           | 10  | 0           | 12  | ns   |                                                 |

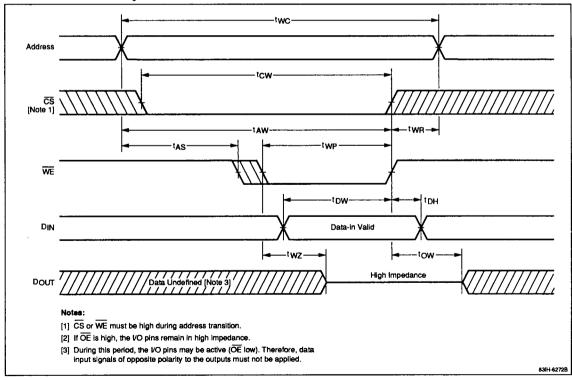

| Write Operation                    |                 |             |             |             |     |             |     |      |                                                 |

| Write cycle time                   | twc             | 12          | ···         | 15          |     | 20          |     | ns   | (Note 2)                                        |

| Chip select to end of write        | tcw             | 11          |             | 13          |     | 15          |     | ns   |                                                 |

| Address valid to end of write      | t <sub>AW</sub> | 11          |             | 13          |     | 15          |     | ns   |                                                 |

| Address setup time                 | tas             | 0           |             | 0           |     | 0           |     | ns   |                                                 |

| Write pulse width                  | t <sub>WP</sub> | 10          |             | 12          |     | 14          |     | ns   |                                                 |

| Write recovery time                | twR             | 1           |             | 1           |     | 1           |     | ns   |                                                 |

| Data valid to end of write         | t <sub>DW</sub> | 7           |             | 7           |     | 8           |     | ns   |                                                 |

| Data hold time                     | t <sub>DH</sub> | 0           |             | 0           |     | 0           |     | ns   | -                                               |

| Write enable to output in high-Z   | twz             | 0           | 7           | 0           | 7   | 0           | 8   | ns   | (Note 4)                                        |

| Output active from end of write    | tow             | 0           | <del></del> | 0           |     | 0           |     | ns   | (Note 3)                                        |

#### Notes:

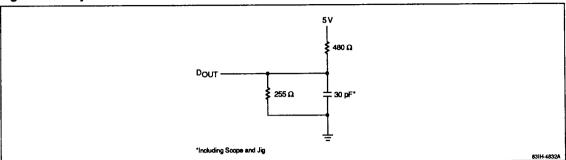

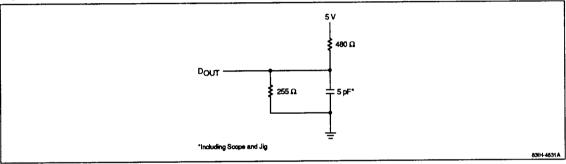

- Input pulse levels = GND to 3.0 V; input pulse rise and fall times = 5 ns; timing reference levels = 1.5 V; see figures 1 and 2 for output load.

- (2) All read and write cycle timings are referenced from the last valid address to the first transitioning address.

- (3) Transition is measured at ±200 mV from steady-state voltage with the loading shown in figure 2.

- (4) Transition is measured at  $V_{OL}$  + 200 mV and  $V_{OH}$  200 mV with the loading shown in figure 2.

Figure 1. Output Load

Figure 2. Output Load for  $t_{HZ}$ ,  $t_{LZ}$ ,  $t_{OHZ}$ ,  $t_{OLZ}$ ,  $t_{WZ}$ , and  $t_{OW}$

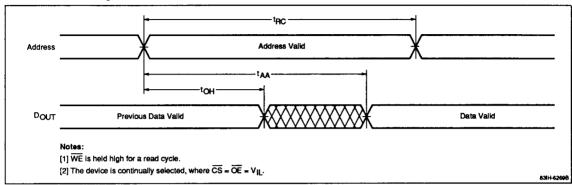

# **Timing Waveforms (cont)**

### Address Access Cycle

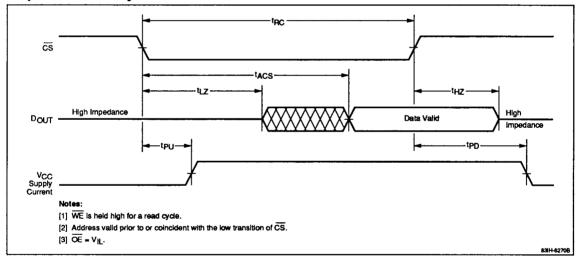

# Chip Select Access Cycle

# **Timing Waveforms (cont)**

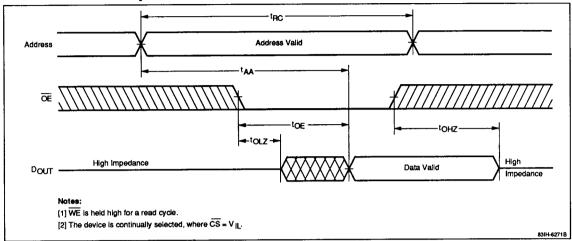

## **OE-Controlled Access Cycle**

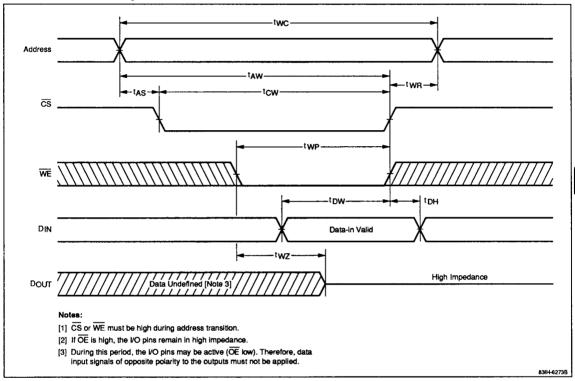

### WE-Controlled Write Cycle

## **Timing Waveforms (cont)**

# **CS-Controlled Write Cycle**