# VERY LOW POWER 3.3V CMOS FAST SRAM 1 MEG (128K x 8-BIT)

ADVANCE INFORMATION IDT713024SL

#### **FEATURES:**

- 128K x 8 advanced high-speed CMOS Static RAM

- · Equal access and cycle times

- Commercial: 20/25ns

- True 3.3V design, not a re-characterized 5V device

- Ideal for battery-operated equipment, including notebook computers, portable instruments, and portable communications devices

- · Low standby currents and 2V data retention mode

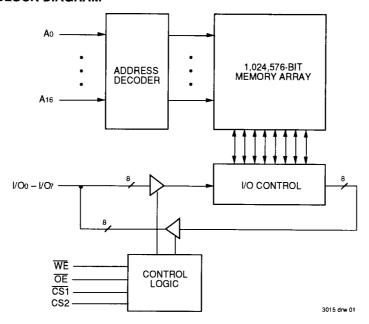

- · Two Chip Selects plus one Output Enable pin

- · Bidirectional inputs and outputs directly TTL-compatible

- Compliant with all JEDEC LVTTL standard specifications

Single 3.3 V/40.3 V/ payers and the specifications

- Single 3.3V (±0.3V) power supply, resulting in 57% dynamic power savings over equivalent 5 volt devices

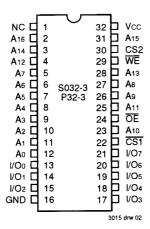

- · Available in 400 mil plastic DIP and plastic SOJ packages

### **DESCRIPTION:**

The IDT713024SL is a 1,024,576-bit high-speed Static RAM organized as  $128K \times 8$ . It is fabricated using IDT's high-

perfomance, high-reliability 3.3V CMOS technology. This state-of-the-art technology, combined with innovative circuit design techniques, results in a unique combination of speed and low power consumption, with only a 3.3V supply.

Unlike re-characterized 5V devices, the IDT713024SL is the result of a dedicated 3.3V design, which ensures full compliance with the JEDEC LVTTL standard of operation in terms of thresholds and noise margins. This dedicated 3.3V technology also allows for a faster device.

The IDT713024SL has address access times as fast as 20ns. All bidirectional inputs and outputs are TTL-compatible and operation is from a single 3.3V supply.

This SRAM offers a very low standby current, as well as a data retention mode that guarantees that data be preserved at voltages as low as 2 volts. These characteristics make the IDT713024SL ideal for high-performance applications that are powered by batteries, as well as AC-powered systems that need to minimize power consumption.

The IDT713024SL is packaged in a 32-pin 400 mil plastic DIP, and a 32-pin 400 mil plastic SOJ.

## **FUNCTIONAL BLOCK DIAGRAM**

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

**COMMERCIAL TEMPERATURE RANGE**

SEPTEMBER 1992

## PIN CONFIGURATION

DIP/SOJ **TOP VIEW**

## TRUTH TABLE(1,2)

| INPUTS |                    |                    |    |         |                           |

|--------|--------------------|--------------------|----|---------|---------------------------|

| WE     | CS1                | CS2                | OE | 1/0     | FUNCTION                  |

| Х      | Н                  | Х                  | Х  | High-Z  | Deselected-Standby (ISB)  |

| Х      | Vнс <sup>(3)</sup> | Х                  | Х  | High-Z  | Deselected-Standby (ISB1) |

| Х      | Х                  | L                  | Х  | High-Z  | Deselected-Standby (ISB)  |

| Х      | Х                  | VLC <sup>(3)</sup> | Х  | High-Z  | Deselected-Standby (ISB1) |

| Н      | L                  | Н                  | Н  | High-Z  | Outputs Disabled          |

| Н      | L                  | Н                  | L  | DATAOUT | Read Data                 |

| L      | L                  | Н                  | Х  | DATAIN  | Write Data                |

#### NOTES:

3015 tbl 01

- H = VIH, L = VIL, X = Don't care.

VLC = 0.2V, VHC = VCC -0.2V.

- 3. Other inputs ≥VHC or ≤VLC.