54ACT112

OBSOLETE July 20, 2009

# **Dual JK Negative Edge-Triggered Flip-Flop**

### **General Description**

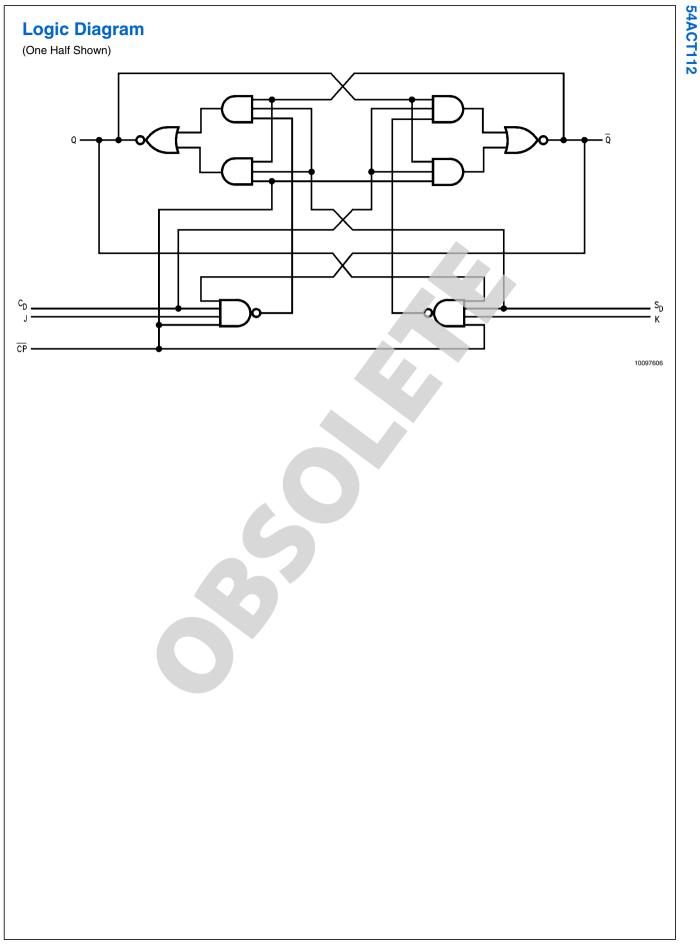

The 'ACT112 contains two independent, high-speed JK flipflops with Direct Set and Clear inputs. Synchronous state changes are initiated by the falling edge of the clock. Triggering occurs at a voltage level of the clock and is not directly related to the transition time. The J and K inputs can change when the clock is in either state without affecting the flip-flop, provided that they are in the desired state during the recommended setup and hold times relative to the falling edge of the clock. A LOW signal on  $\overline{S}_D$  or  $\overline{C}_D$  prevents clocking and forces Q or  $\overline{Q}$  HIGH, respectively. Simultaneous LOW signals on  $\overline{S}_D$  and  $\overline{C}_D$  force both Q and  $\overline{Q}$  HIGH.

Asynchronous Inputs:

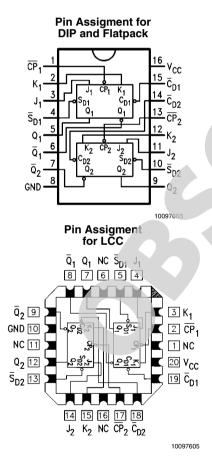

### **Connection Diagrams**

LOW input to  $\overline{S}_D$  sets Q to HIGH level LOW input to  $\overline{C}_D$  sets Q to LOW level Clear and Set are independent of clock Simultaneous LOW on  $\overline{C}_D$  and  $\overline{S}_D$  makes both Q and  $\overline{Q}$ HIGH

### **Features**

- 'ACT112 has TTL-compatible inputs

- Outputs source/sink 24 mA

- Standard Microcircuit Drawing (SMD) 5962-8995001

### **Pin Descriptions**

| Pin Names                                                                       | Description                      |

|---------------------------------------------------------------------------------|----------------------------------|

| <b>J</b> <sub>1</sub> , J <sub>2</sub> , <b>K</b> <sub>1</sub> , K <sub>2</sub> | Data Inputs                      |

| $\overline{CP}_1, \overline{CP}_2$                                              | Clock Pulse Inputs               |

|                                                                                 | (Active Falling Edge)            |

| $\overline{C}_{D1}, \overline{C}_{D2}$                                          | Direct Clear Inputs (Active LOW) |

| $\overline{S}_{D1}, \overline{S}_{D2}$                                          | Direct Set Inputs (Active LOW)   |

| $Q_1, Q_2, \overline{Q}_1, \overline{Q}_2$                                      | Outputs                          |

FACT™ is a trademark of Fairchild Semiconductor

# 54ACT112

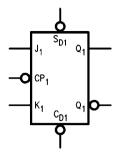

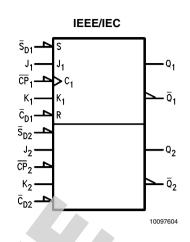

### Logic Symbols

10097601

S<sub>D2</sub>  $Q_2$ J<sub>2</sub> CP2 Q2 К2 C<sub>D2</sub> 10097602

### **Truth Table**

|                       |     | Inputs |   |   | Out                | puts                        |

|-----------------------|-----|--------|---|---|--------------------|-----------------------------|

| <b>S</b> <sub>D</sub> | CD  | CP     | J | К | Q                  | Q                           |

| L                     | Н   | Х      | Х | Х | Н                  | L                           |

| Н                     | L   | Х      | Х | Х | L                  | Н                           |

| L                     | L   | X      | Х | Х | н                  | Н                           |

| H                     | Н   | М      | h | h | $\overline{Q}_{0}$ | $Q_0$                       |

| Н                     | Η / | Μ      | Ι | h | L                  | н                           |

| н                     | Н   | М      | h | Ι | н                  | L                           |

| Н                     | н   | М      | Ι | Ι | Q <sub>0</sub>     | $\overline{\mathbf{Q}}_{0}$ |

H (h) = HIGH Voltage Level L (l) = LOW Voltage Level

X = Immaterial

$\begin{array}{l} A = \text{HIGH} \\ M = \text{HIGH-to-LOW Clock Transition} \\ Q_0 \ (\overline{Q}_0) = \text{Before HIGH-to-LOW Transition of Clock} \\ \text{Lower case letters indicate the state of the referenced input or output one setup time prior to the HIGH-to-LOW clock transition. } \end{array}$

### Absolute Maximum Ratings (Note 1)

### If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage (V <sub>CC</sub> )                     | -0.5V to +7.0V                  |

|-------------------------------------------------------|---------------------------------|

| DC Input Diode Current (I <sub>IK</sub> )             |                                 |

| $V_{I} = -0.5V$                                       | –20 mA                          |

| $V_{\rm I} = V_{\rm CC} + 0.5 V$                      | +20 mA                          |

| DC Input Voltage (VI)                                 | -0.5V to V <sub>CC</sub> + 0.5V |

| DC Output Diode Current (I <sub>OK</sub> )            |                                 |

| $V_{O} = -0.5V$                                       | –20 mA                          |

| $V_{O} = V_{CC} + O.5$                                | +20 mA                          |

| DC Output Voltage (V <sub>O</sub> )                   | –0.5V to V <sub>CC</sub> +0.5V  |

| DC Output Source                                      |                                 |

| or Sink Current (I <sub>O</sub> )                     | ±50 mA                          |

| DC V <sub>CC</sub> or Ground Current                  |                                 |

| per Output Pin (I <sub>CC</sub> or I <sub>GND</sub> ) | ±50 mA                          |

| Storage Temperature (T <sub>STG</sub> )               | –65°C to +150°C                 |

| Junction Temperature $(T_J)$                          |                                 |

| CDIP                                                  | 175°C                           |

# Recommended Operating Conditions

| Supply Voltage (V <sub>CC</sub> )       | 4.5V to 5.5V          |

|-----------------------------------------|-----------------------|

| Input Voltage (V <sub>I</sub> )         | 0V to V <sub>CC</sub> |

| Output Voltage (V <sub>O</sub> )        | 0V to V <sub>CC</sub> |

| Operating Temperature (T <sub>A</sub> ) | –55°C to +125°C       |

| Minimum Input Edge Rate (ΔV/Δt)         | 125 mV/ns             |

| V <sub>IN</sub> from 0.8V to 2.0V       |                       |

| V <sub>CC</sub> @ 4.5V, 5.5V            |                       |

**Note 1:** Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. Fairchild does not recommend operation of FACT<sup>TM</sup> circuits outside databook specifications.

### **DC Characteristics for 'ACT Family Devices**

| Symbol           | Parameter V <sub>CC</sub>           |     | T <sub>A</sub> = -55°C to +125°C | Units | Conditions                           |

|------------------|-------------------------------------|-----|----------------------------------|-------|--------------------------------------|

|                  |                                     | (V) | Guaranteed Limits                |       |                                      |

| V <sub>IH</sub>  | Minimum High Level                  | 4.5 | 2.0                              | V     | V <sub>OUT</sub> = 0.1V              |

|                  | Input Voltage                       | 5.5 | 2.0                              |       | or V <sub>CC</sub> – 0.1V            |

| V <sub>IL</sub>  | Maximum Low Level                   | 4.5 | 0.8                              | V     | $V_{OUT} = 0.1V$                     |

|                  | Input Voltage                       | 5.5 | 0.8                              |       | or V <sub>CC</sub> – 0.1V            |

| V <sub>OH</sub>  | Minimum High Level                  | 4.5 | 4.4                              | V     | I <sub>OUT</sub> = -50 μA            |

|                  | Output Voltage                      | 5.5 | 5.4                              |       |                                      |

|                  |                                     |     |                                  |       | $V_{IN} = V_{IL}$ or $V_{IH}$        |

|                  |                                     | 4.5 | 3.70                             | V     | I <sub>OH</sub> = -24 mA             |

|                  |                                     | 5.5 | 4.70                             |       | I <sub>OH</sub> = -24 mA             |

|                  |                                     |     |                                  |       | (Note 2)                             |

| V <sub>OL</sub>  | Maximum Low Level                   | 4.5 | 0.1                              | V     | Ι <sub>ουτ</sub> = 50 μΑ             |

|                  | Output Voltage                      | 5.5 | 0.1                              |       |                                      |

|                  |                                     |     |                                  |       | $V_{IN} = V_{IL} \text{ or } V_{IH}$ |

|                  |                                     | 4.5 | 0.5                              | V     | I <sub>OL</sub> = 24 MA              |

|                  |                                     | 5.5 | 0.5                              |       | I <sub>OL</sub> = 24 mA              |

|                  |                                     |     |                                  |       | (Note 2)                             |

| I <sub>IN</sub>  | Maximum Input Leakage Current       | 5.5 | ± 1.0                            | μA    | $V_{I} = V_{CC}, GND$                |

| I <sub>CCT</sub> | Maximum I <sub>CC</sub> /Input      | 5.5 | 1.6                              | mA    | $V_{I} = V_{CC} - 2.1V$              |

| I <sub>OLD</sub> | Minimum Dynamic                     | 5.5 | 50                               | mA    | V <sub>OLD</sub> = 1.65V Max         |

| I <sub>OHD</sub> | Output Current(Note 3)              | 5.5 | -50                              | mA    | V <sub>OHD</sub> = 3.85V Min         |

| I <sub>cc</sub>  | Maximum Quiescent Supply<br>Current | 5.5 | 80.0                             | μA    | $V_{IN} = V_{CC}$ or GND             |

Note 2: All outputs loaded; thresholds on input associated with output under test.

Note 3: Maximum test duration 2.0 ms, one output loaded at a time.

### **AC Electrical Characteristics for 'ACT Family Devices**

| Symbol | Parameter                                                               | V <sub>cc</sub><br>(V) | T <sub>A</sub> = −55°C to +125°C<br>C <sub>L</sub> = 50 pF |      | Units | Fig. No. |

|--------|-------------------------------------------------------------------------|------------------------|------------------------------------------------------------|------|-------|----------|

|        |                                                                         | (Note 4)               | Min                                                        | Max  |       |          |

| max    | Maximum Clock                                                           | 5.0                    | 80                                                         |      | MHz   |          |

|        | Frequency                                                               |                        |                                                            |      |       |          |

| PLH    | Propagation Delay                                                       | 5.0                    | 1.0                                                        | 14.0 | ns    |          |

|        | $CP_n$ to $Q_n$ or $\overline{Q}_n$                                     |                        |                                                            |      |       |          |

| PHL    | Propagation Delay                                                       | 5.0                    | 1.0                                                        | 14.0 | ns    |          |

|        | $CP_n$ to $Q_n$ or $\overline{Q}_n$                                     |                        |                                                            |      |       |          |

| PLH    | Propagation Delay                                                       | 5.0                    | 1.0                                                        | 13.5 | ns    |          |

|        | $\overline{C}_{Dn}$ or $\overline{S}_{Dn}$ to $Q_n$ or $\overline{Q}_n$ |                        |                                                            |      |       |          |

| PHL    | Propagation Delay                                                       | 5.0                    | 1.0                                                        | 13.5 | ns    |          |

|        | $\overline{C}_{Dn}$ or $\overline{S}_{Dn}$ to $Q_n$ or $\overline{Q}_n$ |                        |                                                            |      |       |          |

Note 4: Voltage Range 5.0 is 5.0V ±0.5V

### **AC Operating Requirements:**

| Symbol           | Parameter                                                             | V <sub>cc</sub><br>(V)<br>(Note 5) | $T_A = -55^{\circ}C \text{ to } +125^{\circ}C$<br>$C_L = 50 \text{ pF}$<br>Guaranteed Minimum | Units | Fig. No. |

|------------------|-----------------------------------------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------|-------|----------|

| t <sub>S</sub>   | Setup Time, HIGH or LOW $J_n$ or $\overline{K}_n$ to $CP_n$           | 5.0                                | 8.0                                                                                           | ns    |          |

| t <sub>H</sub>   | Hold Time, HIGH or LOW $J_n$ or $\overline{K}_n$ to $CP_n$            | 5.0                                | 1.5                                                                                           | ns    |          |

| t <sub>W</sub>   | Pulse Width $CP_n$ or $\overline{C}_{Dn}$ or $\overline{S}_{Dn}$      | 5.0                                | 5.0                                                                                           | ns    |          |

| t <sub>rec</sub> | Recovery Time<br>$\overline{C}_{Dn}$ or $\overline{S}_{Dn}$ to $CP_n$ | 5.0                                | 3.0                                                                                           | ns    |          |

Note 5: Voltage Range 5.0 is  $5.0V \pm 0.5V$

## Capacitance

| Symbol          | Parameter                     | Мах  | Units | Conditions             |

|-----------------|-------------------------------|------|-------|------------------------|

| C <sub>IN</sub> | Input Capacitance             | 10.0 | pF    | V <sub>CC</sub> = OPEN |

| C <sub>PD</sub> | Power Dissipation Capacitance | 60   | pF    | $V_{CC} = 5.0V$        |

54ACT112

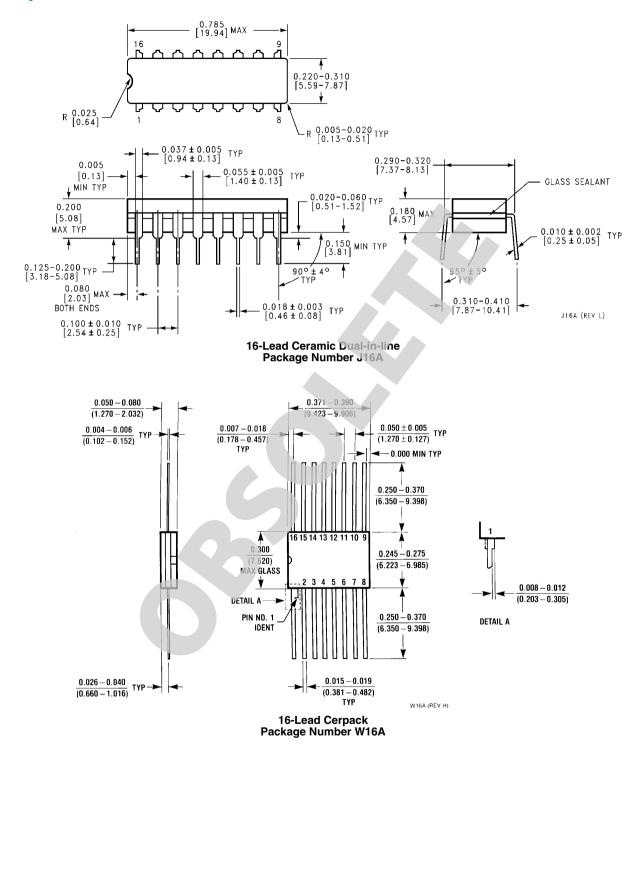

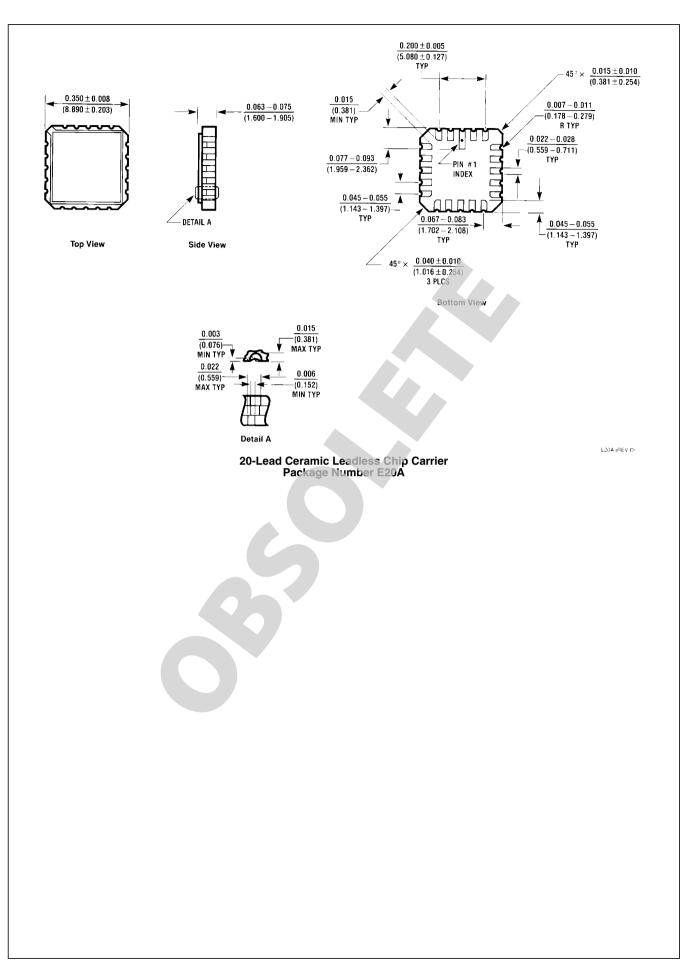

### Physical Dimensions inches (millimeters) unless otherwise noted

54ACT112

www.national.com

54ACT112

# Notes

| Flip-Fl  |                                      |

|----------|--------------------------------------|

| red      | For more National Sen                |

| ge       |                                      |

| ig       | Amplifiers                           |

|          | Audio                                |

| 4        | Clock and Timing                     |

| ð        | Data Converters                      |

| БП       | Interface                            |

| 6        | LVDS                                 |

| <u> </u> | Power Management                     |

| at       | Switching Regula                     |

| 0        | LDOs                                 |

| Ne       | LED Lighting                         |

| X        | Voltage Referen                      |

|          | PowerWise® Solution                  |

| a        | Serial Digital Interface             |

|          | Temperature Sensors                  |

| 2        | Wireless (PLL/VCO)                   |

| -        | THE CONTENTS OF T                    |

| 4ACT     | ("NATIONAL") PRODU                   |

| Ă        | OR COMPLETENESS<br>SPECIFICATIONS AN |

| 4        | IMPLIED, ARISING B                   |

Ω.

miconductor product information and proven design tools, visit the following Web sites at:

| Pr                             | oducts                       | Design Support                  |                                |  |

|--------------------------------|------------------------------|---------------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools                  | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | App Notes                       | www.national.com/appnotes      |  |

| Clock and Timing               | www.national.com/timing      | Reference Designs               | www.national.com/refdesigns    |  |

| Data Converters                | www.national.com/adc         | Samples                         | www.national.com/samples       |  |

| Interface                      | www.national.com/interface   | Eval Boards                     | www.national.com/evalboards    |  |

| LVDS                           | www.national.com/lvds        | Packaging                       | www.national.com/packaging     |  |

| Power Management               | www.national.com/power       | Green Compliance                | www.national.com/quality/green |  |

| Switching Regulators           | www.national.com/switchers   | Distributors                    | www.national.com/contacts      |  |

| LDOs                           | www.national.com/ldo         | Quality and Reliability         | www.national.com/quality       |  |

| LED Lighting                   | www.national.com/led         | Feedback/Support                | www.national.com/feedback      |  |

| Voltage Reference              | www.national.com/vref        | Design Made Easy                | www.national.com/easy          |  |

| PowerWise® Solutions           | www.national.com/powerwise   | Solutions                       | www.national.com/solutions     |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                        | www.national.com/milaero       |  |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                     | www.national.com/solarmagic    |  |

| Wireless (PLL/VCO)             | www.national.com/wireless    | PowerWise® Design<br>University | www.national.com/training      |  |

THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ICTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO ID PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS, PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS. NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

### Copyright© 2009 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com ww.national.com Tel: 1-800-272-9959

National Semiconductor Europe **Technical Support Center** Email: europe.support@nsc.com

National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com

National Semiconductor Japan **Technical Support Center** Email: ipn.feedback@nsc.com