### **Features**

- Improved Accuracy and Ruggedness Over The 7541

- 12 Bit Endpoint Linearity (± 1/2 LSB)

- Improved Gain Error: ± 1 LSB (No User Adjustment Required)

- Low Gain Tempco (5 ppm/°C Max)

- 2 and 4 Quadrant Multiplication

- Superior Power Supply Rejection.

- Low Feedthrough Error and Digital Charge Injection.

- Low Power Consumption.

- TTL/CMOS Compatible

- All Data Input Pins Designed To withstand 200IV ESD

- Direct Replacement for AD 7541 and AD 7541 A.

## **Applications**

- · Programmable Amplifiers

- Function Generators

- · Digitally Controlled Attenuators

- · Digitally Controlled Power Supplies

- Digital Filters

- Digital/Synchro Conversion

- Ratiometric A/D Conversion

- CRT Graphics Generator

### Description

The HS-7541A is a 12-Bit, 4 quadrant multiplying digital-to-analog converter contained in a single high density monolithic CMOS chip. It is manufactured using an advanced oxide isolated, silicon-gate, monolithic CMOS technology.

The HS-7541A features circuitry designed to protect data inputs against damage from 2001 volt electrostatic discharge.

The HS-7541A consists of a highly stable thinfilm R-2R ladder network and twelve NMOS current switches on a monolithic chip. The thin-film resistors are laser trimmed to provide true 12 Bit linearity and excellent absolute linearity. The NMOS switches are temperature compensating and their "ON" resistances are binarily scaled so that the voltage drop across each switch is identical. This is essential in maintaining the accuracy of the binarily weighted current division performed by the ladder network. The internal feedback resistor used in the output current-to-voltage conversion operation is matched to the R-2R ladder.

The HS-7541A is a superior pin-compatible replacement for the industry standard 7541 and the AD7541A. Available in standard Epoxy and CERDIP packages, the HS-7541A is compatible with automatic insertion equipment. The improved performance of the HS-7541A permits upgrading existing designs with greater ruggedness and accuracy. Tight linearity and gain error specifications may permit reduced system parts count by eliminating trimming circuitry.

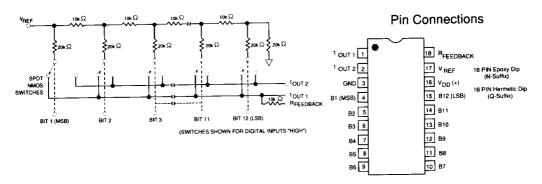

### Functional Diagram

# HS-7541A

CMOS 12-Bit Multiplying DAC

| Absolute | Maximum | Ratings |

|----------|---------|---------|

|----------|---------|---------|

| Absolute Maximum Ratings                      |                           | Operating Temper                       | erature Range (T <sub>A</sub> = Full)                 |                                                   |

|-----------------------------------------------|---------------------------|----------------------------------------|-------------------------------------------------------|---------------------------------------------------|

| (T <sub>A</sub> =+25°C, unless otherwise note | d)                        | Commerical<br>Industrial<br>Military   | (KN ,LN GRADES)<br>(BQ, CQ GRADES)<br>(TQ, UQ GRADES) | 0° C to 70°C<br>-25°C to +85°C<br>-55°C to +125°C |

| V <sub>pp</sub> (to GND)                      | +17V                      | ······································ | (14,04 3.1.122)                                       | ••••                                              |

| V <sub>REF</sub> (to GND)                     | ±25V                      | Dice Junction Te                       | mperature                                             | +150°C                                            |

| V <sub>REB</sub> (to GND)                     | ±25V                      | Storage Tempera                        | •                                                     | -65°C to +150°C                                   |

| Digital Input Voltage Range                   | V <sub>pp</sub> to GND    | Lead Temperatur                        | re (Soldering, 60 Sec)                                | +300°C                                            |

| Output Voltage (Pin 1, Pin 2)                 | -0.3V, to V <sub>nn</sub> |                                        | tages higher than $V_{DD}$ or le                      | ess than GND                                      |

| Power Dissipation (Package)                   | 450mW                     |                                        | terminal except V <sub>REF</sub> .                    |                                                   |

| Derate Above +75°C                            | 6mW/°C                    | Use proper ESD                         | handling procedures                                   |                                                   |

**Electrical Characteristics:**  $V_{DD}$  =+15V,  $V_{REF}$  = +10V,  $V_{OUT 1}$  =  $V_{OUT 2}$  = 0V;  $T_A$  = Full unless otherwise noted.

| Parameters                                                      | Symbol            | Conditions                                                                                                                                                    | Min | Тур                            | Max                 | Units                    |

|-----------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------|---------------------|--------------------------|

| STATIC ACCURACY                                                 |                   |                                                                                                                                                               |     |                                |                     |                          |

| Resolution<br>Nonlinearity                                      | N<br>INL          |                                                                                                                                                               | 12  |                                | ± 1/2               | Bits<br>LSB              |

| Differential<br>NonLinearity                                    | DNL               | HS-7541A - KN/BQ/TQ<br>HS-7541A - JN/AQ/SQ                                                                                                                    |     |                                | ± 1/2<br>± 1        | LSB<br>LSB               |

| Gain Error                                                      | G <sub>FSE</sub>  | Using Internal Feedback Resistor HS-7541A - KN/BQ/TQ $T_A=25^{\circ}C$ $T_A=Full$ HS-7541A - JN/AQ/SQ $T_A=5^{\circ}C$ $T_A=Full$                             |     |                                | 1<br>2<br>2<br>3    | LSB<br>LSB<br>LSB        |

| GAIN TEMPCO<br>(Δ Gain/Δ Temp.)                                 | TC <sub>GFS</sub> |                                                                                                                                                               |     | ±2                             | ± 5                 | PPM/°C                   |

| Power Supply<br>Rejection Ratio<br>(Δ Gain/ Δ V <sub>DD</sub> ) | PSRR              | $T_{A} = 25^{\circ}\text{C}, \Delta V_{DD} = \pm 5\%$ $T_{A} = \text{Full}, \Delta V_{DD} = \pm 5\%$                                                          |     |                                | ±0.001<br>±0.002    | %/%<br>%/%               |

| Output Leakage<br>Current                                       | I <sub>LKG</sub>  | For $I_{OUT}$ , Digital Inputs = $V_{IL}$<br>HS-7541A - KN/BQ/TQ<br>$T_A=25^{\circ}C$<br>$T_A=Full$<br>HS-7541A - JN/AQ/SQ<br>$T_A=25^{\circ}C$<br>$T_A=Full$ |     |                                | 5<br>10<br>5<br>100 | NA<br>NA<br>NA<br>NA     |

| Zero Scale<br>Error                                             | Izse              | $V_{REF}$ =+10V, all digital inputs=0V HS-7541A - KN/BQ/TQ $T_A$ =25°C $T_A$ =Full HS-7541A- JN/AQ/SQ $T_A$ =°25C $T_A$ =Full                                 |     | 0.002<br>0.01<br>0.002<br>0.05 |                     | LSB<br>LSB<br>LSB<br>LSB |

**Electrical Characteristics:**  $V_{DD}$  =+15V,  $V_{REF}$  = +10V,  $V_{OUT 1}$  =  $V_{OUT 2}$  = 0V;  $T_A$  = Full unless otherwise noted.

| Parameters                                                | Symbol             | Conditions                                                                                                                          | Min | Тур                  | Max                    | Units                |

|-----------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------|------------------------|----------------------|

| Reference Input                                           |                    |                                                                                                                                     |     |                      |                        |                      |

| Input Resistance                                          | R <sub>PEF</sub>   |                                                                                                                                     | 7   | 11                   | 15                     | kΩ                   |

| Input Resistance<br>Tempco (Δ R/ΔT)                       | TC<br>R-REF        |                                                                                                                                     |     | 50                   |                        | ppm/°C               |

| Power Supply                                              |                    |                                                                                                                                     |     |                      |                        |                      |

| Supply Current                                            | l <sub>DD</sub>    | Digital Inputs = V <sub>IL</sub> OR V <sub>IH</sub><br>Digital Inputs = 0V or V <sub>DD</sub>                                       |     | 100                  | 2<br>μ A               | ma                   |

| Digital Input                                             |                    |                                                                                                                                     |     | ŀ                    |                        |                      |

| Digital Input High                                        | V <sub>IH</sub>    |                                                                                                                                     | 2.4 |                      |                        | \ \                  |

| Digital Input Low                                         | V <sub>IL</sub>    |                                                                                                                                     |     |                      | 0.8                    | \ \                  |

| Input Leakage<br>Current                                  | 1,                 | T <sub>A</sub> = 25°C<br>T <sub>A</sub> = Full                                                                                      |     | ±1                   | ± 1                    | NA<br>μA             |

| Input Capacitance                                         | C <sub>IN</sub>    | V <sub>IN</sub> = 0V                                                                                                                |     |                      | 8                      | PF                   |

| Dynamic Performance                                       | <b> </b>           |                                                                                                                                     |     |                      |                        |                      |

| Propagation Delay                                         | T <sub>PD</sub>    | $I_{OUT}$ LOAD = 100 $\Omega$ , $C_{EXT}$ = 13 PF, Measured Fom Digital Input Change to 90% Of Final Analog Output, $T_A$ = 25°C    |     | 100                  | 150                    | NS                   |

| Output Current<br>Settling Time                           | T <sub>s</sub>     | To ± 1/2 LSB, T <sub>A</sub> = 25°C<br>Extrapolated Measurement                                                                     |     | 0.6                  | 1                      | μS                   |

| Feedthrough Error (V <sub>REF</sub> to I <sub>OUT</sub> ) | FT                 | $V_{\rm REF}$ = 20 $V_{\rm PP}$ @ $f$ = 10 kHz<br>All Digital Inputs Low<br>TA = 25°C                                               |     | 2                    | 5                      | mV <sub>P-P</sub>    |

| Digital To Analog<br>Glitch Energy                        | Q                  | V <sub>REF</sub> = 0V, All Digital Inputs = 0V<br>To V <sub>DD</sub> Or V <sub>DD</sub> To 0V, T <sub>A</sub> = 25°C                |     | 700                  | 1000                   | NVS                  |

| Analog Outputs                                            |                    |                                                                                                                                     |     |                      |                        |                      |

| Output Capacitance                                        | C <sub>OUT 2</sub> | Digital Inputs = V <sub>IH</sub> Digital Inputs = V <sub>IL</sub> Digital Inputs = V <sub>IH</sub> Digital Inputs = V <sub>IL</sub> |     | 85<br>30<br>30<br>85 | 120<br>50<br>50<br>120 | PF<br>PF<br>PF<br>PF |

### **Circuit Description**

#### General

The HS7541A is a 12-bit multiplying D/A converter consisting of a highly stable, siliconchrome thin film R-2R resistor ladder network and twelve pairs of NMOS current steering switches on a monolithic chip. Most applications require the addition of a voltage or current reference and an output operational amplifier.

A simplified circuit of the HS754A1 is shown in Figure 1. The R-2R inverted ladder binarily divides the input currents that are switched between I  $_{\text{OUT}\,1}$  and I  $_{\text{OUT}\,2}$  bus lines. This switching allows a constant current to be maintained in each ladder leg independent of the input code.

The twelve output current-steering switches are in series with the R-2R resistor ladder, and therefore, can introduce bit errors. It is essential then, that the switch "ON" resistance be binarily scaled so that the voltage drop across each switch remains constant. If, for example, switch 1 of Figure 1 was designed with an "ON" resistance of 10 ohms, switch 2 for 20 ohms, etc., then with a 10 volt reference input, the current through switch 1 is 0.5mA, switch 2 is 0.25mA, etc., a constant 5mV drop will then be maintained across each switch.

To further insure accuracy across the full temperature range, permanently "ON" MOS switches are included in series with the feedback resistor and the R2-R ladder's terminating resistor. These series switches are equivalently scaled to two times switch 1 (MSB) and to switch 12 (LSB) respectively to maintain constant relative voltage drops with varying temperature. During any testing of the resistor ladder or  $R_{\text{FEEDBACK}}$  (such as incoming inspection)  $V_{\text{DD}}$  must be present to turn "ON" these series switches.

#### 2001 ESD Protection

In the design of the HS-7541A's data inputs, 2001 V ESD resistance has been incorporated through careful layout and the inclusion of input protection circuitry.

#### **Equivalent Circuit Analysis**

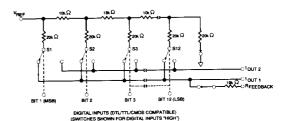

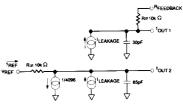

Figures 2 and 3 show the equivalent circuits for all digital inputs LOW and HIGH respectively. The reference current is switched to  $I_{\text{OUT}\,2}$  when

all inputs are LOW and I <sub>OUT 1</sub> when inputs are HIGH. The I <sub>LEAKAGE</sub> current source is the combination of surface and junction leakages to the substrate; the 1/4096 current source represents the constant 1-bit current drain through the ladder terminating resistor. The output capacitance is dependent upon the digital input code, and is therefore varied between the low and high values.

#### **Output Impedance**

The output resistance, as in the case of the output capacitance, varies with the digital input code. The resistance, looking back into the  $I_{\text{OUT}}$  terminal, may be anywhere between  $10 k\Omega$  (the feedback resistor alone when all digital inputs are low) and  $7.5 k\Omega$  (the feedback resistor in parallel with approximately  $30 k\Omega$  of the R-2R ladder network resistance when any single bit logic is high). Static accuracy and dynamic performance will be affected by these variations.

FIGURE 1: Simplified DAC Circuit

FIGURE 2: HS-7541A Equivalent Circuit

(All Inputs Low)

\*\*REF\*\* R=10kΩ

\*\*PREEDBACK

\*\*PRE

FIGURE 3: HS-7541A Equivalent Circuit (All Inputs High)

### **Application Information**

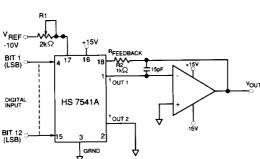

### **Unipolar Operation**

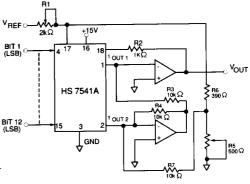

The connections required for digital unipolar operation are shown in Figure 4. The reference voltage  $V_{\text{REF}}$  may be either positive or negative. The  $2k\Omega$  potentiometer in the  $V_{\text{REF}}$  line and the  $1k\Omega$  resistor in the feedback loop are optional and are only needed when the gain error must be trimmed to less than 0.3% F.S.R. They should track each other to better than 0.1%, but don't have to track 7541's internal network resistors.

As shown in Figure 4 the DAC current output is typically connected to an external OP-AMP with it's non-inverting input tied to ground. The amplifier selected should have a low input bias current and low drift over temperature. To maintain specified HS7541 linerarity, the amplifiers input offset voltage should be nulled to less than ±200µV (o.1LSB). Table 1 shows the code table for unipolar operation.

FIGURE 4: Unipolar Operation

### **Bipolar Operation**

The connections required for bipolar operation are shown in Figure 5. The digital input is offset binary coded and produces an output according to the code table shown in Table 2.

As in the case of unipolar operation the gain trim resistors can be omitted in applications that do not require minimum gain error. Amplifier considerations of low input bias current, low drift and offset nulling are also applicable for bipolar operation.

FIGURE 5: Bipolar Operation

| DIGITAL INPUT NO | MINAL ANALOG OUTPUT        |

|------------------|----------------------------|

| 11111111111      | -0.99975 V <sub>REF</sub>  |

| 100000000000     | -0.50000V V <sub>REF</sub> |

| 01111111111      | -0.49975 V <sub>REF</sub>  |

| 00000000000      | 0                          |

**TABLE 1:** Unipolar Operation Code Table

| DITGITAL INPUT NO | MINAL ANALOG OUTPUT        |

|-------------------|----------------------------|

| 11111111111       | -0.99951 V <sub>REF</sub>  |

| 100000000000      | -0.00049V V <sub>REF</sub> |

| 01111111111       | +0.50000 V <sub>REF</sub>  |

| 00000000000       | +1.00000 V <sub>REF</sub>  |

TABLE 2: Bipolar Operation Code Table

# HS-7541A CMOS 12-BIT Multiplying DAC

## **Ordering Information**

| PART #          | PACKAGE                | T <sub>A</sub> -TEMP<br>RANGE (°C) | RELATIVE<br>ACCURACY<br>(LSB's) | GAIN<br>ERROR<br>(LSB's) |

|-----------------|------------------------|------------------------------------|---------------------------------|--------------------------|

| HS-7541A JN     | 20-Pin Epoxy Dip       | 0 to 70                            | ± 1/2                           | ±3                       |

| HS-7541A KN     | 20-Pin Epoxy Dip       | 0 to 70                            | ± 1/2                           | ± 2                      |

| HS-7541A AQ     | 20-Pin Hermetic Cerdip | -25 to 85                          | ± 1/2                           | ±3                       |

| HS-7541A BQ     | 20-Pin Hermetic Cerdip | -25 to 85                          | ± 1/2                           | ± 2                      |

| HS-541A SQ      | 20-Pin Hermetic Cerdip | -55 to 125                         | ± 1/2                           | ±3                       |

| HS-541A TQ      | 20-Pin Hermetic Cerdip | -55 to125                          | ± 1/2                           | ±2                       |

| HS-7541A SQ/883 | 20-Pin Hermetic Cerdip | -55 to125                          | +1/2                            | ±3                       |

| HS-7541A TQ/883 | 20-Pin Hermetic Cerdip | -55 to125                          | ± 1/2                           | ± 2                      |

NOTES: 1) Consult Factory For 883 Data Sheet

2) Package Designations: Suffix N-Plastic Dip, Suffix Q-Hermetic Dip. For package mechanical dimensions, call DataLinear at (408) 945-9080.

### **CROSS REFERENCE INFORMATION**

| ADI Part No.    | DataLinear Part No. |

|-----------------|---------------------|

| AD 7541A JN     | HS 7541A JN         |

| AD 7541A KN     | HS 7541A KN         |

| AD 7541A AD     | HS 7541A AQ         |

| AD 7541A BD     | HS 7541A BQ         |

| AD 7541A SD     | HS 7541A SQ         |

| AD 7541A TD     | HS 7541A TQ         |

| AD 7541A SD/883 | HS 7541A SQ/883     |

| AD 7528A TD/883 | HS 7541A TQ/883     |

The information in this document is subject to change without notice. SIPEX Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose, SIPEX Corporation assumes no responsibility for any errors that may appear in this document. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of SIPEX Corporation.