32K x 8 SRAM

#### MSM832-020/025/35

Issue 1.1: June 1993

### ADVANCE PRODUCT INFORMATION

# 32,768 x 8 CMOS High Speed Static RAM

#### **Features**

Access Times of 020/025/35 ns

Standard 28 pin DIL footprint.

Available in 28 pin VIL™ and FlatPack packages.

Operating Power 715 mW (max)

Standby Power

2.2 mW (max)

Completely Static Operation.

Battery back-up capability.

Directly TTL compatible.

Common Data Inputs and Outputs.

May be Processed to MIL-STD-883, Method 5004, non-compliant.

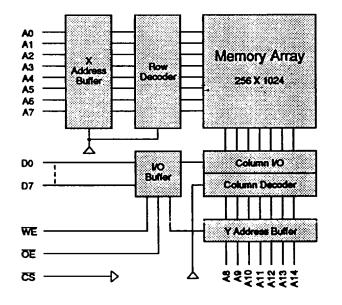

### **Block Diagram**

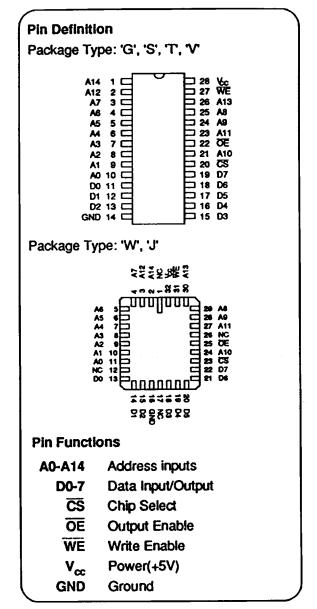

| Pin Count | Description                  | Package Type | Material | Pin Out      |

|-----------|------------------------------|--------------|----------|--------------|

| 28        | 0.6" Dual-in-Line (DIP)      | S            | Ceramic  | <b>JEDEC</b> |

| 28        | 0.3" Dual-in-Line (DIP)      | Т            | Ceramic  | JEDEC        |

| 28        | 0.1" Vertical-in-Line (VIL™) | V            | Ceramic  | JEDEC        |

| 28        | Bottom Brazed Flat Pack      | G            | Ceramic  | JEDEC        |

| 32        | Leadless Chip Carrier (LCC)  | W            | Ceramic  | JEDEC        |

| 32        | J-Leaded Chip Carrier (JLCC) | J            | Ceramic  | JEDEC        |

| Absolute Maximum Ratings (1)                                  |                |             |   |

|---------------------------------------------------------------|----------------|-------------|---|

| Voltage on any pin relative to V <sub>ss</sub> <sup>(2)</sup> | V <sub>T</sub> | -1.0V to +7 | ٧ |

| Power Dissipation                                             | Ρ.             | 1           | W |

Storage Temperature  $T_{STG}$  -65 to +150 °C Notes: (1) Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional

Notes: (1) Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

(2) Pulse width:- 3.5V for less than 10ns.

| Recommended | Operating | Conditions |

|-------------|-----------|------------|

|             |           |            |

|                       |                  | min         | typ | max                 |                 |

|-----------------------|------------------|-------------|-----|---------------------|-----------------|

| Supply Voltage        | $V_{\infty}$     | 4.50        | 5.0 | 5.50                | V               |

| Input High Voltage    | V <sub>H</sub>   | 2.2         | -   | V <sub>∞</sub> +1.0 | V               |

| Input Low Voltage     | V <sub>a</sub> . | -0.5        | -   | 0.8                 | ٧               |

| Operating Temperature | T,               | 0           | -   | 70                  | •C              |

|                       | TAL              | -40         | -   | 85                  | °C (832I)       |

|                       | TAM              | <b>-5</b> 5 | -   | 125                 | °C (832M,832MB) |

| Parameter              | Symbol           | Test Condition                                                                   | min | typ | max | Unit |  |

|------------------------|------------------|----------------------------------------------------------------------------------|-----|-----|-----|------|--|

| Input Leakage Current  | l <sub>u</sub>   | V <sub>N</sub> =0V to V <sub>cc</sub>                                            | -5  | -   | 5   | μА   |  |

| Output Leakage Current | ILO              | CS=V <sub>H</sub> or OE=V <sub>H</sub> , V <sub>IO</sub> =GND to V <sub>CC</sub> | -5  | -   | 5   | μА   |  |

| Average Supply Current | l <sub>cc1</sub> | CS=V <sub>IL</sub> ,I <sub>IO</sub> =0mA, Min. Cycle, Duty=100%                  | -   | -   | 130 | mA   |  |

| Standby Supply Current | l <sub>se</sub>  | CS=V <sub>str</sub> l/P's static                                                 |     | .=  | 30  | mΑ   |  |

|                        | <sub>581</sub>   | <u>CS</u> ≥V <sub>cc</sub> -0.2V, 0.2V≥V <sub>w</sub> ≥V <sub>cc</sub> -0.2V     | -   | -   | 5   | mA   |  |

| L-Version              | 1 <sub>582</sub> | <u>CS</u> ≥V <sub>cc</sub> -0.2V, 0.2V≥V <sub>w</sub> ≥V <sub>cc</sub> -0.2V     | -,  | -   | 3   | mΑ   |  |

| P-Version              | l <sub>ses</sub> | <u>CS</u> ≥V <sub>∞</sub> -0.2V, 0.2V≥V <sub>w</sub> ≥V <sub>∞</sub> -0.2V       | -   | -   | 400 | μА   |  |

| Output Voltage         | Val              | I <sub>ot</sub> =8.0mA                                                           | -   | -   | 0.4 | ٧    |  |

|                        | $V_{OH}$         | I <sub>OH</sub> =-4.0mA                                                          | 2.4 | -   | -   | ٧    |  |

Typical values are at  $V_{cc}$ =5.0V, $T_{A}$ =25°C and specified loading.

# Capacitance (V<sub>cc</sub>=5V±10%,T<sub>a</sub>=25°C)

|                    | - Trotto, the state of |                      |     |     |      |  |

|--------------------|------------------------|----------------------|-----|-----|------|--|

| Parameter          | Symbol                 | Test Condition       | typ | max | Unit |  |

| Input Capacitance: | C <sub>N</sub>         | V <sub>IN</sub> = 0V | •   | 8   | pF   |  |

| I/O Capacitance:   | Cko                    | V <sub>10</sub> = 0V | -   | 10  | рF   |  |

Note: This parameter is sampled and not 100% tested.

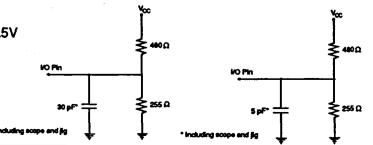

### **AC Test Conditions**

#### Output Load A

## Output Load B

- \* Input pulse levels: 0V to 3.0V

- \* Input rise and fall times: 3ns

- \* Input and Output timing reference levels: 1.5V

- \* Output load: see diagram

- \* V\_=5V±10%

## **Electrical Characteristics & Recommended AC Operating Conditions**

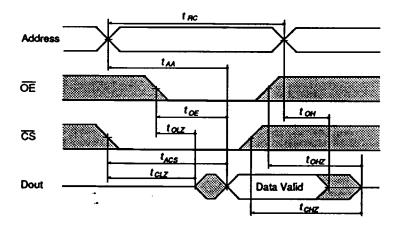

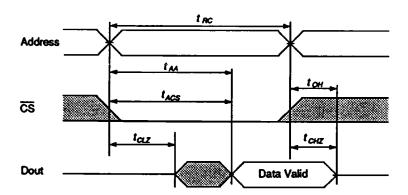

### **Read Cycle**

|                                      |                   |           | -020 |     | <i>-025</i> |     | <i>-35</i> |      |       |

|--------------------------------------|-------------------|-----------|------|-----|-------------|-----|------------|------|-------|

| Parameter                            | Symbol            | min<br>—— | max  | min | max         | min | max        | Unit | Notes |

| Read Cycle Time                      | t <sub>ec</sub>   | 20        | •    | 25  | -           | 35  | •          | ns   |       |

| Address Access Time                  | t                 | -         | 20   | -   | 25          | -   | 35         | ns   |       |

| Chip Select Access Time              | t <sub>ACS</sub>  | -         | 20   | -   | 25          | -   | 35         | ns   |       |

| Output Enable to Output Valid        | toe               | -         | 10   | -   | 12          | -   | 15         | ns   |       |

| Output Hold from Address Change      | t <sub>oH</sub>   | 3         | -    | 3   | -           | 3   | -          | ns   |       |

| Chip Selection to Output in Low Z    | taz               | 3         | -    | 3   | -           | 3   | -          | ns   | 5,6   |

| Output Enable to Output in Low Z     | toz               | 0         | -    | 0   | •           | 0   | -          | ns   | 5,6   |

| Chip Deselection to Output in High Z |                   | -         | 9    | -   | 10          | -   | 15         | ns   | 5,6   |

| Output Disable to Output in High Z   | t <sub>oriz</sub> | -         | 8    | -   | 10          | -   | 15         | ns   | 5,6   |

### Read Cycle 1 Timing Waveform(1,5) (OE Controlled)

## Read Cycle 2 Timing Waveform (1,23,45) (CS Controlled)

- Notes: (1) WE is V<sub>M</sub> (High) for Read Cycle.

- (2) Device may be continually selected, (CS=V<sub>e</sub>).

- (3) OE is V<sub>1</sub> (Low) for Read Cycle.

- (4) If address is valid prior to or coincident with  $\overline{CS}$  access is controlled by  $\overline{CS}$ , otherwise address transition controls timing.

- (5) t<sub>cre</sub> and t<sub>ore</sub> are defined as the time at which the outputs achieve the open circuit conditions and are not referenced to output voltage levels. These parameters are sampled and not 100% tested.

- (6) Transition is measured ±200mV from steady voltage with load B shown on page 2.

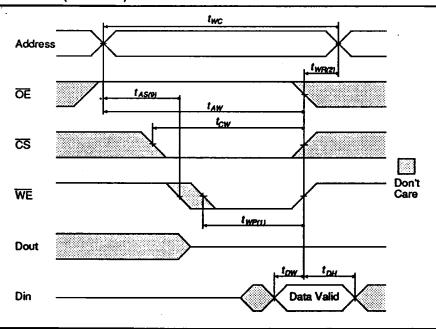

|                                 | -020             |     | 20      | <i>-025</i>  |     | -35 |     |           |      |

|---------------------------------|------------------|-----|---------|--------------|-----|-----|-----|-----------|------|

| Parameter                       | Symbol           | min | min max | c <i>min</i> | max | min | max | Unit Note |      |

| Write Cycle Time                | t <sub>wc</sub>  | 20  | •       | 25           | -   | 35  | -   | ns        |      |

| Chip Selection to End of Write  | t <sub>cw</sub>  | 15  | -       | 18           | -   | 30  | -   | ns        |      |

| Address Valid to End of Write   | t <sub>AW</sub>  | 15  | -       | 18           | -   | 30  | -   | ns        |      |

| Address Setup Time              | tas              | 0   | -       | 0            | -   | 0   | •   | ns        |      |

| Write Pulse Width               | twe              | 15  | -       | 17           | •   | 20  | -   | ns        |      |

| Write Recovery Time             | t <sub>wa</sub>  | 0   | -       | 0            | -   | 0   | -   | ns        |      |

| Write to Output in High Z       | t <sub>wiz</sub> | 0   | 10      | 0            | 15  | 0   | 15  | ns        | 9,10 |

| Data to Write Time Overlap      | t <sub>ow</sub>  | 11  | -       | 12           | -   | 15  | -   | ns        |      |

| Data Hold from Write Time       | t <sub>DH</sub>  | 0   | -       | 0            | -   | 0   | -   | ns        |      |

| Output Active from End of Write | tow              | 3   | -       | 3            | -   | 3   | -   | ns        |      |

# Write Cycle 1 Timing Waveform (OE Clock)

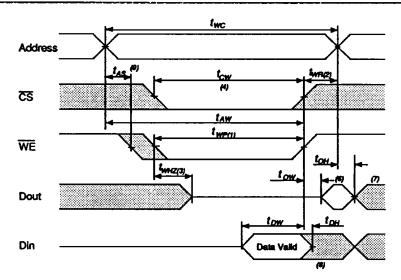

Write Cycle 2 Timing Waveform (OE Low Fixed)

#### **AC Write Characteristics Notes**

- (1) A write occurs during the overlap (twp) of a low CS and a low WE.

- (2) t<sub>wn</sub> is measured from the earlier of CS or WE going high to the end of write cycle.

- (3) During this period, I/O pins are in the output state. Input signals out of phase must not be applied.

- (4) If the  $\overline{\text{CS}}$  low transition occurs simultaneously with the  $\overline{\text{WE}}$  low transition or after the  $\overline{\text{WE}}$  low transition, outputs remain in a high impedance state.

- (5) OE is continuously low. (OE=V<sub>x</sub>)

- (6) Dout is in the same phase as written data of this write cycle.

- (7) Dout is the read data of next address.

- (8) If CS is low during this period, I/O pins are in the output state. Input signals out of phase must not be applied to I/O pins.

- (9) WE must be high during all address transitions except when the device is deselected with CS.

- (10) Transition is measured ±200mV from steady voltage with load B. This parameter is sampled and is not 100% tested.

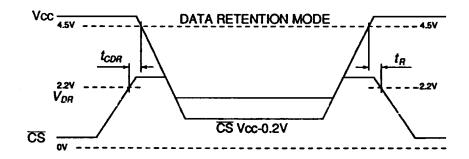

| Parameter Sy                         |                  | ymbol Test Condition I                                                     |                                | typ | max | Unit |

|--------------------------------------|------------------|----------------------------------------------------------------------------|--------------------------------|-----|-----|------|

| V <sub>∞</sub> for Data Retention    | V <sub>DR</sub>  | <u>CS</u> ≥ V <sub>cc</sub> -0.2V                                          | 2.0                            | -   | •   | ٧    |

| Data Retention Current               | 2                | $\overline{CS} \ge V_{cc}^{-0.2V}, V_{N} \ge V_{cc}^{-0.2V}$ or $\le 0.2V$ | eV.                            |     |     |      |

| L-Version                            | CCDR1            | V <sub>∞</sub> = 3V                                                        | -                              | -   | 800 | μА   |

| P-Version                            | CCOR2            | V <sub>∞</sub> =3V                                                         | -                              | -   | 200 | μΑ   |

| Chip Deselect to Data Retention Time | t <sub>con</sub> | See Retention Waveform                                                     | 0                              | -   | -   | ns   |

| Operation Recovery Time              | t <sub>R</sub>   | See Retention Waveform                                                     | t <sub>RC</sub> <sup>(1)</sup> | -   | -   | ns   |

Notes (1) t<sub>ac</sub>=Read Cycle Time

#### **Data Retention Waveform**

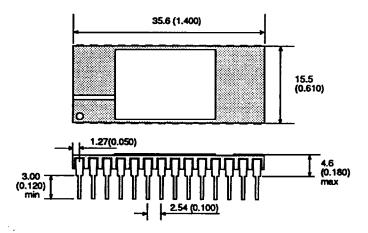

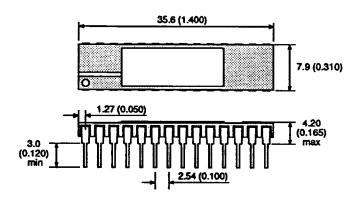

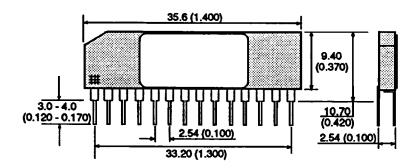

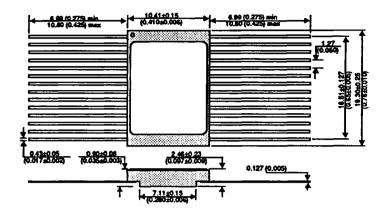

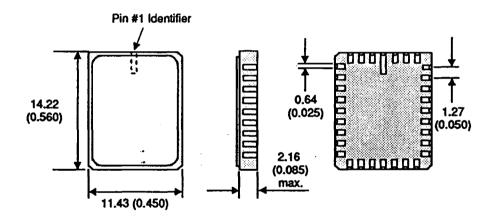

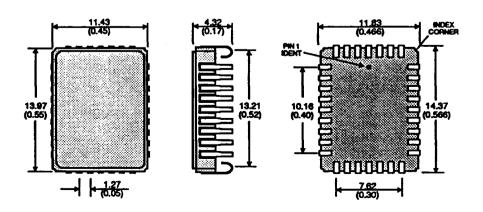

### Package Details Dimensions in mm (inches). Tolerance on all dimensions $\pm$ 0.254 (0.01)

# 28 pin 0.6" Dual-In-Line (DIL) - 'S' Package

# 28 pin 0.3" Dual-In-Line (DIL) - T' Package

28 pin 0.1" Vertical-in-Line (VIL) - "V" Package

# 28 pin Cereamic Flatpack - 'G' Package

# 32 pad Leadless Chip Carrier (LCC) - 'W' Package

32 pad 'J' Leaded Chi p Carrier (JLCC) - 'J' Package

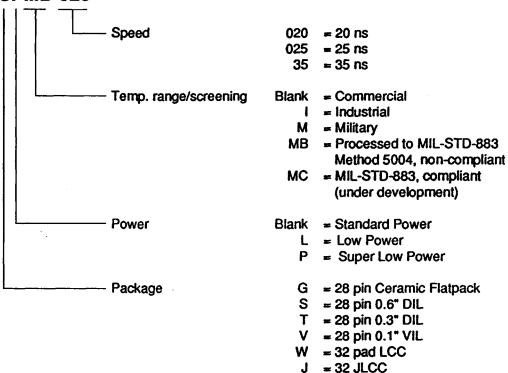

#### **Ordering Information**

## MSM832SPMB-020

Note: For more information regarding screening levels, contact Mosaic Semiconductor Inc. for a 'Screening Level Applications Note.'

mofaic

Mosaic

Semiconductor

Inc.