# High-Frequency Flash Programmable PLL Die with Spread Spectrum

#### **Features**

- Flash programmable die for in-package programming of crystal oscillators

- High resolution phase-locked loop (PLL) with 10-bit multiplier and 7-bit divider

- Flash programmable capacitor tuning array

- $\blacksquare$  Simple two-pin programming interface (excluding VDD and  $V_{SS}$  pins)

- On-chip oscillator used with external 25.1 MHz fundamental tuned crystal

- Flash programmable spread spectrum with spread percentages between ± 0.25% and ± 2.00%

- Spread spectrum on/off function

- Operating frequency: 5 MHz to 170 MHz at 3.3 V ± 10%

- Seven-bit linear post divider with divide options from divide-by-2 to divide-by-127

- Programmable PD# or OE pin

- Programmable asynchronous or synchronous OE and PD# modes

- Low jitter output: < 200 ps (pk-pk) at 3.3 V ± 10%

- Controlled rise and fall times and output slew rate

- Software configuration support

#### **Benefits**

- Enables quick turnaround of custom oscillators and lowers inventory costs through stocking blank parts. In addition, the part may be Flash programmed up to 100 times. This reduces programming errors and provides an easy upgrade path for existing designs.

- Enables synthesis of highly accurate and stable output clock frequencies with zero or low PPM.

- Enables fine tuning of output clock frequency by adjusting the load capacitance of the crystal.

- Allows the device to go into standard 4 or 6-pin packages.

- Lowers cost of oscillator, because PLL may be programmed to a high frequency using a low frequency, low cost crystal.

- Provides various spread percentage.

- Provides the ability to enable or disable spread spectrum with an external pin.

- Provides flexibility in output configurations and testing.

- Enables low power operation or output enable function.

- Provides flexibility for system applications through selectable instantaneous or synchronous change in outputs.

- Suitable for most PC, consumer, and networking applications.

- Has lower EMI than oscillators.

- Easy to use software support for design entry.

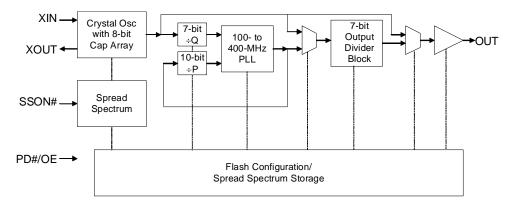

## **Logic Block Diagram**

## **Contents**

| Die Pad                           | 3 |

|-----------------------------------|---|

| Die Pad Definitions               | 4 |

| Functional Description            | 5 |

| Flash Configuration and           |   |

| Spread Spectrum Storage Block     | 5 |

| PLL Output Frequency              | 5 |

| Power Management Features         | 5 |

| Spread Spectrum                   | 5 |

| Inkless Die Pick Map (DPM) Format | 6 |

| Absolute Maximum Ratings          | 7 |

| Operating Conditions              | 7 |

| DC Electrical Characteristics     | 8 |

| AC Electrical Characteristics     | 9 |

| Timing Parameters                 | 9 |

|                                   |   |

| Switching Waveforms                     | 10 |

|-----------------------------------------|----|

| Ordering Information                    |    |

| Ordering Code Definitions               |    |

| Acronyms                                |    |

| Document Conventions                    | 13 |

| Units of Measure                        | 13 |

| Document History Page                   | 14 |

| Sales, Solutions, and Legal Information |    |

| Worldwide Sales and Design Support      | 16 |

| Products                                | 16 |

| PSoC® Solutions                         | 16 |

| Cypress Developer Community             | 16 |

| Technical Support                       | 16 |

## Die Pad

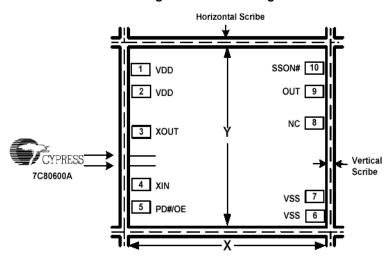

Figure 1. Die Pad Diagram

#### Note

Active die size: X = 75.0 mils / 1907  $\mu m$  Y = 56.2 mils / 1428  $\mu m$

Scribe: X (vertical) = 3.4 mils / 86.2  $\mu$ m

Y (horizontal) = 2.8 mils / 71  $\mu$ m

Bond pad opening:  $85~\mu m \times 85~\mu m$  Pad pitch:  $125~\mu m \times 125~\mu m$  (pad center to pad center) Wafer thickness: 11~mils typical

## **Die Pad Definitions**

[Pad coordinates are referenced from the center of the die  $(X=0,\,Y=0)$ ]

| Name            | Die Pad | Description                                                                                                                                                                    | X Coordinate     | Y Coordinate       |

|-----------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------|

| V <sub>DD</sub> | 1, 2    | Power supply                                                                                                                                                                   | -843.612         | 597.849, 427.266   |

| V <sub>SS</sub> | 6, 7    | Ground                                                                                                                                                                         | 883.743, 887.355 | -563.304, -369.957 |

| XIN             | 4       | Crystal gate pin                                                                                                                                                               | -843.612         | -1.806             |

| XOUT            | 3       | Crystal drain pin                                                                                                                                                              | -843.612         | 236.565            |

| PD#/OE          | 5       | Flash programmable to function as power down or output enable in normal operating mode. Weak pull up is enabled by default.                                                    | -843.612         | -424.662           |

| V <sub>PP</sub> |         | Super voltage when going into programming mode.                                                                                                                                |                  |                    |

| SDA             |         | Data pin when going into and when in programming mode.                                                                                                                         |                  |                    |

| SSON#           | 10      | Active low spread spectrum control. Asserting LOW turns the internal modulation waveform on. Strong pull down is enabled by default. Pull down is disabled in power down mode. |                  | 589.848            |

| SCL             |         | Clock pin in programming mode. Must be double bonded to the OUT pad for pinouts not using the SSON# function. There is an internal pull down resistor on this pad.             |                  |                    |

| OUT             | 9       | Clock output. There is an internal pull down resistor on this pad. Weak pull down is enabled by default. Default output is from the reference.                                 | 834.183          | 462.840            |

| NC              | 8       | No connect pin (do not connect this pad).                                                                                                                                      | 834.183          | 335.832            |

## **Functional Description**

CY5057 is a Flash programmable, high accuracy, PLL-based die designed for the crystal oscillator market. It also contains spread spectrum circuitry that is enabled or disabled with an external pin. The die is integrated with a low cost 25.1 MHz fundamental tuned crystal in a 4 or 6-pin through hole or surface mount package. The oscillator devices may be stocked as blank parts and custom frequencies programmed in-package at the last stage before shipping. This enables faster manufacturing of custom and standard crystal oscillators without the need for dedicated and expensive crystals.

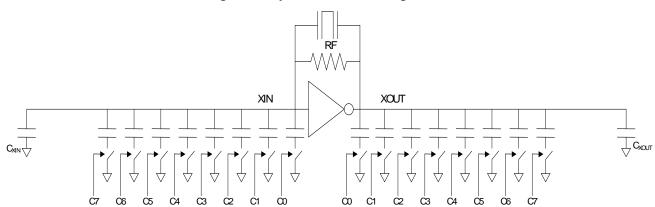

CY5057 contains an on-chip oscillator and unique oscillator tuning circuit for fine tuning the output frequency. The crystal  $C_{load}$  is selectively adjusted by programming a set of Flash memory bits. This feature is used to compensate for crystal variations or to obtain a more accurate synthesized frequency.

CY5057 uses a simple two-pin programming interface, excluding the  $V_{SS}$  and  $V_{DD}$  pins. Clock outputs are generated from 5 MHz to 170 MHz at 3.3 V  $\pm$  10% operating voltage. You can reprogram the entire Flash configuration multiple times to alter or reuse the programmed inventory.

CY5057 PLL die is designed for very high resolution. It has a 10-bit feedback counter multiplier and a 7-bit reference counter divider. This enables the synthesis of highly accurate and stable output clock frequencies with zero or low PPM error. The output of the PLL or the oscillator is further modified by a 7-bit linear post divider with a total of 126 divider options (2 to 127).

CY5057 also contains flexible power management controls. These parts include both power down mode (PD# = 0) and output enable mode (OE = 1). The power down and output enable modes have an additional setting to determine timing (asynchronous or synchronous) with respect to the output signal.

Controlled rise and fall times, unique output driver circuits, and innovative circuit layout techniques enables CY5057 to have low jitter and accurate outputs. This makes it suitable for most PC, networking, and consumer applications.

CY5057 also has an additional spread spectrum feature that is disabled or enabled with an external pin. For more information, refer the section Spread Spectrum.

## Flash Configuration and Spread Spectrum Storage Block

Table 2 summarizes the features configurable by the Flash memory bits. Refer to "CY5057 Programming Specification" for programming details. The specification can be obtained from your Cypress factory representative.

**Table 1. Flash Programmable Features**

| Adjust                                                | Feedback counter value (P)                  |  |  |

|-------------------------------------------------------|---------------------------------------------|--|--|

| Frequency                                             | Reference counter value (Q)                 |  |  |

|                                                       | Output divider selection                    |  |  |

|                                                       | Oscillator tuning (load capacitance values) |  |  |

|                                                       | Oscillator direct output                    |  |  |

|                                                       | Power management mode (OE or PD#)           |  |  |

| Power management timing (synchronous or asynchronous) |                                             |  |  |

| Spread spectrum                                       |                                             |  |  |

| Pull up and Pull down resistors                       |                                             |  |  |

## **PLL Output Frequency**

CY5057 contains a high resolution PLL with a 10-bit multiplier and a 7-bit divider. The output frequency of the PLL is determined by the following equation:

$$F_{PLL} = \frac{2 \cdot (PBL + 4) + Po}{(QL + 2)} \cdot F_{REF}$$

Equation (1)

In this equation:

- Q<sub>L</sub> is the loaded or programmed reference counter value (Q counter)

- P<sub>BL</sub> is the loaded or programmed feedback counter value (P counter)

- Po is the P offset bit (is only 0 or 1)

In spread spectrum mode, the time averaged P value is used to calculate the average frequency.

## **Power Management Features**

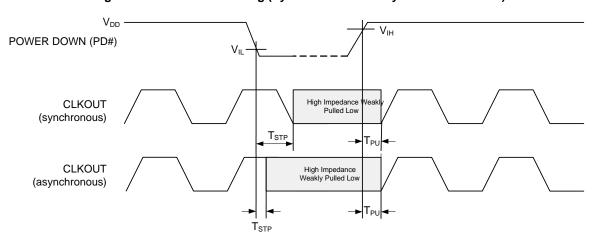

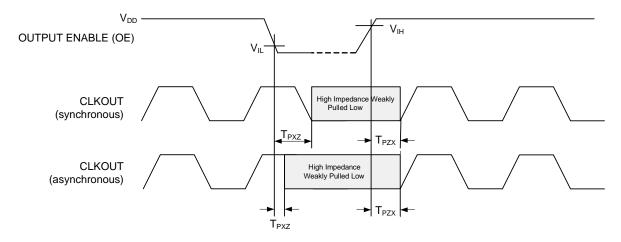

CY5057 contains Flash programmable PD# (active LOW) and OE (active HIGH) functions. If power down mode is selected (PD# = 0), the oscillator and PLL are placed in a low supply current standby mode and the output is tri-stated and weakly pulled low. The oscillator and PLL circuits must relock when the part leaves power down mode. If output enable mode is selected (OE = 0), the output is tri-stated and weakly pulled low. In this mode, the oscillator and PLL circuits continue to operate allowing a rapid return to normal operation when the output is enabled.

In addition, the PD# and OE modes may be programmed to occur synchronously or asynchronously with respect to the output signal. When the asynchronous setting is used, the power down or output disable occurs immediately (allowing for logic delays) irrespective of the position in the clock cycle. However, when the synchronous setting is used, the part waits for a falling edge at the output before power down or output enable signal is initiated. This prevents output glitches. In asynchronous or synchronous setting, the output is always enabled synchronously by waiting for the next falling edge of the output.

## Spread Spectrum

CY5057 contains spread spectrum with Flash programmable spread percentage and modulation frequency. Center spread nonlinear "hershey kiss" modulation is obtained. Spread percentage is programmed to values between ±0.25% and ±2.00%, in 0.25% intervals. Only one spread profile (for one specific percentage spread and for one output frequency) may be programmed into the device at a time.

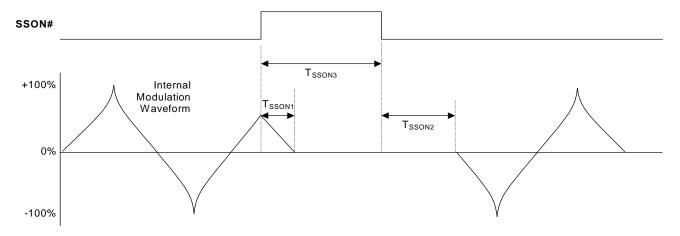

CY5057 has a spread spectrum on and off function. The spread spectrum is enabled or disabled through an external pin. Timing this feature is explained in the section Switching Waveforms on page 10.

Figure 2. Crystal Oscillator Tuning Circuit

Table 2. Crystal Oscillator Tuning Cap Values

| Bit [1] Capacitance per Bit (pF)                   |       |  |

|----------------------------------------------------|-------|--|

| C <sub>7</sub> (MSB)                               | 24.32 |  |

| C <sub>6</sub><br>C <sub>5</sub>                   | 12.16 |  |

|                                                    | 6.08  |  |

| C <sub>4</sub><br>C <sub>3</sub><br>C <sub>2</sub> | 3.04  |  |

| C <sub>3</sub>                                     | 1.52  |  |

|                                                    | 0.76  |  |

| C <sub>1</sub>                                     | 0.38  |  |

| C <sub>0</sub> (LSB)                               | 0.19  |  |

## Inkless Die Pick Map (DPM) Format

Cypress ships inkless wafers to customers with an accompanying die pick map, which is used to determine the good die for assembly and programming. Customers can also access individual DPM files at their convenience through ftp.cypress.com with a valid user account login and password. Contact your local Cypress Field Application Engineer (FAE) or sales representative for a customer FTP account. The DPM files are named using the fab lot number and wafer number scribed on the wafer. The DPM files are transferred to the FTP account of the customer when the factory ships out the wafers against their purchase order (PO).

#### Note

<sup>1.</sup> C<sub>XIN,</sub> C<sub>XOUT,</sub> and parasitic capacitance due to fixture and package must be included when calculating the total capacitance.

## **Absolute Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested. Supply voltage .....-0.5 to 7.0 V Input voltage .....-0.5 V to V<sub>DD</sub> + 0.5 Storage temperature (non-condensing) ...... -55°C to 125°C

| Junction temperature                                    | -40°C to 125°C |

|---------------------------------------------------------|----------------|

| Data retention at Tj = 125 °C                           | > 10 years     |

| Maximum non volatile programming cycles                 | 100            |

| Static discharge voltage (per MIL-STD-883, method 3015) | ≥ 2000 V       |

| Output (pad 9) sink or sources current2                 | 20 mA maximum  |

## **Operating Conditions**

| Parameter           | Description                                                                                                                    |       | Max  | Unit |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------|-------|------|------|

| $V_{DD}$            | Supply voltage (3.3 V)                                                                                                         | 3.0   | 3.6  | V    |

| T <sub>AJ</sub> [2] | Operating temperature, junction                                                                                                | -40   | 100  | °C   |

| C <sub>LC</sub>     | Maximum capacitive load on the output (CMOS levels spec) V <sub>DD</sub> = 3.0 V to 3.6 V, output frequency = 5 MHz to 170 MHz | _     | 15   | pF   |

| X <sub>REF</sub>    | Reference frequency with spread spectrum disabled. Fundamental tuned crystals only                                             | 25.1  | 25.1 | MHz  |

| C <sub>in</sub>     | nput capacitance (except crystal pins)                                                                                         |       | 7    | pF   |

| C <sub>XIN</sub>    | Crystal input capacitance (all internal caps off)                                                                              | 10    | 14   | pF   |

| C <sub>Xout</sub>   | Crystal output capacitance (all internal caps off)                                                                             | 10    | 14   | pF   |

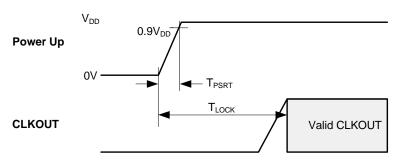

| T <sub>PSRT</sub>   | Power up time for all $V_{\mbox{\scriptsize DD}} s$ to reach minimum specified voltage (power ramps must be monotonic)         | 0.005 | 500  | ms   |

Document Number: 38-07363 Rev. \*K

Note

2. In Cypress standard TSSOP packages with external crystal.

## **DC Electrical Characteristics**

$(Tj = -40 \text{ to } 100 \text{ }^{\circ}\text{C})$

| Parameter           | Description                                 | Test Conditions                                                         | Min                   | Max                   | Unit |

|---------------------|---------------------------------------------|-------------------------------------------------------------------------|-----------------------|-----------------------|------|

| V <sub>IL</sub>     | Input low voltage<br>PD#/OE and SSON# pins  | V <sub>DD</sub> = 3.0 V–3.6 V                                           | -                     | 0.3 × V <sub>DD</sub> | V    |

| V <sub>IH</sub>     | Input high voltage<br>PD#/OE and SSON# pins | V <sub>DD</sub> = 3.0 V–3.6 V                                           | 0.7 × V <sub>DD</sub> | _                     | V    |

| V <sub>OL</sub>     | Output low voltage, OUT pin                 | $V_{DD} = 3.0 \text{ V} - 3.6 \text{ V}, I_{OL} = 8 \text{ mA}$         | -                     | 0.4                   | V    |

| V <sub>OH</sub>     | Output high voltage, CMOS levels            | $V_{DD} = 3.0 \text{ V} - 3.6 \text{ V}, I_{OH} = -8 \text{ mA}$        | V <sub>DD</sub> – 0.4 | _                     | V    |

| I <sub>ILPDOE</sub> | Input low current, PD#/OE pin               | $V_{IN} = V_{SS}$ (Internal pull up = 3 M $\Omega$ typical)             | -                     | 10                    | μΑ   |

| I <sub>IHPDOE</sub> | Input high current, PD#/OE pin              | V <sub>IN</sub> = V <sub>DD</sub> (Internal pull up = 100 kΩ typical)   | -                     | 10                    | μΑ   |

| I <sub>ILSR</sub>   | Input low current, SSON# pin                | V <sub>IN</sub> = V <sub>SS</sub> (Internal pull down = 100 kΩ typical) | -                     | 10                    | μΑ   |

| I <sub>IHSR</sub>   | Input high current, SSON# pin               | $V_{IN} = V_{DD}$ (Internal pull down = 100 k $\Omega$ typical)         | -                     | 50                    | μΑ   |

| I <sub>DD</sub>     | Supply current                              | No load, V <sub>DD</sub> = 3.0 V–3.6 V, Fout = 170 MHz                  | -                     | 50                    | mA   |

| I <sub>OZ</sub>     | Output leakage current, OUT pin             | V <sub>DD</sub> = 3.0 V–3.6 V, output disabled with OE                  | -                     | 50                    | μΑ   |

| I <sub>PD</sub>     | Standby current                             | V <sub>DD</sub> = 3.0 V–3.6 V,<br>device powered down with PD#          | -                     | 50                    | μА   |

| R <sub>UP</sub>     | Pull up resistor on PD#/OE pin              | $V_{DD}$ = 3.0 V–3.6 V, measured at $V_{IN}$ = $V_{SS}$                 | 1                     | 6                     | МΩ   |

|                     |                                             | $V_{DD}$ = 3.0 V–3.6 V, measured at $V_{IN}$ = 0.7 $V_{DD}$             | 80                    | 150                   | kΩ   |

| R <sub>DN</sub>     | Pull down resistor on SSON# and OUT pins    | $V_{DD}$ = 3.0 V–3.6 V, measured at $V_{IN}$ = 0.5 $V_{DD}$             | 80                    | 150                   | kΩ   |

| Rf                  | Crystal feedback resistor                   | $V_{DD} = 3.0 \text{ V} - 3.6 \text{ V}$ , measured at $X_{IN} = 0$     | 100                   | -                     | kΩ   |

## **AC Electrical Characteristics**

$(Tj = -40 \text{ to } 100 \text{ }^{\circ}\text{C})$

| Parameter [3]    | Description                | Test Conditions                                                                                             | Min | Max                         | Unit |

|------------------|----------------------------|-------------------------------------------------------------------------------------------------------------|-----|-----------------------------|------|

| F <sub>out</sub> | Output frequency           | V <sub>DD</sub> = 3.0 V–3.6 V, C <sub>L</sub> = 15 pF                                                       | 5   | 170                         | MHz  |

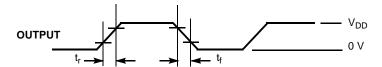

| tr               | OUT rise time              | $V_{DD} = 3.0 \text{ V} - 3.6 \text{ V}, 20\% \text{ to } 80\% \text{ V}_{DD}, C_L = 15 \text{ pF}$         | _   | 2.7                         | ns   |

| tf               | OUT fall time              | $V_{DD} = 3.0 \text{ V} - 3.6 \text{ V}, 80\% \text{ to } 20\% \text{ V}_{DD}, \text{ C}_L = 15 \text{ pF}$ | _   | 2.7                         | ns   |

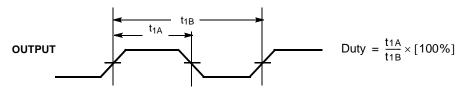

| DC               | OUT duty cycle             | Divider output, measured at V <sub>DD</sub> /2                                                              | 45  | 55                          | %    |

|                  |                            | Crystal direct output, measured at V <sub>DD</sub> /2                                                       | 40  | 60                          | %    |

| t <sub>J1</sub>  | Peak-to-peak period jitter | $F_{out} \ge 133 \text{ MHz}, V_{DD}/2, SS \text{ off}$                                                     | _   | 200                         | ps   |

|                  |                            | 25 MHz $\leq$ F <sub>out</sub> $<$ 133 MHz, V <sub>DD</sub> /2, SS off                                      |     | 400                         | ps   |

|                  |                            | F <sub>out</sub> < 25 MHz, V <sub>DD</sub> /2, SS off                                                       |     | 1% of<br>1/F <sub>out</sub> | S    |

| t <sub>J2</sub>  | Cycle-to-cycle jitter      | $F_{out}$ > 133 MHz, $V_{DD}$ /2, SS on                                                                     | _   | 200                         | ps   |

|                  |                            | 25 MHz $\leq$ F <sub>out</sub> $<$ 133 MHz, V <sub>DD</sub> /2, SS on                                       |     | 400                         | ps   |

|                  |                            | F <sub>out</sub> < 25 MHz, V <sub>DD</sub> /2, SS on                                                        |     | 1% of<br>1/F <sub>out</sub> | S    |

| F <sub>MOD</sub> | Modulation frequency       |                                                                                                             | 30  | 33                          | kHz  |

| DL               | Crystal drive level        | Measured at 25.1 MHz, with crystal ESR = 20 $\Omega$ , cap setting = hex16, DL = program code [1,0]         | -   | 540                         | μW   |

| –R               | Negative resistance        | Measured at 25.1 MHz, cap setting = hex 3F                                                                  | _   | -200                        | Ω    |

## **Timing Parameters**

| Parameter [3]          | Description                                                                               |     | Max        | Unit |

|------------------------|-------------------------------------------------------------------------------------------|-----|------------|------|

| T <sub>SSON1</sub>     | Time from steady state spread to steady state nonspread                                   |     | 600        | μS   |

| T <sub>SSON2</sub>     | Time from steady state non spread to steady state spread                                  |     | 100        | μS   |

| T <sub>SSON3</sub>     | Minimum SSON# pulse width (positive or negative)                                          | 250 | _          | μS   |

| T <sub>MOD</sub>       | Spread spectrum modulation period                                                         | 30  | 33.33      | μS   |

| T <sub>STP,SYNC</sub>  | Time from falling edge on PD# to stopped outputs, synchronous mode, $T = 1/F_{out}$       |     | 1.5T + 350 | ns   |

| T <sub>STP,ASYNC</sub> | Time from falling edge on PD# to stopped outputs, asynchronous mode                       |     | 350        | ns   |

| T <sub>PU,SYNC</sub>   | Time from rising edge on PD# to outputs at valid frequency, synchronous mode              |     | 3          | ms   |

| T <sub>PU,ASYNC</sub>  | Time from rising edge on PD# to outputs at valid frequency, asynchronous mode             |     | 3          | ms   |

| T <sub>PXZ,SYNC</sub>  | Time from falling edge on OE to high impedance outputs, synchronous mode, $T = 1/F_{out}$ |     | 1.5T+350   | ns   |

| T <sub>PXZ,ASYNC</sub> | Time from falling edge on OE to high impedance outputs, asynchronous mode                 |     | 350        | ns   |

| T <sub>PZX,SYNC</sub>  | Time from rising edge on OE to running outputs, synchronous mode, $T = 1/F_{out}$         |     | 1.5T + 350 | ns   |

| T <sub>PZX,ASYNC</sub> | Time from rising edge on OE to running outputs, asynchronous mode                         |     | 350        | ns   |

| T <sub>LOCK</sub>      | PLL lock time (from 0.9 V <sub>DD</sub> to valid output clock frequency)                  |     | 10         | ms   |

Document Number: 38-07363 Rev. \*K

Note

3. In Cypress standard TSSOP packages with external crystal.

## **Switching Waveforms**

Figure 3. Duty Cycle Timing (dc)

Figure 4. Output Rise/Fall Time

Figure 5. Power Down Timing (Synchronous and Asynchronous Modes)

Figure 6. Output Enable Timing (Synchronous and Asynchronous Modes)

## **Switching Waveforms** (continued)

Figure 7. Power Up Timing

Figure 8. Spread Spectrum On and OFF Timing

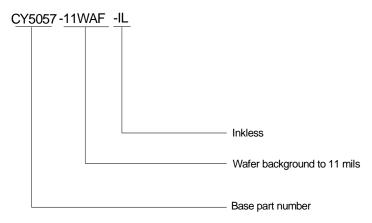

## **Ordering Information**

| Ordering Code   | Status | Туре                                  | Operating Range  |

|-----------------|--------|---------------------------------------|------------------|

| CY5057-11WAF-IL | Active | Inkless wafer (background to 11 mils) | –40 °C to 100 °C |

## **Ordering Code Definitions**

## **Acronyms**

| Acronym | Description                             |  |

|---------|-----------------------------------------|--|

| CLKOUT  | Clock Output                            |  |

| CMOS    | Complementary Metal Oxide Semiconductor |  |

| DPM     | Die Pick Map                            |  |

| EMI     | Electromagnetic Interference            |  |

| EPROM   | Erasable Programmable Read Only Memory  |  |

| FAE     | Field Application Engineer              |  |

| FTP     | File Transfer Protocol                  |  |

| OE      | Output Enable                           |  |

| PAL     | Phase Alternate Line                    |  |

| PD      | Power Down                              |  |

| PLL     | Phase Locked Loop                       |  |

| TSSOP   | Thin Shrunk Small Outline Package       |  |

| TTL     | Transistor-Transistor Logic             |  |

## **Document Conventions**

## **Units of Measure**

| Symbol | Unit of Measure   |  |  |  |  |

|--------|-------------------|--|--|--|--|

| °C     | degree Celsius    |  |  |  |  |

| MHz    | megahertz         |  |  |  |  |

| ΜΩ     | megaohm           |  |  |  |  |

| μA     | microampere       |  |  |  |  |

| μF     | microfarad        |  |  |  |  |

| μm     | micrometer        |  |  |  |  |

| mA     | milliampere       |  |  |  |  |

| mm     | millimeter        |  |  |  |  |

| ms     | millisecond       |  |  |  |  |

| ns     | nanosecond        |  |  |  |  |

| ps     | picosecond        |  |  |  |  |

| ppm    | parts per million |  |  |  |  |

| Ω      | ohm               |  |  |  |  |

| kΩ     | kilohm            |  |  |  |  |

| PPM    | parts per million |  |  |  |  |

| рр     | peak-to-peak      |  |  |  |  |

| %      | percent           |  |  |  |  |

| pF     | picofarad         |  |  |  |  |

| V      | volt              |  |  |  |  |

## **Document History Page**

| Document Number: 38-07363  Powision FCN Orig. of Submission Description of Change |         |               |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|-----------------------------------------------------------------------------------|---------|---------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Revision                                                                          | ECN     | Change        | Date       | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| **                                                                                | 112486  | CKN           | See ECN    | New data sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| *4                                                                                | 121373  | CKN           | See ECN    | Added scribe lines to die pad description Added wafer thickness to die pad description Added X and Y coordinates to die pad description Removed list of discrete frequencies and discrete spread percentages Removed references to discrete frequencies and profile tables Replaced with description of software for full programmability Operating frequency changed to 5 MHz–170 MHz Removed C0 and C1 from crystal oscillator tuning circuit; renumbered other capacitors Changed maximum junction temperature to 125°C Changed PDOE internal pull up value to 1–6 Mohm when $V_{\text{IN}} = V_{\text{SS}}$ Changed IILPDOE to 10 $\mu\text{A}$ Changed Rf spec to 100 kohm, at condition $X_{\text{IN}} = 0$ Change DL spec to 540 $\mu\text{W}$ , at condition cap setting = hex16, DL=10 Added power up timing diagram separate from power down timing diagram Removed die information table |  |  |  |

| *B                                                                                | 127414  | RGL           | See ECN    | Added –11 and other details to ordering Information Added t <sub>PU</sub> details to operating conditions Changed max T <sub>SSON1</sub> value to 600 in timing parameters table Changed parameter T <sub>PU</sub> under timing parameters to T <sub>LOCK</sub> with the descriptior "PLL lock time" Altered minimum and maximum values in power up timing figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| *C                                                                                | 2143928 | FGA /<br>PYRS | See ECN    | Modified power down timing diagram Changed power up timing from min. of 50 µs to 5 µs Added output sink/source current specification in the absolute max ratings Change cap array from 10 to 8-bit Add MSB and LSB in the crystal oscillator tuning cap values table Fixed power up timing diagram Added -R cap setting value FF Added Inkless die information before Absolute Maximum Ratings Added new part number (CY5057-11WAF-IL) with note                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| *D                                                                                | 2541797 | AESA          | 07/24/08   | Updated template. Added Note "Not recommended for new designs." Added part number CY5057K-11WAF-IL in ordering information table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| *E                                                                                | 2600816 | KVM /<br>AESA | 11/04/08   | Updated to match data sheet labeled "Rev *C November 16, 2004" (added logorand die number to die drawing; added pull up & pull down resistors to features table; revised –R spec and conditions; added missing labels to waveform drawings)  Removed CY5057K-11WAF-IL from ordering information table.  Updated die dimensions (page 2) with 29 mil thickness; corrected scribe variables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| *F                                                                                | 2621902 | KVM /<br>AESA | 12/15/2008 | Corrected typos on p. 1 (spread amount) & p. 5 ( $\rm V_{IL}$ & $\rm V_{IH}$ test conditions). Connected text frames.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| *G                                                                                | 2897373 | CXQ           | 03/22/10   | Removed part number CY5057-29WAF-IL from Ordering information table. Updated copyright section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| *H                                                                                | 3068367 | CXQ           | 10/21/2010 | Removed CY5057-11WAF part from Ordering Information. Added Ordering Code Definitions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| *                                                                                 | 3201346 | CXQ           | 03/21/2011 | Sunset review. No material changes to document. Fixed various typos. Included Acronyms and units tables. Updated template and styles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

## **Document History Page** (continued)

| Document Title: CY5057, High-Frequency Flash Programmable PLL Die with Spread Spectrum Document Number: 38-07363 |         |                    |                    |                                                     |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|-----------------------------------------------------|--|--|--|--|

| Revision                                                                                                         | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                               |  |  |  |  |

| *J                                                                                                               | 4334627 | CINM               | 04/06/2014         | Updated in new template.                            |  |  |  |  |

|                                                                                                                  |         |                    |                    | Completing Sunset Review.                           |  |  |  |  |

| *K                                                                                                               | 5686604 | XHT                | 04/06/2017         | Updated to new template<br>Completing sunset review |  |  |  |  |

## Sales, Solutions, and Legal Information

### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

cypress.com/usb

cypress.com/wireless

#### **Products**

**USB Controllers**

Wireless Connectivity

ARM® Cortex® Microcontrollers cypress.com/arm Automotive cypress.com/automotive Clocks & Buffers cypress.com/clocks Interface cypress.com/interface Internet of Things cypress.com/iot Memory cypress.com/memory Microcontrollers cypress.com/mcu **PSoC** cypress.com/psoc Power Management ICs cypress.com/pmic Touch Sensing cypress.com/touch

## PSoC® Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6

### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

## **Technical Support**

cypress.com/support

#### **Clock Tree Services**

cypress.com/cts

© Cypress Semiconductor Corporation, 2002-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended of or the operation of weapons, weapons systems, nuclear installations, life-support devices or systems of the medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the aliure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 38-07363 Rev. \*K Revised April 6, 2017 Page 16 of 16