# **Synchronous Communication SRAM**

# Features

- 256K x 36 or 512K x 18 organization

- 3.3 V or 2.5 V Power Supply and I/O

- LVTTL Input and Output levels

- 100% bus utilization at high frequencies

- Optimized control logic for minimum control signal interface

- CKE to enable or suspend clock operations

- Three chip enable pins (CE, CE2, CE2) for depth expansion with double cycle deselect

- Single Read/Write control pin (R/W)

- · Individual Byte Write Controls

- Synchronous Pipeline Mode of Operation with fully coherent Self-Timed Late-Late-Write

- Registered control inputs, addresses and data I/O.

- Burst feature supports interleaved or linear burst orders

- SNOOZE Mode, for reduced stand-by power.

- 100 pin TQFP package

## **Description**

The IBM0418/36A86L/SQKA 8Mb SRAMs are Synchronous Pipeline SRAMs using Late-Late-Write protocol and optimized I/O timing parameters to permit 100% bus utilization for any sequence of READ & WRITE operations.

The clock input (CLK) is used to register all synchronous input pins on its rising edge. Synchronous inputs include clock enable (CKE), chip enable (CE, CE2 and CE2), cycle start input (ADV/LD), all addresses (SA), read/write control (R/W), byte write controls (BWa, BWb, BWc, BWd) and all data inputs (DQ).

Asynchronous inputs include output enable  $(\overline{OE})$ , which may be carefully timed to optimally reduce bus turn-around time, and snooze enable (ZZ). Static burst mode pin (MODE) selects between interleaved and linear burst modes, and should be tied HIGH (or left unconnected) for interleaved burst order (or if Burst Mode is not used), or tied LOW for linear burst order.

READ, WRITE and DESELECT cycles (see cycle truth table) are initiated with ADV/LD = LOW. Sub-

sequent READ or WRITE operations can load new Addresses (ADV/ $\overline{LD}$  = LOW), or use the internally generated burst address if ADV/ $\overline{LD}$  = HI (see Burst Sequence Truth tables) based on the initial address that was loaded.

For WRITE operations, Byte Write inputs (BWa, BWb, BWc, BWd) are registered on each cycle the address is either loaded externally, or advanced from the internal burst counter, data is registered two (active) cycles later.

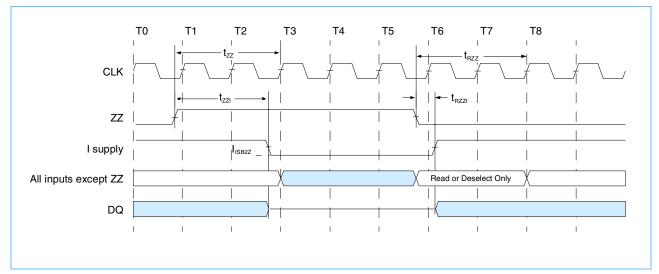

Snooze Mode is enabled by switching asynchronous signal ZZ High. When the SRAM is in Snooze mode, the outputs will go to a High-Z state, and the SRAM will draw a standby current of  $I_{SB2Z}$  after a delay of  $t_{ZZI}$ . SRAM data will be preserved during SNOOZE Mode, but any READ or WRITE operation that is pending while entering SNOOZE Mode is not guaranteed. A recovery time ( $t_{ZZR}$ ) is required before the SRAM resumes normal operation.

The SRAM operates from a single 3.3 V or 2.5 V power supply, and supports LVTTL I/O levels.

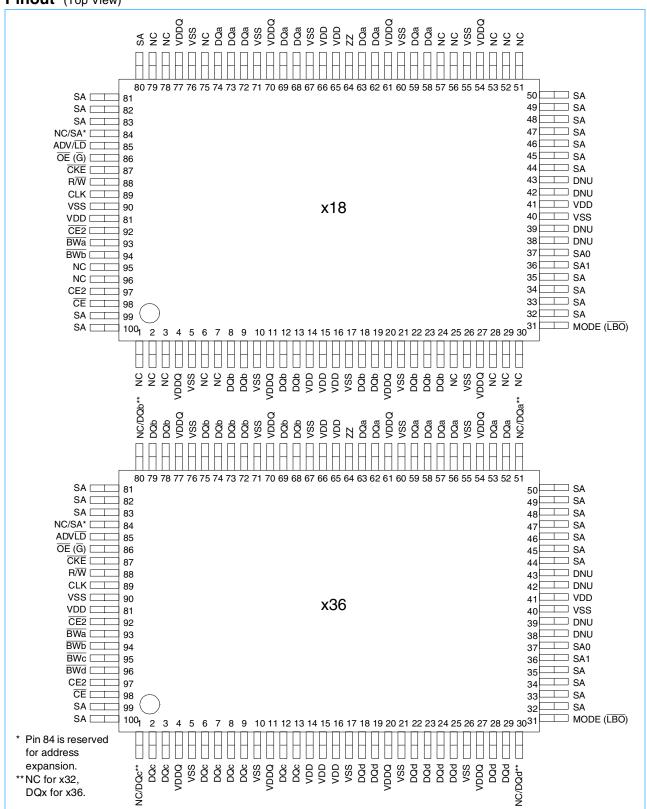

### Pinout (Top View)

# **Ordering Information** (These are all possible sorts; some may not be qualified or others added)

| Part Number       | Organization | Function       | V <sub>DD</sub> /V <sub>DDQ</sub> (Volts) | Cycle/Access (ns) |

|-------------------|--------------|----------------|-------------------------------------------|-------------------|

| IBM0418A86LQKA-6  | 512K x 18    | LVTTL Pipeline | 2.5/2.5                                   | 6.0/3.5           |

| IBM0418A86LQKA-7  | 512K x 18    | LVTTL Pipeline | 2.5/2.5                                   | 6.7/3.8           |

| IBM0418A86LQKA-7F | 512K x 18    | LVTTL Pipeline | 2.5/2.5                                   | 7.5/4.2           |

| IBM0418A86LQKA-8F | 512K x 18    | LVTTL Pipeline | 2.5/2.5                                   | 8.5/4.5           |

| IBM0418A86LQKA-10 | 512K x 18    | LVTTL Pipeline | 2.5/2.5                                   | 10.0/5.0          |

| IBM0418A86SQKA-6  | 512K x 18    | LVTTL Pipeline | 3.3/3.3                                   | 6.0/3.5           |

| IBM0418A86SQKA-7  | 512K x 18    | LVTTL Pipeline | 3.3/3.3                                   | 6.7/3.8           |

| IBM0418A86SQKA-7F | 512K x 18    | LVTTL Pipeline | 3.3/3.3                                   | 7.5/4.2           |

| IBM0418A86SQKA-8F | 512K x 18    | LVTTL Pipeline | 3.3/3.3                                   | 8.5/4.5           |

| IBM0418A86SQKA-10 | 512K x 18    | LVTTL Pipeline | 3.3/3.3                                   | 10.0/5.0          |

| IBM0436A86LQKA-6  | 256K x 36    | LVTTL Pipeline | 2.5/2.5                                   | 6.0/3.5           |

| IBM0436A86LQKA-7  | 256K x 36    | LVTTL Pipeline | 2.5/2.5                                   | 6.7/3.8           |

| IBM0436A86LQKA-7F | 256K x 36    | LVTTL Pipeline | 2.5/2.5                                   | 7.5/4.2           |

| IBM0436A86LQKA-8F | 256K x 36    | LVTTL Pipeline | 2.5/2.5                                   | 8.5/4.5           |

| IBM0436A86LQKA-10 | 256K x 36    | LVTTL Pipeline | 2.5/2.5                                   | 10.0/5.0          |

| IBM0436A86SQKA-6  | 256K x 36    | LVTTL Pipeline | 3.3/3.3                                   | 6.0/3.5           |

| IBM0436A86SQKA-7  | 256K x 36    | LVTTL Pipeline | 3.3/3.3                                   | 6.7/3.8           |

| IBM0436A86SQKA-7F | 256K x 36    | LVTTL Pipeline | 3.3/3.3                                   | 7.5/4.2           |

| IBM0436A86SQKA-8F | 256K x 36    | LVTTL Pipeline | 3.3/3.3                                   | 8.5/4.5           |

| IBM0436A86SQKA-10 | 256K x 36    | LVTTL Pipeline | 3.3/3.3                                   | 10.0/5.0          |

# **Pin Descriptions**

| Symbol                   | Туре         | Description                                                                                                                                                                                                                                                                                                                      |

|--------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK                      | Input        | <b>Clock:</b> This signal registers the address, data, chip enables, byte write enables and burst control inputs on its rising edge. All synchronous inputs must meet setup and hold times around clock's rising edge.                                                                                                           |

| CKE                      | Input        | <b>Synchronous Clock Enable:</b> This active LOW input enables the CLK input. When HIGH, the CLK input is ignored, and the previous cycle is extended.                                                                                                                                                                           |

| CE<br>CE2                | Input        | <b>Synchronous Chip enable:</b> These active LOW inputs are used to enable the device and is sampled only when a new external address is loaded (ADV/LD LOW). Double cycle deselect protocol.                                                                                                                                    |

| CE2                      | Input        | <b>Synchronous Chip enable:</b> This active HIGH input is used to enable the device and is sampled only when a new external address is loaded (ADV/\overline{LD} LOW). Double cycle deselect protocol.                                                                                                                           |

| ADV/LD                   | Input        | <b>Synchronous Address Advance/Load:</b> When LOW, a new address is loaded into the device (and Burst counter). When HIGH, the internal burst counter is advanced and used (R/W is ignored).                                                                                                                                     |

| SA0<br>SA1<br>SA         | Input        | Synchronous Address Inputs. SA0 and SA1 are the least significant Address bits, and are used to set the Burst Address counter for Burst operations.  Pin 84 is reserved as the High order Address for the 16Mb Late-Late-Write SRAM.                                                                                             |

| BWa<br>BWb<br>BWc<br>BWd | Input        | Synchronous Byte Writes: These inputs allow individual bytes to be written (LOW), or masked (HIGH) during a WRITE operation. BYTE WRITEs are registered on the same clock edge as the WRITE Address (whether it is an externally provided or internally generated Address). These inputs have no affect during a READ operation. |

| R/W                      | Input        | <b>Read/Write:</b> This synchronous input, sampled at the rising edge of CLK when ADV/ $\overline{\text{LD}}$ is low, determines whether a READ (HIGH) or WRITE (LOW) operation is initiated. For WRITE operations, the Byte Write Enable inputs provide Byte control for partial WRITE operations.                              |

| OE                       | Input        | Output Enable: This active LOW, asynchronous input enables the Output Drivers.                                                                                                                                                                                                                                                   |

| MODE(LBO)                | Input        | <b>Mode:</b> A LOW on this pin selects Linear Burst order. A HIGH or NC will default Interleaved Burst order. Do not change input state once device is operating.                                                                                                                                                                |

| DQa<br>DQb<br>DQc<br>DQd | Input/Output | <b>Data I/Os:</b> DQa is Data Input and Output for Byte "a". DQb is for Byte "b",DQc is for Byte "c" and DQd is for Byte "d".                                                                                                                                                                                                    |

| ZZ                       | Input        | Snooze Enable: This active HIGH, asynchronous input causes the chip to enter Snooze Mode, which is a low standby-current state. While ZZ is HIGH, all other inputs are ignored, and data in the memory array is retained. Pin may be left unconnected.                                                                           |

| NC                       | NC           | <b>No Connect:</b> These pins can be left unconnected, or may be connected to GND to minimize thermal impedance or any other DC input.                                                                                                                                                                                           |

| VDD                      | Supply       | Power Supply: See DC Electrical Characteristics and Recommended DC Operating Conditions for range.                                                                                                                                                                                                                               |

| VDDQ                     | Supply       | <b>Isolated Output Buffer Supply</b> : See DC Electrical Characteristics and Recommended DC Operating Conditions for range.                                                                                                                                                                                                      |

| VSS                      | Supply       | Ground: GND.                                                                                                                                                                                                                                                                                                                     |

| DNU                      | NC/Input     | <b>Do Not Use.</b> Reserved pins. These can either be left unconnected or wired to GND to improve thermal impedance                                                                                                                                                                                                              |

#### **SRAM Features**

#### Late-Late-Write

In Late-Late-Write function, WRITE data must be registered on the N+2 clock cycle and addresses and controls registered on the N base clock cycle. READ data is available in the N+1 clock cycle. READ data is valid a full cycle plus access time from the time the address is registered. WRITE data must be provided with setup time 2 cycles after the valid address. This provides 100% bus utilization. In the unique case when a read cycle occurs after a write cycle to the same address, WRITE data information is stored temporarily in holding registers. During the first write cycle preceded by a read cycle, the SRAM array will be updated with the address and data from the holding registers. Read cycle addresses are monitored to determine if read data is supplied from the SRAM array or the write buffer holding registers. By-passing the SRAM array occurs on a byte-by-byte basis. When only one byte is written during a write cycle, read data from the address last written will have new byte data from the write buffer and the remaining bytes from the SRAM array. Late-Late-Write is extremely similar to Late-Write; just one additional cycle is needed to register the write data.

#### **Burst Mode**

The IBM0418/36A86 SRAM can operate in either linear or interleave burst modes using LBO pin. Addresses are loaded via the ADV/LD pin. Once an address is loaded, it is designated as either a write or read address from the initial address load. All burst addresses produced by ADV pulses are either read or write as designated by the initial address. Only read OR write operation within a burst loaded address is supported.

#### **Power Down Mode**

Power Down Mode, or "Sleep Mode," is accomplished by switching asynchronous signal ZZ high. When powering-down the SRAM inputs must be dropped first and VDDQ must be dropped before or simultaneously with  $V_{DD}$ .

### **Power-Up Requirements**

In order to guarantee the optimum internally regulated supply voltage, the SRAM requires 50  $\mu$ s of power-up time after  $V_{DD}$  reaches its operating range. SRAM power-up requires  $V_{DD}$  to be powered before or simultaneously with  $V_{DDQ}$  and inputs after  $V_{DDQ}$ .  $V_{DDQ}$  should not exceed  $V_{DD}$  supply by more than 0.4V during power-up.

#### **Sleep Mode Operation**

Sleep mode is a low power mode initiated by bringing the asynchronous ZZ pin HIGH. During sleep mode, all other inputs are ignored and outputs are brought to a High-Z state. Sleep mode current and output High Z are guaranteed after the specified sleep mode enable time. During sleep mode, the array data contents are preserved. Sleep mode must not be initiated until after all pending operations have completed, as any pending operation is not guaranteed to properly complete after sleep mode is initiated. Sense amp data is lost. Normal operation can be resumed by bringing ZZ low, but only after specified sleep mode recovery time.

## Cycle Definition Truth Table (see notes 1, 2, 3, 4)

| Operation                        | Address<br>used | CE | CE2 | CE2 | ZZ | ADV/<br>LD | R/W | BWx | OE | CKE | CLK | DQ     | Notes      |

|----------------------------------|-----------------|----|-----|-----|----|------------|-----|-----|----|-----|-----|--------|------------|

| Deselect Cycle                   | None            | Н  | Х   | Х   | L  | L          | Х   | Х   | Х  | L   | L→H | High-Z |            |

| Deselect Cycle                   | None            | Х  | Н   | Х   | L  | L          | Х   | Х   | Х  | L   | L→H | High-Z |            |

| Deselect Cycle                   | None            | Х  | х   | L   | L  | L          | Х   | Х   | Х  | L   | L→H | High-Z |            |

| Deselect Cycle<br>(Continue)     | None            | Х  | Х   | Х   | L  | Н          | Х   | Х   | Х  | L   | L→H | High-Z | 5          |

| READ Cycle<br>(Begin Burst)      | External        | L  | L   | Н   | L  | L          | Н   | Х   | L  | L   | L→H | Q      |            |

| READ Cycle<br>(Continue Burst)   | Next            | Х  | Х   | Х   | L  | Н          | Х   | Х   | L  | L   | L→H | Q      | 5, 6       |

| No Op /Dummy READ (Begin Burst)  | External        | L  | L   | Н   | L  | L          | Н   | Х   | Н  | L   | L→H | High-Z | 7          |

| Dummy READ<br>(Continue Burst)   | Next            | Х  | Х   | Х   | L  | Н          | Х   | Х   | Н  | L   | L→H | High-Z | 5, 6, 7    |

| WRITE Cycle<br>(Begin Burst)     | External        | L  | L   | Н   | L  | L          | L   | L   | Х  | L   | L→H | D      | 8          |

| WRITE Cycle<br>(Continue Burst)  | Next            | Х  | Х   | Х   | L  | Н          | Х   | L   | Х  | L   | L→H | D      | 5, 6, 8    |

| No Op /WRITE Abort (Begin Burst) | None            | L  | L   | Н   | L  | L          | L   | Н   | Х  | L   | L→H | High-Z | 7, 8       |

| WRITE Abort<br>(Continue Burst)  | Next            | Х  | Х   | Х   | L  | Н          | Х   | Н   | Х  | L   | L→H | High-Z | 5, 6, 7, 8 |

| Clock Disabled<br>(Stall)        | Current         | Х  | Х   | Х   | L  | Х          | Х   | Х   | Х  | Н   | L→H | Held   | 9          |

| SNOOZE Mode                      | None            | Χ  | Х   | Х   | Н  | Х          | Х   | Х   | Χ  | Х   | Х   | High-Z |            |

- 1. X="Don't care", H=Logic "High", L= Logic "Low". BWx=H means all byte write inputs (BWa, BWb, BWc, BWd) are "High". BWx=L means one or more byte write signals are "Low". (see truth table for READ/WRITE commands for more info on byte enable control).

- 2. All inputs except  $\overline{\text{OE}}$  and ZZ must meet setup and hold times around the rising edge of CLK

- 3. CKE held "High" will insert wait states. Internal device registers will hold their previous values.

- 4. On-chip circuitry is included to ensure that outputs are held in High-Z during power-up.

- 5. Continue BURST Cycles are initiated with the ADV/\overline{LD} pin held high. The type of cycle that is performed (DESELECT, READ or WRITE) is determined by the initial DESELECT or Begin READ/WRITE burst cycle.

- 6. The address counter is incremented for all CONTINUE BURST cycles (see Burst Sequence truth table for Burst order and wrap information).

- 7. DUMMY READ and WRITE ABORT cycles can be considered Non-Operations or "No Ops". All BWx inputs must be High to prevent a WRITE operation from being performed.

- 8.  $\overline{\text{OE}}$  may be tied LOW to reduce the number of control pins for the SRAM. The device will automatically tri-state the output drivers during a WRITE cycle. By carefully controlling the  $\overline{\text{OE}}$  timings, cycle time improvements can be obtained.

- 9. If a Clock Disable (CKE = High) command is issued during a READ operation, the DQ bus will remain active (Low-Z). If it occurs during a WRITE operation, the bus will remain inactive (High-Z), and any pending DATA-IN is delayed by an additional cycle. No operation will be performed during the Clock Disable cycle.

# Interleaved Burst Sequence Truth Table (MODE=HI or NC)

| First Address (External) | Second Address (Internal) | Third Address (Internal) | Fourth Address (Internal) |

|--------------------------|---------------------------|--------------------------|---------------------------|

| XX00                     | XX01                      | XX10                     | XX11                      |

| XX01                     | XX00                      | XX11                     | XX10                      |

| XX10                     | XX11                      | XX00                     | XX01                      |

| XX11                     | XX10                      | XX01                     | XX00                      |

# **Linear Burst Sequence Truth Table** (MODE=LOW)

| First Address (External) | Second Address (Internal) | Third Address (Internal) | Fourth Address (Internal) |

|--------------------------|---------------------------|--------------------------|---------------------------|

| XX00                     | XX01                      | XX10                     | XX11                      |

| XX01                     | XX10                      | XX11                     | XX00                      |

| XX10                     | XX11                      | XX00                     | XX01                      |

| XX11                     | XX00                      | XX01                     | XX10                      |

## **Read/Write Command Truth Table**

| FUNCTION                   | R/W | BWa | BWb | BWc | BWd |

|----------------------------|-----|-----|-----|-----|-----|

| READ                       | Н   | Х   | Х   | Х   | Х   |

| Abort Write (No Operation) | L   | Н   | Н   | Н   | Н   |

| WRITE Byte "a"             | L   | L   | Н   | Н   | Н   |

| WRITE Byte "b"             | L   | Н   | L   | Н   | Н   |

| WRITE Byte "c"             | L   | Н   | Н   | L   | Н   |

| WRITE Byte "d"             | L   | Н   | Н   | Н   | L   |

Any combination of BWx inputs may be used during WRITE operations to perform partial Byte Writes.

Shaded area of table does not apply to the x18 part, as only BWa and BWb are provided.

## **Absolute Maximum Ratings**

| Item                         | Symbol Rating      |                               | Units | Notes |

|------------------------------|--------------------|-------------------------------|-------|-------|

| Power Supply Voltage         | $V_{DD}$           | -0.5 to 4.3                   | V     | 1     |

| Output Power Supply Voltage  | $V_{\mathrm{DDQ}}$ | -0.5 to V <sub>DD</sub>       | V     | 1     |

| Input Voltage                | V <sub>IN</sub>    | -0.5 to V <sub>DD</sub> +0.5  | V     | 1, 2  |

| DQ Input Voltage             | V <sub>DQIN</sub>  | -0.5 to V <sub>DDQ</sub> +0.5 | V     | 1     |

| Junction Temperature         | TJ                 | 150                           | °C    | 1     |

| Operating Temperature        | T <sub>A</sub>     | 0 to 70                       | °C    | 1     |

| Storage Temperature          | T <sub>STG</sub>   | -55 to +150                   | °C    | 1     |

| Short Circuit Output Current | І <sub>оит</sub>   | 25                            | mA    | 1     |

<sup>1.</sup> Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reli-

# Recommended DC Operating Conditions (T<sub>A</sub>=0 to +70 °C)

| Parameter                                     | Symbol             |      | Min.  | Тур. | Max.                   | Units | Notes |

|-----------------------------------------------|--------------------|------|-------|------|------------------------|-------|-------|

| 0 1 1 1 1                                     | V                  | 2.5V | 2.25  | 2.5  | 2.75                   | .,    | ,     |

| Supply Voltage                                | $V_{DD}$           | 3.3V | 3.0   | 3.3  | 3.63                   | V     | 1     |

|                                               | .,                 | 2.5V | 2.25  | 2.5  | $V_{DD}$               | .,    |       |

| Output Driver Supply Voltage                  | $V_{\mathrm{DDQ}}$ | 3.3V | 3.135 | 3.3  | $V_{DD}$               | V     | 1     |

|                                               | V                  | 2.5V | 1.7   | _    | V <sub>DDQ</sub> + 0.3 | .,    |       |

| Input High Voltage                            | V <sub>IH</sub>    | 3.3V | 2.0   | _    | V <sub>DDQ</sub> + 0.3 | V     | 1, 2  |

| Input Low Voltage                             | V <sub>IL</sub>    |      | -0.3  | _    | 0.8                    | V     | 1, 3  |

| Input Leakage Current                         | IL <sub>I</sub>    |      | -2.0  |      | 2.0                    | μΑ    | 5     |

| Output High Voltage (I 4 0mA)                 | V                  | 2.5V | 2.0   |      |                        | .,    |       |

| Output High Voltage (I <sub>OH</sub> =-4.0mA) | V <sub>OH</sub>    | 3.3V | 2.4   |      |                        | V     | 1, 4  |

| 0.45.41.50.7/5/15.55.7/                       | .,                 | 2.5V | _     |      | 0.2                    |       |       |

| Output Low Voltage (I <sub>OL</sub> =8.0mA)   | V <sub>OL</sub>    | 3.3V | _     |      | 0.4                    | V     | 1, 4  |

| Output Leakage Current                        | IL <sub>O</sub>    |      | -4.0  |      | 4.0                    | μΑ    |       |

<sup>2.</sup> Excludes DQ inputs.

<sup>1.</sup> All voltages referenced to V<sub>SS</sub>. All V<sub>DD</sub>, V<sub>DDQ</sub> and V<sub>SS</sub> pins must be connected.

2.  $V_{IH}(Max)DC = V_{DDQ} + 0.3 \text{ V}$ ,  $V_{IH}(Max)AC = V_{DDQ} + 0.85 \text{ V}$  (pulse width  $\leq 4.0 \text{ns}$ ).

<sup>3.</sup>  $V_{IL}(Min)DC = -0.3 \text{ V}, V_{IL}(Min)AC = -1.5 \text{ V} \text{ (pulse width } \leq 4.0 \text{ns)}$

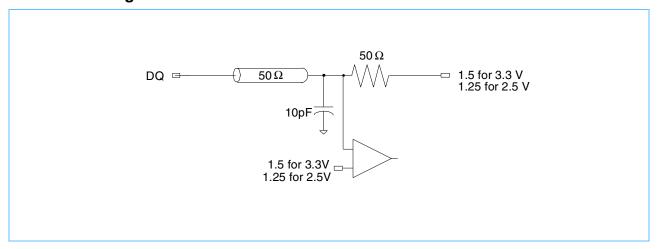

<sup>4.</sup> Driver AC characteristics are higher than the shown DC values. See AC Test Loading figure for actual test conditions.

<sup>5.</sup> MODE pin has an internal pull-up, and  $IL_I = +/-100\mu A$ .

# DC Electrical Characteristics ( $T_A=0$ to +70 °C, $V_{DD}=3.3\pm10\%$ or 2.5V $\pm10\%$ V)

| Permute                                                                                                                                                                                   | Symbol            |     |     | Max. |     |     | Units | Notes |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----|-----|------|-----|-----|-------|-------|

| Parameter                                                                                                                                                                                 |                   | -6  | -7  | -7F  | -8F | -10 |       |       |

| Average Power Supply Current - Operating Device Selected; $V_{IL} \ge all$ inputs $\ge V_{IH}$ ; Cycle time $\ge t_{KHKH}$ (min); $V_{DD}$ =max.; Outputs open                            | I <sub>DD</sub>   | 450 | 400 | 350  | 300 | 250 | mA    | 1, 2  |

| Average Power Supply Current - Idle Device Selected; $V_{SS}$ + 0.2 $\geq$ all inputs $\geq$ $V_{DD}$ - 0.2; CKE $\geq$ $V_{DD}$ - 0.2; Cycle time $\geq$ $t_{KHKH}$ (min); $V_{DD}$ =max | I <sub>DD1</sub>  | 20  | 18  | 15   | 12  | 10  | mA    | 1, 2  |

| CMOS Standby Current Device De-selected; $V_{SS}$ + 0.2 $\geq$ all inputs $\geq$ $V_{DD}$ - 0.2; All inputs static; Clocks idle; $V_{DD}$ =max                                            | I <sub>SB2</sub>  | 10  | 10  | 10   | 10  | 10  | mA    | 2     |

| TTL Standby Current Device De-selected; $V_{IL} \ge all$ inputs $\ge V_{IH}$ ; All inputs static; Clock frequency = 0; $V_{DD}$ =max                                                      | I <sub>SB3</sub>  | 25  | 25  | 25   | 25  | 25  | mA    | 2     |

| Clock Running Current Device Selected; $V_{SS}$ + 0.2 $\geq$ all inputs $\geq$ $V_{DD}$ - 0.2; Cycle time $\geq$ $t_{KHKH}$ (min); $V_{DD}$ =max                                          | I <sub>SB4</sub>  | 95  | 85  | 75   | 65  | 60  | mA    | 2     |

| SNOOZE Mode Current ZZ ≥ V <sub>IH</sub> ; V <sub>DD</sub> =max                                                                                                                           | I <sub>SB2Z</sub> | 10  | 10  | 10   | 10  | 10  | mA    |       |

I<sub>DD</sub> does not include I<sub>DDQ</sub> (output driver supply) current. Current increases with faster cycle times. I<sub>DDQ</sub> is a function of Clock Frequency and output load.

# **TQFP Thermal Characteristics**

| Item                                   | Symbol | Rating | Units |

|----------------------------------------|--------|--------|-------|

| Thermal Resistance Junction to Ambient | R⊝JA   | 32     | °C/W  |

| Thermal Resistance Junction to Case    | RΘJC   | 4      | °C/W  |

# Capacitance (T<sub>A</sub>=0 to +70 °C, $V_{DD}$ =3.3 $\pm$ 10%V, f=1MHz)

| Parameter                             | Symbol           | Test Condition        | Max | Units | Notes |

|---------------------------------------|------------------|-----------------------|-----|-------|-------|

| Control and Address Input Capacitance | C <sub>IN</sub>  | V <sub>IN</sub> = 0V  | 4   | pF    | 1     |

| Data I/O Capacitance (DQ0-DQ35)       | C <sub>OUT</sub> | V <sub>OUT</sub> = 0V | 5   | pF    | 1     |

| Capacitance Values are sampled.       |                  |                       |     |       |       |

<sup>2.</sup> See Cycle Definition Truth Table for complete definition of "Selected" and "Deselected" cycles.

# **AC Test Conditions** (T<sub>A</sub>=0 to +70 °C, $V_{DD\ \&}V_{DDQ}$ =3.3 $\pm$ 10% V, See AC Test Loading figure below.)

| Parameter                      | Symbol           | V <sub>DD</sub> /V <sub>DDQ</sub> ± 10% | Conditions | Units | Notes |

|--------------------------------|------------------|-----------------------------------------|------------|-------|-------|

| Outrot Driver Complex Valters  | M                | 2.5V                                    | 2.5        | V     |       |

| Output Driver Supply Voltage   | $V_{DDQ}$        | 3.3V                                    | 1.8        | V     |       |

|                                | V                | 2.5V                                    | 2.0        | .,    |       |

| Input High Level               | V <sub>IH</sub>  | 3.3V                                    | 1.5        | V     |       |

| Input Low Level                | V <sub>IL</sub>  |                                         | VSS        | V     |       |

| Land The land Defended Welling |                  | 2.5V                                    | 1.25       | .,    |       |

| Input Timing Reference Voltage |                  | 3.3V                                    | 1.5        | V     |       |

| O Level Defense as Welliams    | V                | 2.5V                                    | 1.25       | V     |       |

| Output Reference Voltage       | V <sub>REF</sub> | 3.3V                                    | 0.90       | V     |       |

| Input Rise Time                | T <sub>R</sub>   |                                         | 0.5        | ns    |       |

| Input Fall Time                | T <sub>F</sub>   |                                         | 0.5        | ns    |       |

# **AC Test Loading**

# AC Characteristics (T<sub>A</sub>=0 to +70 °C, $V_{DD\ \&}V_{DDQ\ =}$ 2.5 or 3.3V)

| <u>.</u> .      |                                    | Symbol             | -6  |                      | -7  |                       | -7F |                       | -8F |                       | -10 |                       |       |       |

|-----------------|------------------------------------|--------------------|-----|----------------------|-----|-----------------------|-----|-----------------------|-----|-----------------------|-----|-----------------------|-------|-------|

|                 | Parameter                          |                    | Min | Max                  | Min | Max                   | Min | Max                   | Min | Max                   | Min | Max                   | Units | Notes |

| Clock           | Cycle Time                         | t <sub>KHKH</sub>  | 6.0 | _                    | 6.7 | _                     | 7.5 | _                     | 8.5 | _                     | 10  | _                     | ns    |       |

|                 | Clock High Pulse Width             | t <sub>KHKL</sub>  | 2.0 | _                    | 2.2 | _                     | 2.5 | _                     | 2.5 | _                     | 3.0 | _                     | ns    |       |

|                 | Clock Low Pulse Width              | t <sub>KLKH</sub>  | 2.0 | _                    | 2.2 | _                     | 2.5 | _                     | 2.5 | _                     | 3.0 | _                     | ns    |       |

|                 | Clock Enable Set-up time           | t <sub>EVKH</sub>  | 1.5 | _                    | 1.5 | _                     | 1.5 | _                     | 1.5 | _                     | 1.5 | _                     | ns    |       |

|                 | Clock Enable Hold time             | t <sub>KHEX</sub>  | 0.5 | _                    | 0.5 | _                     | 0.5 | _                     | 0.5 | _                     | 0.5 | _                     | ns    |       |

| Output<br>Times | Clock to Output Valid              | t <sub>KHQV</sub>  | _   | 3.5                  | _   | 3.8                   | _   | 4.2                   | _   | 4.5                   | _   | 5.0                   | ns    | 1     |

|                 | Clock to Output Invalid            | t <sub>KHQX</sub>  | 1.5 | _                    | 1.5 | _                     | 1.5 | _                     | 1.5 | _                     | 1.5 | _                     | ns    | 1     |

|                 | Clock High to Output Low-Z         | t <sub>KHQX1</sub> | 1.5 | _                    | 1.5 | _                     | 1.5 | _                     | 1.5 | _                     | 1.5 | _                     | ns    | 1, 2  |

|                 | Clock High to Output High-Z        | t <sub>KHQZ</sub>  | 1.5 | 3.0                  | 1.5 | 3.0                   | 1.5 | 3.5                   | 1.5 | 3.5                   | 1.5 | 3.5                   | ns    | 1, 2  |

|                 | Output Enable to Output<br>Valid   | t <sub>GLQV</sub>  | _   | 3.5                  | _   | 4.0                   | _   | 4.2                   | _   | 4.5                   | _   | 5.0                   | ns    | 1     |

|                 | Output Enable to Low-Z             | t <sub>GLQX</sub>  | 0.0 | _                    | 0.0 | _                     | 0.0 | _                     | 0.0 | _                     | 0.0 | _                     | ns    | 1, 2  |

|                 | Output Enable to High-Z            | t <sub>GHQZ</sub>  | _   | 3.0                  | _   | 3.0                   | _   | 3.5                   | _   | 4.0                   | _   | 4.0                   | ns    | 1, 2  |

| Setup<br>Times  | Address Setup Time                 | t <sub>AVKH</sub>  | 1.5 | _                    | 1.5 | _                     | 1.5 | _                     | 1.5 | _                     | 1.5 | _                     | ns    |       |

|                 | Sync Select Setup Time             | t <sub>CVKH</sub>  | 1.5 | _                    | 1.5 | _                     | 1.5 | _                     | 1.5 | _                     | 1.5 | _                     | ns    |       |

|                 | Write Enables Setup Time           | t <sub>WVKH</sub>  | 1.5 | _                    | 1.5 | _                     | 1.5 | _                     | 1.5 | _                     | 1.5 | _                     | ns    |       |

|                 | Data In Setup Time                 | t <sub>DVKH</sub>  | 1.5 | _                    | 1.5 | _                     | 1.5 | _                     | 1.5 | _                     | 1.5 | _                     | ns    |       |

|                 | Address Hold Time                  | t <sub>KHAX</sub>  | 0.5 | _                    | 0.5 | _                     | 0.5 | _                     | 0.5 | _                     | 0.5 | _                     | ns    |       |

| Hold            | Sync Select Hold Time              | t <sub>KHCX</sub>  | 0.5 | _                    | 0.5 | _                     | 0.5 | _                     | 0.5 | _                     | 0.5 | _                     | ns    |       |

| Times           | Write Enables Hold Time            | t <sub>KHWX</sub>  | 0.5 | _                    | 0.5 | _                     | 0.5 | _                     | 0.5 | _                     | 0.5 | _                     | ns    |       |

|                 | Data In Hold Time                  | t <sub>KHDX</sub>  | 0.5 | _                    | 0.5 | _                     | 0.5 | _                     | 0.5 | _                     | 0.5 | _                     | ns    |       |

| Snooz<br>e Mode | ZZ active to input ignored         | t <sub>ZZ</sub>    | 0.0 | 2(t <sub>KHKH)</sub> | 0.0 | 2(t <sub>KHKH</sub> ) | ns    |       |

|                 | ZZ inactive to input sampled       | t <sub>RZZ</sub>   | 0.0 | 2(t <sub>KHKH)</sub> | 0.0 | 2(t <sub>KHKH</sub> ) | ns    |       |

|                 | ZZ active to snooze current        | t                  | 0.0 | 2(t <sub>KHKH)</sub> | 0.0 | 2(t <sub>KHKH</sub> ) | ns    |       |

|                 | ZZ inactive to exit snooze current | t <sub>RZZI</sub>  | 0.0 | _                    | 0.0 | _                     | 0.0 | _                     | 0.0 | _                     | 0.0 | _                     | ns    |       |

<sup>1.</sup> See AC Test Loading figure on page 10.

<sup>2.</sup> This parameter is sampled. Transition is measured  $\pm\,200\text{mV}$  from steady-state.

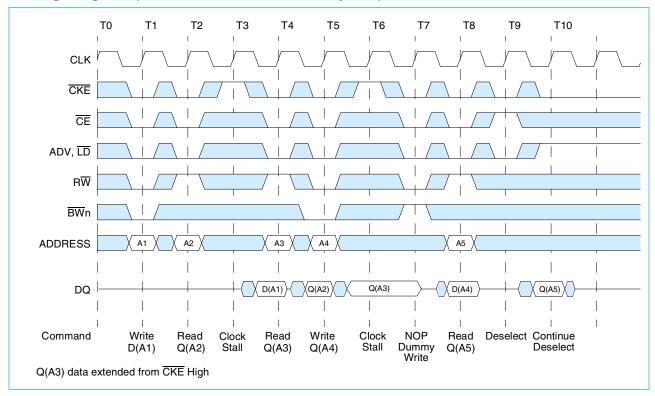

# Timing Diagram (NOP, Stall, and Deselect Cycles)

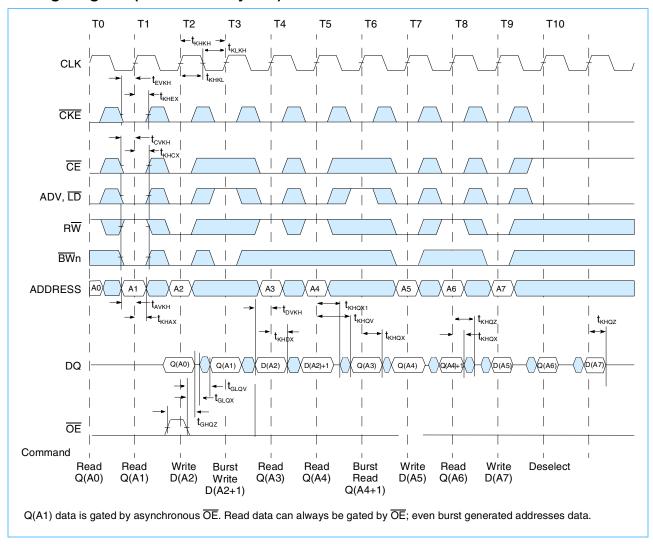

# **Timing Diagram (Read Write Cycles)**

# **Timing Diagram (Sleep Mode)**

# **Revision Log**

| Rev     | Contents of Modification                                                                                                                      |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 8/26/99 | Initial public release (00).                                                                                                                  |

| 9/16/99 | Corrected V <sub>DD</sub> /V <sub>DDQ</sub> column in Ordering Information table. Release document version 01.                                |

| 9/27/99 | Changed name of product to Synchronous Communication SRAM. Fixed notes on Cycle Definition Truth Table on page 6 Release document version 02. |

# IBM ®

© Copyright International Business Machines Corporation 1999.

All Rights Reserved

Printed in the United States of America August 1999

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both.

IBM

IBM logo

PowerPC™

Other company, product and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in implantation or other life support applications where malfunction may result in injury or death to persons. The information contained in this document does not affect or change IBM's product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS.

In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM Microelectronics Division 1580 Route 52, Bldg. 504 Hopewell Junction, NY 12533-6351

The IBM home page can be found at http://www.ibm.com

The IBM Microelectronics Division home page can be found at http://www.chips.ibm.com

llwp.02 9/27/99