#### ADVANCED INFORMATION

# 54F/74F377 Octal D Flip-Flop with Clock Enable

#### **General Description**

The 'F377 has eight edge-triggered, D-type flip-flops with individual D inputs and Q outputs. The common buffered Clock (CP) input loads all flip-flops simultaneously, when the Clock Enable (CE) is LOW.

The register is fully edge-triggered. The state of each D input, one setup time before the LOW-to-HIGH clock transition, is transferred to the corresponding flip-flop's Q output. The  $\overline{\text{CE}}$  input must be stable only one setup time prior to the LOW-to-HIGH clock transition for predictable operation

#### **Features**

- Ideal for addressable register applications

- Clock enable for address and data synchronization applications

- Eight edge-triggered D flip-flops

- Buffered common clock

- See 'F273 for master reset version

- See 'F373 for transparent latch version

- See 'F374 for TRI-STATE® version

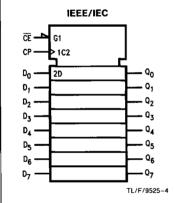

### Logic Symbols

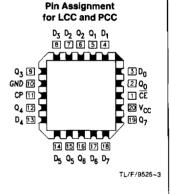

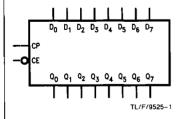

## **Connection Diagrams**

#### Mode Select-Function Table

| Operating Mode       | Inputs |        |                | Output                 |

|----------------------|--------|--------|----------------|------------------------|

|                      | СР     | CE     | D <sub>n</sub> | Qn                     |

| Load "1"             |        | 1      | h              | Н                      |

| Load "0"             |        | - I    | ı              | L                      |

| Hold<br>(Do Nothing) | X      | h<br>H | ×              | No Change<br>No Change |

$\begin{array}{ll} H \ = \ HIGH \ Voltage \ Level \\ h \ = \ HIGH \ Voltage \ Level \ one \ setup \ time \ prior \ to \\ the \ LOW-to-HIGH \ Clock \ Transition \end{array}$

L = LOW Voltage Level

I = LOW Voltage Level one setup time prior to the LOW-to-HiGH Clock Transition

X = Immaterial

= LOW-to-HIGH Clock Transition

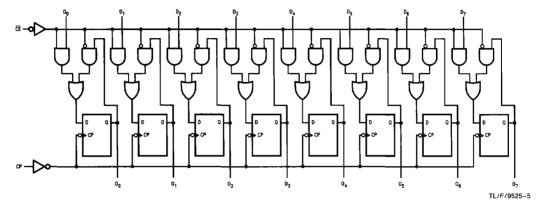

## **Logic Diagram**

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.