# DS3647A Quad TRI-STATE® MOS Memory I/O Register

#### **General Description**

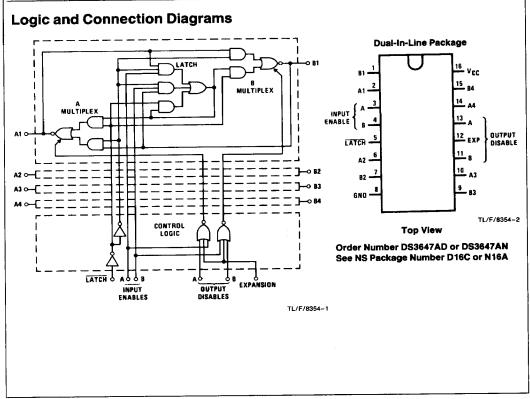

The DS3647A is a 4-bit I/O buffer register intended for use in MOS memory systems. This circuit employs a fall-through latch for data storage. This method of latching captures the data in parallel with the output, thus eliminating the delays encountered in other designs. This circuit uses Schottky-clamped transistor logic for minimum propagation delay and employs PNP input transistors so that input currents are low, allowing a large fan-out for this circuit which is needed in a memory system.

Two pins per bit are provided, and data transfer is bi-directional so that the register can handle both input and output data. The direction of data flow is controlled through the input enables. The latch control, when taken low, will cause the register to hold the data present at that time and display it at the outputs. Data can be latched into the register independent of the output disables or EXPANSION input. Either or both of the outputs may be taken to the high-impedance state with the output disables. The EXPANSION pin disables both outputs to facilitate multiplexing with other I/O registers on the same data lines.

The DS3647A features TRI-STATE outputs. The "B" port outputs are designed for use in bus organized data transmission systems and can sink 80 mA and source - 5.2 mA.

Data going from port "A" to port "B" and from "B" to port "A" is inverted in the DS3647A.

#### **Features**

- PNP inputs minimize loading

- Fall-through latch design

- Propagation delay of only 15 ns

- TRI-STATE outputs

- EXPANSION control

- Bi-directional data flow

- TTL compatible

- Transmission line driver output

Units

٧

°C

Max

5.5

+70

4.5

0

#### 5

| Absolute Maximum Ratings (Note 1)                        |

|----------------------------------------------------------|

| If Military/Aerospace specified devices are required,    |

| please contact the National Semiconductor Sales          |

| Office/Distributors for availability and specifications. |

Supply Voltage

Input Voltage

-1.5V to +7V

Storage Temperature Range

-65° to +150°C

Maximum Power Dissipation\* at 25°C

Molded Package

1476 mW

Lead Temperature (Soldering, 10 seconds)

300°C

**Operating Conditions**

Supply Voltage (V<sub>CC</sub>)

Temperature (T<sub>A</sub>)

DS3647A

### Electrical Characteristics (Notes 2 and 3)

| Symbol                                     | Parameter                              | Conditions                                                            |                         | Min | Тур  | Max   | Units |

|--------------------------------------------|----------------------------------------|-----------------------------------------------------------------------|-------------------------|-----|------|-------|-------|

| V <sub>IN(1)</sub> Logic "1" Input Voltage |                                        |                                                                       |                         | 2.0 |      |       | V     |

| V <sub>IN(0)</sub>                         | Logic "0" Input Voltage                |                                                                       |                         |     |      | 0.8   | V     |

| l <sub>IN(1)</sub>                         | Logic "1" Input Current                |                                                                       | Latch, Disable Inputs   |     | 0.1  | 40    | μΑ    |

|                                            |                                        | V <sub>CC</sub> =5.5V, V <sub>IN</sub> =5.5V                          | Expansion               |     | 0.2  | 80    | μА    |

|                                            |                                        | 100 0.00, VIN 0.00                                                    | A Ports, B Ports        |     | 0.2  | 100   | μА    |

|                                            |                                        |                                                                       | Enable Inputs           |     | 0.4  | 200   | μА    |

| I <sub>IN(0)</sub>                         | Logic "0" Input Current                |                                                                       | Latch, Disable Inputs   |     | -25  | -250  | μА    |

|                                            |                                        | V <sub>CC</sub> =5.5V, V <sub>IN</sub> =0.5V                          | Expansion               |     | -50  | -500  | μА    |

|                                            |                                        | 100 0.01, 11N 0.01                                                    | A Ports, B Ports        |     | -50  | -500  | μА    |

|                                            |                                        | Enable, Inputs                                                        |                         |     | -0.1 | -1.25 | mA    |

| VCLAMP                                     | Input Clamp Voltage                    | V <sub>CC</sub> =4.5V, I <sub>IN</sub> = -18 mA                       |                         |     | -0.6 | -1.2  | ٧     |

| V <sub>OL(A)</sub>                         | Logic "0" Output Voltage<br>A Ports    | V <sub>CC</sub> =4.5V, I <sub>OL</sub> =20 mA                         |                         |     | 0.4  | 0.5   | ٧     |

| V <sub>OL(B)</sub>                         | Logic "0" Output Voltage               | V <sub>CC</sub> =4.5V                                                 | I <sub>OL</sub> =30 mA  |     | 0.3  | 0.4   | ٧     |

| • ОЦВ)                                     | B Ports                                | 4.50                                                                  | I <sub>OL</sub> = 50 mA |     | 0.4  | 0.5   | ٧     |

| V <sub>OH(A)</sub>                         | Logic "1" Output Voltage               | I <sub>OH</sub> = -1 mA                                               | V <sub>CC</sub> =5V     | 3.0 | 3.4  |       | ٧     |

| - 011(A)                                   | A Ports                                | On Thirt                                                              | V <sub>CC</sub> =4.5V   | 2.5 | 3.4  |       | ٧     |

| V <sub>OH(B)</sub>                         | Logic "1" Output Voltage               | $I_{OH} = -5.2 \text{ mA, (Note 4)}$                                  | V <sub>CC</sub> =5V     | 2.9 | 3.3  |       | ٧     |

| O(1,0)                                     | B Ports                                | V <sub>CC</sub> =4.5V                                                 |                         | 2.4 | 3.3  |       | >     |

| I <sub>OS(A)</sub>                         | Output Short-Circuit Current<br>A Port | V <sub>CC</sub> = 4.5V to 5.5V, V <sub>OUT</sub> = 0V, (Note 4)       |                         | -50 | -80  | -120  | mA    |

| I <sub>OS(B)</sub>                         | Output Short-Circuit Current B Port    | V <sub>CC</sub> = 4.5V to 5.5V, V <sub>OUT</sub> = 0V, (Note 4)       |                         | -70 | -120 | -180  | mA    |

| lcc                                        | Power Supply Current                   | Exp=3V, A Ports=0V,<br>B Ports Open, All Other Pins=0V                | DS3647A                 |     | 100  | 140   | mA    |

|                                            |                                        | Enable A, Latch = 3V, A Ports = 0V, B Ports Open, All Other Pins = 0V | DS3647A                 |     | 70   | 105   | mA    |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

Note 2: Unless otherwise specified min/max limits apply across the 0°C to +70°C range. All typicals are given for V<sub>CC</sub>=5V and T<sub>A</sub>=25°C.

Note 3: All currents into device pins shown as positive, out of device pins as negative, all voltages referenced to ground unless otherwise noted.

Note 4: Only one output at a time should be shorted.

<sup>\*</sup>Derate molded package 10.0 mW/\* C above 25°C.

| Symbol                                            | Parameter                                          | Conditions                                                    | Min | Тур | Max | Units |

|---------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------|-----|-----|-----|-------|

| DATA TRA                                          | NSFER B PORT TO A PORT                             |                                                               |     |     |     |       |

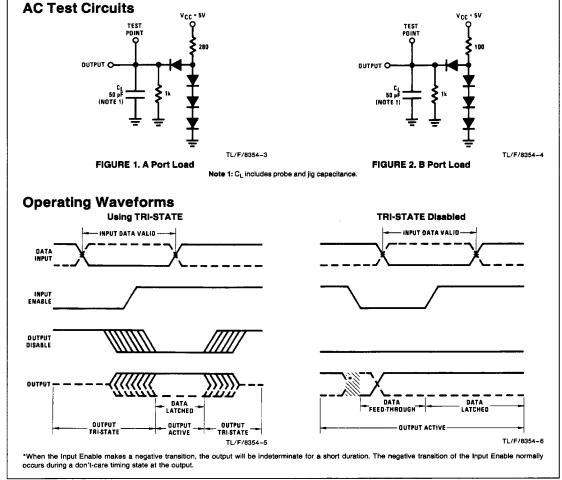

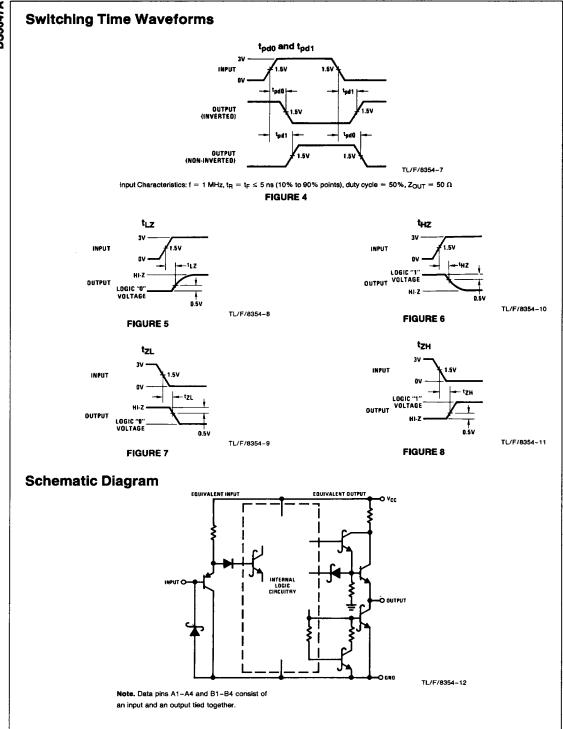

| t <sub>pd0</sub>                                  | Propagation Delay to a Logic "0"                   | CL=50 pF, $R_L$ =280 $\Omega$ , (Figures 1 and 4)             |     | 7.5 | 15  | ns    |

| t <sub>pd1</sub> Propagation Delay to a Logic "1" |                                                    | $C_L = 50 \text{ pF}, R_L = 280\Omega,$<br>(Figures 1 and 4)  |     | 6.0 | 12  | ns    |

| A PORT CO                                         | ONTROL FROM OUTPUT DISABLE A IN                    | PUT                                                           |     |     |     |       |

| t <sub>LZ</sub>                                   | Delay to High Impedance from Logic "0"             | (Figures 1 and 5)                                             |     | 13  | 20  | ns    |

| t <sub>HZ</sub>                                   | Delay to High Impedance from Logic "1"             | (Figures 1 and 6)                                             |     | 14  | 20  | ns    |

| tzL                                               | Delay to Logic "0" from High<br>Impedance          | (Figures 1 and 7)                                             |     | 10  | 15  | ns    |

| t <sub>ZH</sub>                                   | Delay to Logic "1" from High<br>Impedance          | (Figures 1 and 8)                                             |     | 25  | 35  | ns    |

| DATA TRA                                          | NSFER A PORT TO B PORT, DS3647A                    |                                                               |     |     |     |       |

| t <sub>pd0</sub>                                  | Propagation Delay to a Logic "0"                   | $C_L = 50 \text{ pF}, R_L = 100 \Omega,$<br>(Figures 2 and 4) |     | 6.5 | 12  | ns    |

| t <sub>pd1</sub>                                  | Propagation Delay to a Logic "1"                   | $C_L = 50 \text{ pF}, R_L = 100 \Omega,$<br>(Figures 2 and 4) |     | 8.0 | 15  | ns    |

| B PORT C                                          | ONTROL FROM OUTPUT DISABLE B IN                    | IPUT, DS3647A                                                 |     |     |     | ,     |

| t <sub>LZ</sub>                                   | Delay to High Impedance from Logic "0"             | (Figures 2 and 5)                                             |     | 15  | 25  | ns    |

| t <sub>HZ</sub>                                   | Delay to High Impedance from Logic "1"             | (Figures 2 and 6)                                             |     | 14  | 20  | ns    |

| t <sub>ZL</sub>                                   | Delay to Logic "0" from High<br>Impedance          | (Figures 2 and 7)                                             |     | 10  | 16  | ns    |

| <sup>t</sup> zH                                   | Delay to Logic "1" from High<br>Impedance          | (Figures 2 and 8)                                             |     | 25  | 35  | ns    |

| LATCH SE                                          | T-UP AND HOLD TIMES, ALL DEVICES                   |                                                               | ,   |     |     |       |

| t <sub>SET-UP</sub>                               | Set-Up Time of Data Input Before<br>Latch Goes Low |                                                               | 5   | 0   |     | ns    |

| tHOLD                                             | Hold Time of Data Input After Latch Goes Low       |                                                               | 10  | 5   |     | ns    |

## **Product Description**

| Device Number | B Port To A Port<br>Function | A Port To B Port<br>Function | A Port Outputs | B Port Outputs |

|---------------|------------------------------|------------------------------|----------------|----------------|

| DS3647A       | Inverting                    | Inverting                    | TRI-STATE      | TRI-STATE      |

| Truth Table      |   |       |   |                        |   |         |                  |                                                             |

|------------------|---|-------|---|------------------------|---|---------|------------------|-------------------------------------------------------------|

| Input<br>Enables |   | · I I |   | Output  Latch Disables |   | A Ports | B Ports<br>B1-B4 | Comments                                                    |

| A                | В |       | Α | В                      |   | A 1-A4  | B 1-04           |                                                             |

| 1                | 0 | 1     | 0 | 0                      | 0 | Hi-Z    | Ā                | Data in on A, output to B                                   |

| 0                | 1 | 1     | 0 | 0                      | 0 | B       | Hi-Z             | Data in on B, output to A                                   |

| 1                | 0 | 0     | 0 | 0                      | 0 | Hi-Z    | Ā                | Data stored which is present when latch goes low            |

| 0                | 1 | 0     | 0 | 0                      | 0 | B       | Hî-Z             | Data stored which is present when latch goes low            |

| 1                | 0 | x     | 0 | 1                      | 0 | Hi-Z    | Hi-Z             | Both A and B in Hi-Z state,<br>Data in on A, may be latched |

| 0                | 1 | х     | 1 | 0                      | 0 | Hi-Z    | Hi-Z             | Both A and B in Hi-Z state,<br>Data in on B, may be latched |

| ×                | × | ×     | × | х                      | 1 | Hi-Z    | Hi-Z             | Both A and B in Hi-Z state                                  |

5-31

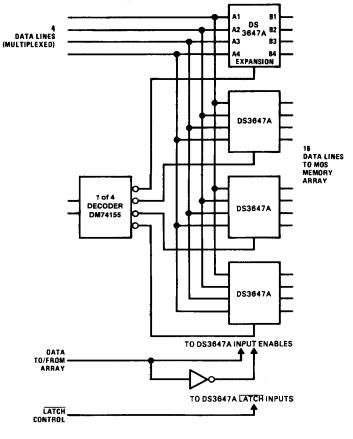

## **Typical Application**

The diagram below shows how the DS3647A can be used as a register capable of multiplexing data lines.

TL/F/8354-13

5-33