# **Rochester Electronics Manufactured Components**

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceed the OCM data sheet.

# **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-35835

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

• Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

August 1986 Revised March 2000

# DM74LS74A Dual Positive-Edge-Triggered D Flip-Flops with Preset, Clear and Complementary Outputs

#### **General Description**

FAIRCHILD

SEMICONDUCTOR

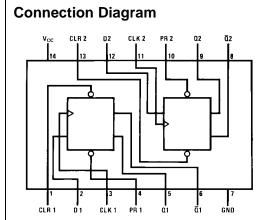

This device contains two independent positive-edge-triggered D flip-flops with complementary outputs. The information on the D input is accepted by the flip-flops on the positive going edge of the clock pulse. The triggering occurs at a voltage level and is not directly related to the transition time of the rising edge of the clock. The data on the D input may be changed while the clock is LOW or HIGH without affecting the outputs as long as the data setup and hold times are not violated. A low logic level on the preset or clear inputs will set or reset the outputs regardless of the logic levels of the other inputs.

#### **Ordering Code:**

| Order Number | Package Number | Package Description                                                         |

|--------------|----------------|-----------------------------------------------------------------------------|

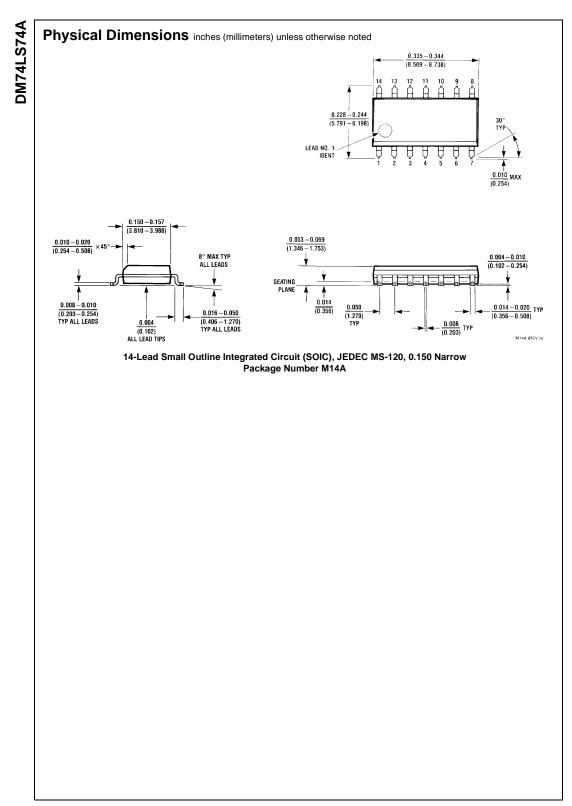

| DM74LS74AM   | M14A           | 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow |

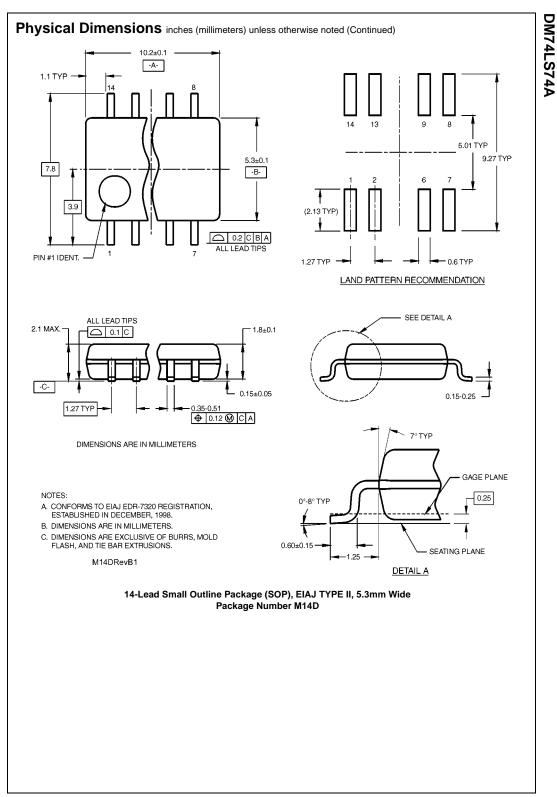

| DM74LS85ASJ  | M14D           | 14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide               |

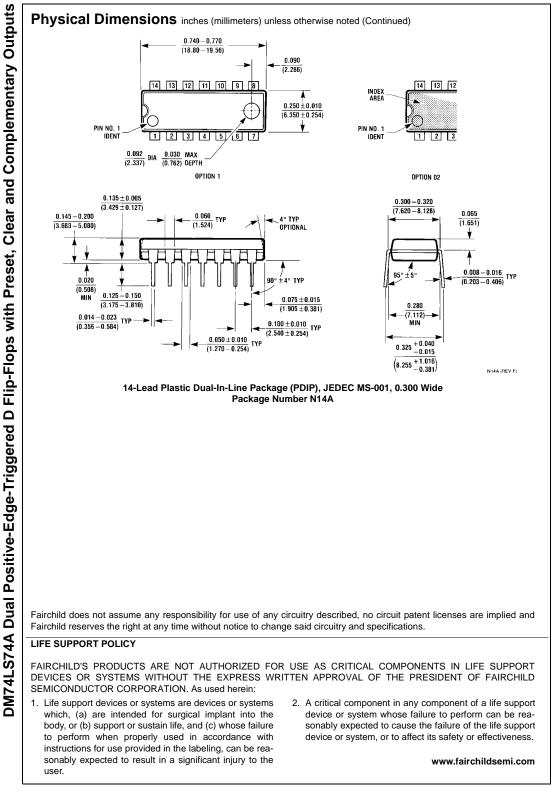

| DM74LS74AN   | N14A           | 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide       |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

#### Function Table

| Inputs |     |            |   | Outputs        |                  |  |  |

|--------|-----|------------|---|----------------|------------------|--|--|

| PR     | CLR | CLK        | D | Q              | Q                |  |  |

| L      | Н   | Х          | Х | Н              | L                |  |  |

| Н      | L   | Х          | Х | L              | Н                |  |  |

| L      | L   | Х          | Х | H (Note 1)     | H (Note 1)       |  |  |

| н      | н   | $\uparrow$ | Н | н              | L                |  |  |

| н      | н   | $\uparrow$ | L | L              | н                |  |  |

| Н      | н   | L          | Х | Q <sub>0</sub> | $\overline{Q}_0$ |  |  |

H = HIGH Logic Level X = Either LOW or HIGH Logic Level

L = LOW Logic Level

↑ = Positive-going Transition

$Q_0$  = The output logic level of Q before the indicated input conditions were established.

Note 1: This configuration is nonstable; that is, it will not persist when either the preset and/or clear inputs return to their inactive (HIGH) level.

DS006373

© 2000 Fairchild Semiconductor Corporation

www.fairchildsemi.com

## Absolute Maximum Ratings(Note 2)

| Supply Voltage                       | 7V              |

|--------------------------------------|-----------------|

| Input Voltage                        | 7\/             |

| Operating Free Air Temperature Range | 0°C to +70°C    |

|                                      |                 |

| Storage Temperature Range            | –65°C to +150°C |

Note 2: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

## **Recommended Operating Conditions**

| Symbol          | Parame                         | Min        | Nom  | Max | Units |     |

|-----------------|--------------------------------|------------|------|-----|-------|-----|

| / <sub>cc</sub> | Supply Voltage                 |            | 4.75 | 5   | 5.25  | V   |

| VIH             | HIGH Level Input Voltage       |            | 2    |     |       | V   |

| V <sub>IL</sub> | LOW Level Input Voltage        |            |      |     | 0.8   | V   |

| ОН              | HIGH Level Output Curre        | ent        |      |     | -0.4  | mA  |

| l <sub>OL</sub> | LOW Level Output Current       |            |      |     | 8     | mA  |

| f<br>CLK        | Clock Frequency (Note 3)       |            | 0    |     | 25    | MHz |

| f<br>CLK        | Clock Frequency (Note 4)       |            | 0    |     | 20    | MHz |

| t <sub>W</sub>  | Pulse Width                    | Clock HIGH | 18   |     |       |     |

|                 | (Note 3)                       | Preset LOW | 15   |     |       | ns  |

|                 |                                | Clear LOW  | 15   |     |       |     |

| t <sub>W</sub>  | Pulse Width                    | Clock HIGH | 25   |     |       |     |

|                 | (Note 4)                       | Preset LOW | 20   |     |       | ns  |

|                 |                                | Clear LOW  | 20   |     |       |     |

| tsu             | Setup Time (Note 3)(Note 5)    |            | 20↑  |     |       | ns  |

| su              | Setup Time (Note 4)(Not        | ie 5)      | 25↑  |     |       | ns  |

| Н               | Hold Time (Note 5)(Note 6)     |            | 0↑   |     |       | ns  |

| T <sub>A</sub>  | Free Air Operating Temperature |            | 0    |     | 70    | °C  |

**Note 3:**  $C_L = 15 \text{ pF}, R_L = 2 \text{ k}\Omega, T_A = 25^{\circ}\text{C}, \text{ and } V_{CC} = 5\text{V}.$ **Note 4:**  $C_L = 50 \text{ pF}, R_L = 2 \text{ k}\Omega, T_A = 25^{\circ}\text{C}, \text{ and } V_{CC} = 5\text{V}.$

**Note 4.**  $O_{C} = 30 \text{ pr}$ ,  $N_{C} = 2 \text{ Ns2}$ ,  $N_{A} = 23 \text{ O}$ , and  $V_{CC} = 30$ .

Note 5: The symbol  $(\uparrow)$  indicates the rising edge of the clock pulse is used for reference.

Note 6:  $T_A = 25^{\circ}C$  and  $V_{CC} = 5V$ .

| Symbol          | Parameter                    | Conditions                                                   |        | Min | Typ<br>(Note 7) | Мах  | Units |

|-----------------|------------------------------|--------------------------------------------------------------|--------|-----|-----------------|------|-------|

| VI              | Input Clamp Voltage          | $V_{CC} = Min, I_I = -18 mA$                                 |        |     | -1.5            | V    |       |

| V <sub>ОН</sub> | HIGH Level<br>Output Voltage | $V_{CC} = Min, I_{OH} = Max$<br>$V_{IL} = Max, V_{IH} = Min$ | 2.7    | 3.4 |                 | V    |       |

| V <sub>OL</sub> | LOW Level<br>Output Voltage  | $V_{CC} = Min, I_{OL} = Max$<br>$V_{IL} = Max, V_{IH} = Min$ |        |     | 0.35            | 0.5  | V     |

|                 |                              | $I_{OL} = 4 \text{ mA}, V_{CC} = \text{Min}$                 |        |     | 0.25            | 0.4  |       |

| I <sub>I</sub>  | Input Current @ Max          | V <sub>CC</sub> = Max                                        | Data   |     |                 | 0.1  |       |

|                 | Input Voltage                | $V_1 = 7V$                                                   | Clock  |     |                 | 0.1  | mA    |

|                 |                              |                                                              | Preset |     |                 | 0.2  | IIIA  |

|                 |                              |                                                              | Clear  |     |                 | 0.2  |       |

| I <sub>IH</sub> | HIGH Level                   | V <sub>CC</sub> = Max                                        | Data   |     |                 | 20   |       |

|                 | Input Current                | $V_{1} = 2.7V$                                               | Clock  |     |                 | 20   |       |

|                 |                              |                                                              | Clear  |     | 1               | 40   | μA    |

|                 |                              |                                                              | Preset |     | 1 1             | 40   |       |

| IIL             | LOW Level                    | V <sub>CC</sub> = Max                                        | Data   |     |                 | -0.4 |       |

|                 | Input Current                | $V_I = 0.4V$                                                 | Clock  |     |                 | -0.4 | mA    |

|                 |                              |                                                              | Preset |     |                 | -0.8 | mA    |

|                 |                              |                                                              | Clear  |     |                 | -0.8 |       |

| I <sub>OS</sub> | Short Circuit Output Current | V <sub>CC</sub> = Max (Note 8)                               | 1      | -20 | 1               | -100 | mA    |

| I <sub>CC</sub> | Supply Current               | V <sub>CC</sub> = Max (Note 9)                               |        |     | 4               | 8    | mA    |

Note 7: All typicals are at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

**Note 8:** Not more than one output should be shorted at a time, and the duration should not exceed one second. For devices, with feedback from the outputs, where shorting the outputs to ground may cause the outputs to change logic state an equivalent test may be performed where  $V_0 = 2.125V$  with the minimum and maximum limits reduced by one half from their stated values. This is very useful when using automatic test equipment. **Note 9:** With all outputs OPEN,  $I_{CC}$  is measured with CLOCK grounded after setting the Q and  $\overline{Q}$  outputs HIGH in turn.

## **Switching Characteristics**

at  $V_{CC} = 5V$  and  $T_A = 25^{\circ}C$

| Symbol           |                                                    | From (Input)<br>To (Output)  |                        |     |                        |     |       |

|------------------|----------------------------------------------------|------------------------------|------------------------|-----|------------------------|-----|-------|

|                  | Parameter                                          |                              | C <sub>L</sub> = 15 pF |     | C <sub>L</sub> = 50 pF |     | Units |

|                  |                                                    |                              | Min                    | Max | Min                    | Max |       |

| f <sub>MAX</sub> | Maximum Clock Frequency                            |                              | 25                     |     | 20                     |     | MHz   |

| t <sub>PLH</sub> | Propagation Delay Time<br>LOW-to-HIGH Level Output | Clock to Q or $\overline{Q}$ |                        | 25  |                        | 35  | ns    |

| t <sub>PHL</sub> | Propagation Delay Time<br>HIGH-to-LOW Level Output | Clock to Q or $\overline{Q}$ |                        | 30  |                        | 35  | ns    |

| t <sub>PLH</sub> | Propagation Delay Time<br>LOW-to-HIGH Level Output | Preset to Q                  |                        | 25  |                        | 35  | ns    |

| t <sub>PHL</sub> | Propagation Delay Time<br>HIGH-to-LOW Level Output | Preset to $\overline{Q}$     |                        | 30  |                        | 35  | ns    |

| t <sub>PLH</sub> | Propagation Delay Time<br>LOW-to-HIGH Level Output | Clear to $\overline{Q}$      |                        | 25  |                        | 35  | ns    |

| t <sub>PHL</sub> | Propagation Delay Time<br>HIGH-to-LOW Level Output | Clear to Q                   |                        | 30  |                        | 35  | ns    |

www.fairchildsemi.com

www.fairchildsemi.com