transforming specialty electronics

## **512K x 8 SRAM**

# 3.3 VOLT HIGH SPEED SRAM with **CENTER POWER PINOUT**

## **AVAILABLE AS MILITARY SPECIFICATIONS**

- •MIL-STD-883 for Ceramic

- •Extended Temperature Plastic (COTS)

### **FEATURES**

**OPTIONS**

- Ultra High Speed Asynchronous Operation

- Fully Static, No Clocks

- · Multiple center power and ground pins for improved noise immunity

- Easy memory expansion with CE\ and OE\

- · All inputs and outputs are TTL-compatible

- Single +3.3V Power Supply +/- 0.3V

- Data Retention Functionality Testing

- · Cost Efficient Plastic Packaging

• 2V data retention/low power\*

- Extended Testing Over -55°C to +125°C for plastics

- RoHS Compliant Options Available

| • | Timing                       |       |         |

|---|------------------------------|-------|---------|

|   | 10ns access                  | -10   |         |

|   | 12ns access                  | -12   |         |

|   | 15ns access                  | -15   |         |

|   | 20ns access                  | -20   |         |

|   | 25ns access                  | -25   |         |

|   |                              |       |         |

| • | Operating Temperature Ranges |       |         |

|   | 883C (-55°C to +125°C)       | /883C |         |

|   | Military (-55°C to +125°C)   | /XT   |         |

|   | Industrial (-40°C to +85°C)  | /IT   |         |

|   | Poskoga(s)                   |       |         |

| • | Package(s)                   | Б     | NI 207  |

|   | Ceramic Flatpack             | F     | No. 307 |

|   | Ceramic LCC                  | EC    | No. 210 |

|   | Plastic SOJ (400 mils wide)  | DJ    |         |

|   |                              |       |         |

**MARKING**

For more products and information please visit our web site at www.micross.com

L

#### PIN ASSIGNMENT (Top View) 36-Pin PSOJ (DJ) 36-Pin CLCC (EC) 36 T NC 35 A18 A1 [ 34 A17 A2 [ АЗ П 33 A16 A4 [ 32 T A15 31 OE CE [ 30 1/07 1/00 F 29 7 1/06 1/01 E 28 GND Vcc [ (/O2 [ 27 Voc 26 7 1/05 VO3 ☐ 12 WE ☐ 13 25 1/04 24 A14 23 A13 AS [ 22 A12 A6 [] A7 [ 21 A11 20 A10 A8 [] 19 NC 36-Pin Flat Pack (F) 35 A18 34 A17 A2 3 [ 33 A16 A3 4 [ A4 5 [ 7 31 DE∖ CE/ 6 [ 30 1/07 1/00 7 7 29 1/06 1/01 8 🗆 VCC 9 [ 28 VSS VSS 10 27 VCC 1/02 11 26 1/05 1/03 12 25 1/04 WE\ 13 24 A14 \_ 7 23 A13 A5 14 22 A12 A6 15 [ A7 16 21 A11 \_\_\_\_\_\_20 A10 19 NC

transforming specialty electronics

### GENERAL DESCRIPTION

The AS5LC512K8 is a 3.3V high speed SRAM. It offers flexibility in high-speed memory applications, with chip enable (CE\) and output enable (OE\) capabilities. These features can place the outputs in High-Z for additional flexibility in system design.

Writing to these devices is accomplished when write enable (WE\) and CE\ inputs are both LOW. Reading is accomplished when WE\ remains HIGH and CE\ and OE\ go LOW.

As a option, the device can be supplied offering a reduced power standby mode, allowing system designers to meet low standby power requirements. This device operates from a single +3.3V power supply and all inputs and outputs are fully TTL-compatible.

The AS5LC512K8DJ offers the convenience and reliability of the AS5LC512K8 SRAM and has the cost advantage of a plastic encapsulation. TSOPII with copper lead frames offers superior thermal performance.

## **FUNCTIONAL BLOCK DIAGRAM**

<sup>\*</sup>On the low voltage Data Retention option.

#### TRUTH TABLE

| MODE         | OE\ | CE\ | WE\ | I/O    | POWER   |

|--------------|-----|-----|-----|--------|---------|

| STANDBY      | Χ   | Н   | Χ   | HIGH-Z | STANDBY |

| READ         | L   | L   | Η   | Q      | ACTIVE  |

| NOT SELECTED | Н   | L   | Н   | HIGH-Z | ACTIVE  |

| WRITE        | Χ   | Ĺ   | Ĺ   | D      | ACTIVE  |

X = Don't Care

#### PIN FUNCTIONS

| A0 - A18                            | Address Inputs      |

|-------------------------------------|---------------------|

| WE\                                 | Write Enable        |

| CE\                                 | Chip Enable         |

| OE\                                 | Output Enable       |

| I/O <sub>0</sub> - I/O <sub>7</sub> | Data Inputs/Outputs |

| V <sub>cc</sub>                     | Power               |

| V <sub>SS</sub>                     | Ground              |

| NC                                  | No Connection       |

transforming specialty electronics

### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on Vcc Supply Relative to Vss  |                |

|----------------------------------------|----------------|

| Vcc                                    | 5V to 4.0V     |

| Storage Temperature                    | 65°C to +150°C |

| Short Circuit Output Current (per I/O) | 20mA           |

| Voltage on any Pin Relative to Vss     | 5V to 4.6V     |

| Maximum Junction Temperature**         | +150°C         |

| Power Dissipation                      | 1W             |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This v is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **ELECTRICAL CHARACTERISTICS AND RECOMMENDED DC OPERATING CONDITIONS**

$(-55^{\circ}C \le T_{_A} \le +125^{\circ}C \& -40^{\circ}C \le T_{_A} \le +85^{\circ}C ; Vcc = 3.3V \pm 0.3\%)$

|                                    |                                                                                          |                                             |                    |     |     | MAX |     |     |       |       |

|------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------|--------------------|-----|-----|-----|-----|-----|-------|-------|

| DESCRIPTION                        | COND                                                                                     | ITIONS                                      | SYM                | -10 | -12 | -15 | -20 | -25 | UNITS | NOTES |

| Power Supply<br>Current: Operating | 110                                                                                      |                                             | I <sub>CCSP</sub>  | 90  | 80  | 70  | 60  | 55  | mA    | 3, 2  |

|                                    |                                                                                          | "L" Version Only                            | I <sub>CCLP</sub>  | 1   | 60  | 50  | 40  | 35  | mA    |       |

|                                    | $CE \ge V_{IH}$ , All other inputs $\le V_{IL}$ , $Vcc = MAX$ , $f = 0$ , $Outputs Open$ |                                             | I <sub>SBTSP</sub> | 30  | 20  | 20  | 20  | 20  | mA    |       |

| Power Supply                       |                                                                                          | "L" Version Only                            | I <sub>SBTLP</sub> | 1   | 15  | 15  | 15  | 15  | mA    |       |

| Current: Standby                   | V <sub>IN</sub> ≤Vss                                                                     | 2V; Vcc = MAX<br>s +0.2V or<br>-0.2V; f = 0 | I <sub>SBCSP</sub> | 20  | 15  | 15  | 15  | 15  | mA    |       |

|                                    |                                                                                          | "L" Version Only                            | I <sub>SBCLP</sub> | -   | 9   | 9   | 9   | 9   | mA    | 1     |

| DESCRIPTION                  | CONDITIONS                                     | SYM             | MIN  | MAX      | UNITS | NOTES |

|------------------------------|------------------------------------------------|-----------------|------|----------|-------|-------|

| Input High (Logic 1) Voltage |                                                | $V_{IH}$        | 2.2  | Vcc +0.3 | V     | 1     |

| Input Low (Logic 0) Voltage  |                                                | $V_{IL}$        | -0.3 | 8.0      | >     | 1     |

| Input Leakage Current        | $0V \le V_{IN} \le Vcc$                        | ILI             | -2   | 2        | μΑ    |       |

| Output Leakage Current       | Output(s) Disabled $0V \le V_{OUT} \le V_{CC}$ | I <sub>LO</sub> | -2   | 2        | μΑ    |       |

| Output High Voltage          | I <sub>OH</sub> = <b>-4</b> .0 mA              | $V_{OH}$        | 2.4  |          | >     | 1     |

| Output Low Voltage           | I <sub>OL</sub> = 8 mA                         | $V_{OL}$        |      | 0.5      | ٧     | 1     |

### **CAPACITANCE**

| PARAMETER          | CONDITIONS                      | SYMBOL | MAX | UNITS | NOTES |

|--------------------|---------------------------------|--------|-----|-------|-------|

| Input Capacitance  | T <sub>A</sub> = 25°C, f = 1MHz | Cı     | 8   | pF    | 4     |

| Output Capactiance | $V_{IN} = 0$                    | Со     | 6   | pF    | 4     |

<sup>\*\*</sup> Junction temperature depends upon package type, cycle time, loading, ambient temperature and airflow, and humidity.

## **ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS**

$(-55^{\circ}C \le T_A \le +125^{\circ}C \text{ or } -40^{\circ}C \text{ to } +85^{\circ}C; \text{ Vcc} = 3.3 \text{V} \pm 0.3\%)$

| DESCRIPTION                        | SYM               |     | 10  | -1  | 12  | -1  | 15  | -2  | 20  | -2  | 25  | LIMITS | NOTES   |

|------------------------------------|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|--------|---------|

|                                    |                   | MIN | MAX | UNITS  | NOTES   |

| READ CYCLE                         |                   |     |     |     |     |     |     |     |     |     |     |        |         |

| Read Cycle Time                    | t <sub>RC</sub>   | 10  |     | 12  |     | 15  |     | 20  |     | 25  |     | ns     |         |

| Address Access Time                | t <sub>AA</sub>   |     | 10  |     | 12  |     | 15  |     | 20  |     | 25  | ns     |         |

| Chip Enable Access Time            | t <sub>ACE</sub>  |     | 10  |     | 12  |     | 15  |     | 20  |     | 25  | ns     |         |

| Output Hold From Address Change    | t <sub>OH</sub>   | 2   |     | 2   |     | 2   |     | 2   |     | 2   |     | ns     |         |

| Chip Enable to Output in Low-Z     | t <sub>LZCE</sub> | 2   |     | 2   |     | 2   |     | 2   |     | 2   |     | ns     | 4, 6, 7 |

| Chip Disable to Output in High-Z   | t <sub>HZCE</sub> |     | 4   |     | 6   |     | 7   |     | 8   |     | 9   | ns     | 4, 6, 7 |

| Output Enable Acess Time           | t <sub>AOE</sub>  |     | 4.5 |     | 6   |     | 7   |     | 8   |     | 9   | ns     |         |

| Output Enable to Output in Low-Z   | t <sub>LZOE</sub> | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | ns     | 4, 6, 7 |

| Output Disable to Output in High-Z | t <sub>HZOE</sub> |     | 4   |     | 6   |     | 7   |     | 8   |     | 9   | ns     | 4, 6, 7 |

| WRITE CYCLE                        |                   |     |     |     | •   |     |     |     |     |     |     |        |         |

| WRITE Cycle Time                   | t <sub>WC</sub>   | 10  |     | 12  |     | 15  |     | 20  |     | 25  |     | ns     |         |

| Chip Enable to End of Write        | t <sub>CW</sub>   | 8   |     | 8   |     | 10  |     | 12  |     | 13  |     | ns     |         |

| Address Valid to End of Write      | t <sub>AW</sub>   | 8   |     | 8   |     | 10  |     | 12  |     | 13  |     | ns     |         |

| Address Setup Time                 | t <sub>AS</sub>   | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | ns     |         |

| Address Hold From End of Write     | t <sub>AH</sub>   | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | ns     |         |

| WRITE Pulse Width                  | t <sub>WP</sub>   | 8   |     | 10  |     | 12  |     | 15  |     | 15  |     | ns     |         |

| Data Setup Time                    | t <sub>DS</sub>   | 6   |     | 6   |     | 7   |     | 8   |     | 8   |     | ns     |         |

| Data Hold Time                     | t <sub>DH</sub>   | 1   |     | 1   |     | 1   |     | 1   |     | 1   |     | ns     |         |

| Write Disable to Output in Low-Z   | t <sub>LZWE</sub> | 2   |     | 2   |     | 2   |     | 2   |     | 2   |     | ns     | 4, 6, 7 |

| Write Enable to Output in High-Z   | t <sub>HZWE</sub> |     | 5   |     | 5   |     | 6   |     | 7   |     | 7   | ns     | 4, 6, 7 |

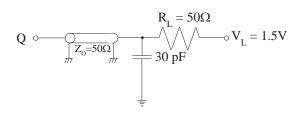

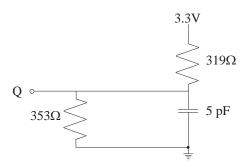

### **AC TEST CONDITIONS**

| Input pulse levels            | Vss to 3.0V         |

|-------------------------------|---------------------|

| Input rise and fall times     | 3ns                 |

| Input timing reference levels | 1.5V                |

| Output reference levels       | 1 5Vl               |

| Output load                   | See Figures 1 and 2 |

| _                             | - 1                 |

Fig. 1 Output Load Equivalent

Fig. 2 Output Load Equivalent

### **NOTES**

- All voltages referenced to  $V_{ss}$  (GND).

- I<sub>cc</sub> limit shown is for absolute worst case switching of ADDR, ADDR\, ADDR, etc.

- I<sub>cc</sub> is dependent on output loading and cycle rates.

- This parameter is guaranteed but not tested.

- Test conditions as specified with the output loading as shown in Fig. 1 unless otherwise noted.

- 6. LZCE, LZWE, LZOE, HZCE, HZOE and HZWE are specified with CL = 5pF as in Fig. 2. Transition is measured ±200mV from steady state voltage.

- 7. At any given temperature and voltage condition, 'HZCE is less than 'LZCE, and 'HZWE is less than tLZWE.

- 8. WE\ is HIGH for READ cycle.

- Device is continuously selected. Chip enables and output enables are held in their active state.

- 10. Address valid prior to, or coincident with, latest occurring chip enable.

- 11. 'RC = Read Cycle Time.

- 12. Chip enable and write enable can initiate and terminate a WRITE cycle.

- 13. Output enable (OE\) is inactive (HIGH).

- 14. Output enable (OE\) is active (LOW).

- 15. ASI does not warrant functionality nor reliability of any product in which the junction temperature exceeds 150°C. Care should be taken to limit power to acceptable levels.

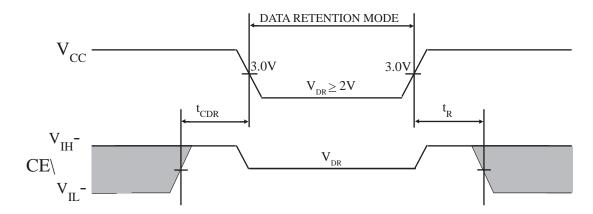

## DATA RETENTION ELECTRICAL CHARACTERISTICS (L Version Only)

| DESCRIPTION             | CONDITIO                                             | SYM                    | MIN               | MAX | UNITS | NOTES |       |

|-------------------------|------------------------------------------------------|------------------------|-------------------|-----|-------|-------|-------|

|                         | CE\ > $V_{CC}$ -0.2V<br>$V_{IN} > V_{CC}$ -0.2 or 0. | $V_{DR}$               | 2                 |     | ٧     |       |       |

|                         | VIN > VCC -0.2 01 0.                                 | /IN > VCC -U.2 OF U.2V |                   |     |       |       |       |

| Data Retention Current  |                                                      | Vcc = 2.0V             | I <sub>CCDR</sub> |     | 6.5   | mA    |       |

| Chip Deselect to Data   |                                                      |                        | t <sub>CDR</sub>  | 0   |       | ns    | 4     |

| Operation Recovery Time |                                                      |                        | t <sub>R</sub>    | 20  |       | ms    | 4, 11 |

# LOW $V_{cc}$ DATA RETENTION WAVEFORM

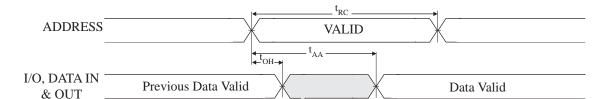

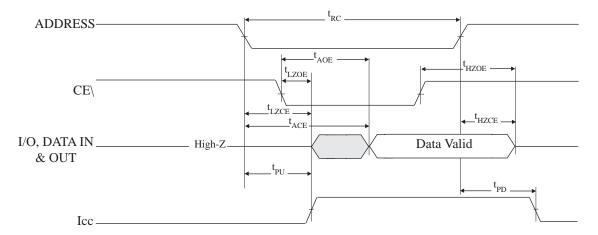

## READ CYCLE NO. 11,2

(Address Controlled,  $CE = OE = V_{II}$ ,  $WE = V_{IH}$ )

## **READ CYCLE NO. 2**

$$(WE \setminus = V_{IH})$$

#### NOTES:

- 1. WE\ is HIGH for READ cycle.

- 2. Device is continuously selected. Chip enables and output enables are held in their active state.

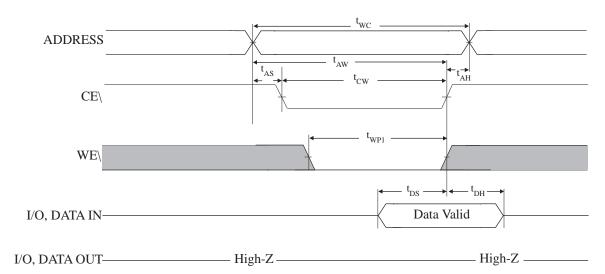

# WRITE CYCLE NO. 11

(CE Controlled)

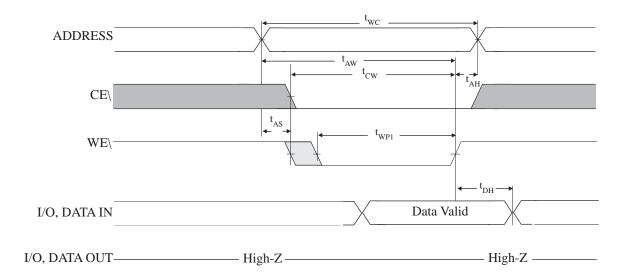

# WRITE CYCLE NO. 2<sup>1, 2</sup>

(Write Enabled Controlled)

### **NOTES:**

- 1. Chip enable and write enable can initiate and terminate a WRITE cycle.

- Output enable (OE\) is inactive (HIGH).

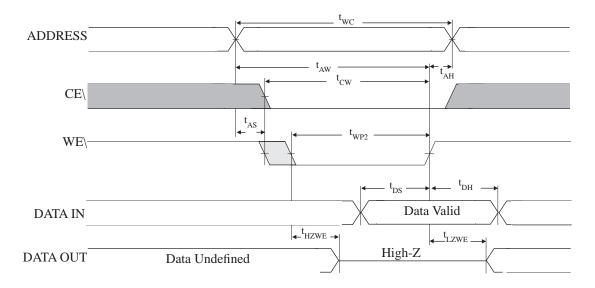

# WRITE CYCLE NO. 31, 2, 3

(WE Controlled)

#### **NOTES:**

- 1. At any given temperature and voltage condition,  $t_{HZCE}$  is less than  $t_{LZCE}$ , and  $t_{HZWE}$  is less than  $t_{LZWE}$ .

2. Chip enable and write enable can initiate and terminate a WRITE cycle.

- 3. Output enable (OE\) is active (LOW).

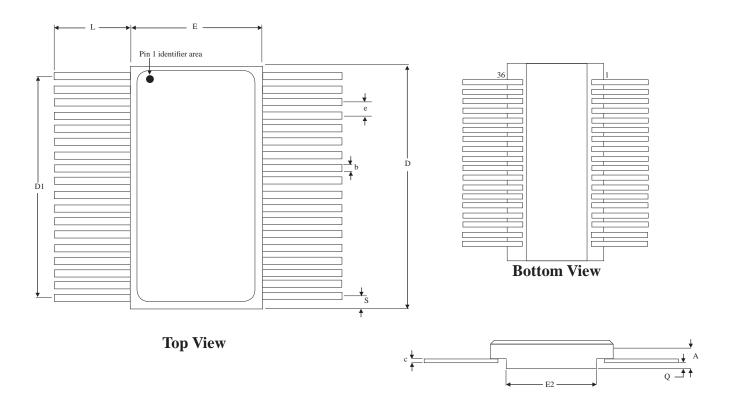

# **MECHANICAL DEFINITIONS\***

Micross Case #307 (Package Designator F)

|        | MICROSS SPECIFICATIONS |       |  |  |  |  |  |  |

|--------|------------------------|-------|--|--|--|--|--|--|

| SYMBOL | MIN                    | MAX   |  |  |  |  |  |  |

| Α      | 0.096                  | 0.125 |  |  |  |  |  |  |

| b      | 0.015                  | 0.022 |  |  |  |  |  |  |

| С      | 0.003                  | 0.009 |  |  |  |  |  |  |

| D      | 0.910                  | 0.930 |  |  |  |  |  |  |

| D1     | 0.840                  | 0.860 |  |  |  |  |  |  |

| E      | 0.505                  | 0.515 |  |  |  |  |  |  |

| E2     | 0.385                  | 0.397 |  |  |  |  |  |  |

| е      | 0.050                  | ) BSC |  |  |  |  |  |  |

| L      | 0.250                  | 0.370 |  |  |  |  |  |  |

| Q      | 0.020                  | 0.045 |  |  |  |  |  |  |

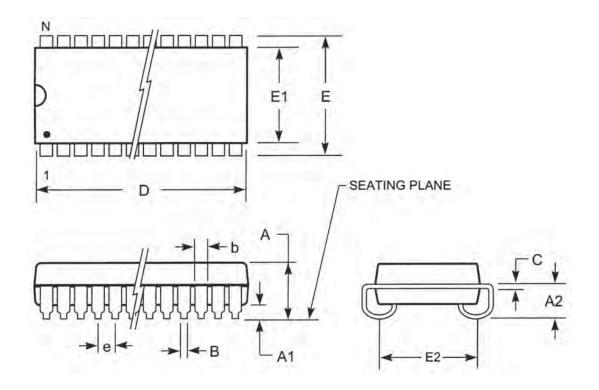

# **MECHANICAL DEFINITIONS\***

# Package Designator DJ

|        | MICROSS SPECIFICATIONS |       |  |  |  |  |  |  |

|--------|------------------------|-------|--|--|--|--|--|--|

| SYMBOL | MIN                    | MAX   |  |  |  |  |  |  |

| Α      | 0.128                  | 0.148 |  |  |  |  |  |  |

| A1     | 0.025                  |       |  |  |  |  |  |  |

| A2     | 0.082                  |       |  |  |  |  |  |  |

| В      | 0.015                  | 0.020 |  |  |  |  |  |  |

| b      | 0.026                  | 0.032 |  |  |  |  |  |  |

| С      | 0.007                  | 0.013 |  |  |  |  |  |  |

| D      | 0.920                  | 0.930 |  |  |  |  |  |  |

| E      | 0.435                  | 0.445 |  |  |  |  |  |  |

| E1     | 0.395                  | 0.405 |  |  |  |  |  |  |

| E2     | 0.370 BSC              |       |  |  |  |  |  |  |

| е      | 0.050 BSC              |       |  |  |  |  |  |  |

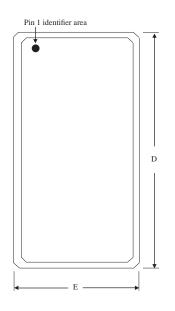

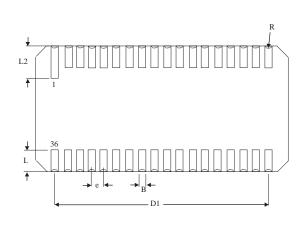

# **MECHANICAL DEFINITIONS\***

# Micross Case #210 (Package Designator EC)

|        | MICROSS SPECIFICATIONS |       |  |

|--------|------------------------|-------|--|

| SYMBOL | MIN                    | MAX   |  |

| Α      | 0.080                  | 0.100 |  |

| A1     | 0.054                  | 0.066 |  |

| В      | 0.022                  | 0.028 |  |

| D      | 0.910                  | 0.930 |  |

| D1     | 0.840                  | 0.860 |  |

| E      | 0.445                  | 0.460 |  |

| е      | 0.050 BSC              |       |  |

| L      | 0.100 TYP              |       |  |

| L2     | 0.115                  | 0.135 |  |

| Р      |                        | 0.006 |  |

| R      | 0.009 TYP              |       |  |

## ORDERING INFORMATION

### **36-Pin Ceramic Flat Pack**

**EXAMPLE:** AS5LC512K8F-12L/XT

| Device Number | Package<br>Type | Speed<br>ns | Options** | Process |

|---------------|-----------------|-------------|-----------|---------|

| AS5LC512K8    | F               | -10         | L         | /*      |

| AS5LC512K8    | F               | -12         | L         | /*      |

| AS5LC512K8    | F               | -15         | L         | /*      |

| AS5LC512K8    | F               | -25         | L         | /*      |

#### 36-Pin Plastic PSOJ

**EXAMPLE:** AS5LC512K8DJ-20L/IT

| Device Number | Package<br>Type | Speed<br>ns | Options** | Process |

|---------------|-----------------|-------------|-----------|---------|

| AS5LC512K8    | DJ              | -12         | L         | /*      |

| AS5LC512K8    | DJ              | -15         | L         | /*      |

| AS5LC512K8    | DJ              | -20         | L         | /*      |

| AS5LC512K8    | DJ              | -25         | L         | /*      |

### 36-Pin Ceramic CLCC

**EXAMPLE:** AS5LC512K8EC-15L/IT

| Device Number | Package<br>Type | Speed<br>ns | Options** | Process |

|---------------|-----------------|-------------|-----------|---------|

| AS5LC512K8    | EC              | -12         | L         | /*      |

| AS5LC512K8    | EC              | -15         | L         | /*      |

| AS5LC512K8    | EC              | -20         | L         | /*      |

| AS5LC512K8    | EC              | -25         | L         | /*      |

## \*AVAILABLE PROCESSES

$IT = Industrial \ Temperature \ Range \\ XT = Extended \ Temperature \ Range \\ 883C = Full \ Military \ Processing^1 \\ -55^{\circ}C \ to +125^{\circ}C \\ -$

### \*\*OPTIONS DEFINITIONS

L = 2V Data Retention / Low Power

**NOTES:** 1. 883C process available with ceramic packaging only.

## **DOCUMENT TITLE**

512K x 8 SRAM 3.3 VOLT HIGH SPEED SRAM with CENTER POWER PINOUT

| <u>Rev #</u><br>2.1 | History Pg 1: Changed 0.3% to 0.3V                                                                                                                                                                                                                                | Release Date<br>August 2009 | <u>Status</u><br>Release |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------|

| 2.2                 | Updated Micross Information                                                                                                                                                                                                                                       | January 2010                | Release                  |

| 2.3                 | Expanded package offering to include Copper Lead Frames and RoHS Compliancy, added -10 speed option, Reduced $C_L$ from 9pF to 8pF, corrected $t_{HZWE}$ from min's to max's on page 4, corrected 4.5V reference points on data retention waveform to 3.0V, pg. 6 | March 2011                  | Release                  |

| 2.4                 | Removed Cu-lead frame option                                                                                                                                                                                                                                      | October 2013                | Release                  |