# Dual 3A MOSFET Driver With Adaptive LEB

#### **FEATURES**

- Built using BCDMOS Process

- High Peak Output Current (3A)

- · Self Biasing Active Off Outputs

- Pinout Compatible with Industry Standard Drivers

- Patent Pending Adaptive Leading Edge Blanking (LEB)

- Undervoltage Lockout (UVLO)

- High Capacitive Load Drive Capability

- CMOS Compatible Input Threshold

- Wide Operating Voltage Range from 4.5V to 18V

- Shutdown Capability via Logic Level Input ENBL

#### **DESCRIPTION**

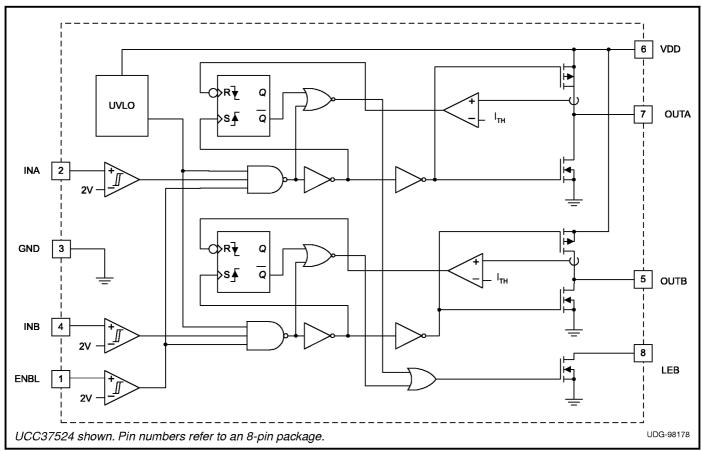

The UCC37523/37524/37525 devices are high speed, dual MOSFET drivers using the BiCMOS/DMOS process. All three devices are designed to be pin and performance compatible with industry standard '423, '424, '425, '426A, '427A, and '428A drivers. Each of the dual outputs is capable of providing 3A peak current and 6A in parallel. In addition, the devices feature Undervoltage Lockout (UVLO) protection, an improved input noise immunity and an enable/shutdown input. The ENBL function is implemented on one of the unused pins from the industry standard pinout. An adaptive leading edge blanking (LEB) signal is provided on the other unused pin.

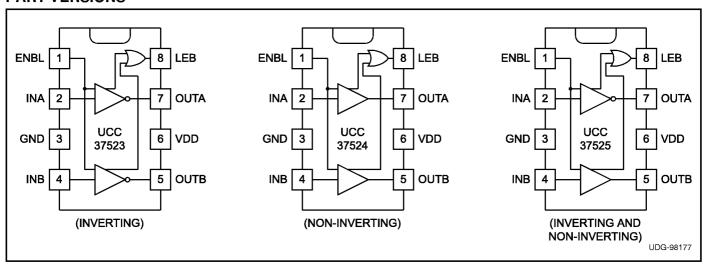

The UCC37523 is a dual inverting driver. The UCC37524 is a dual non-inverting driver. The UCC37525 contains one inverting and one non-inverting driver.

In addition to driving two power MOSFETs in high power and high frequency switch mode power supply and motion control applications, these drivers are also capable of driving capacitive and inductive loads in applications such as small motor, relay, solenoid and actuator drivers. Unlike Bipolar Gate Driver ICs, these BCDMOS drivers do not require external Schottky clamp diodes for slight negative voltage overshoot protection.

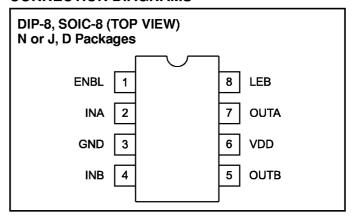

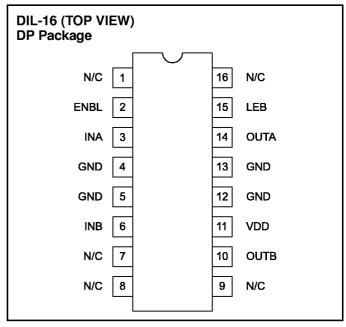

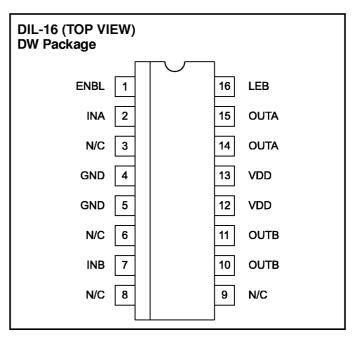

UCC37523/37524/37525 family of drivers are available in 8 pin SOIC (D), PDIP (N) or CDIP (J), 16 pin SOIC-Wide (DW) or 16 pin SOIC-Power (DP) packages.

## **BLOCK DIAGRAM**

# **ABSOLUTE MAXIMUM RATINGS**

Unless otherwise indicated, voltages are referenced to GND pin and currents are positive into, negative out of, the specified terminals. Consult Packaging Section of Databook for thermal limitations and considerations of the packages.

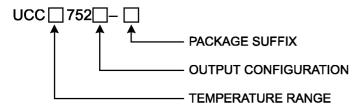

#### ORDERING INFORMATION

|          | Temperature Range | Package Suffix |

|----------|-------------------|----------------|

| UCC1752X | −55°C to +125°C   | J              |

| UCC2752X | -40°C to +85°C    | D, DP, DW, N   |

| UCC3752X | 0°C to +70°C      | D, DP, DW, N   |

## **PACKAGE THERMAL RESISTANCE**

| Package           | Suffix | Theta (jc) | Theta (ja) |

|-------------------|--------|------------|------------|

| 8 pin SOIC        | D      | 42°C/W     | 84-160°C/W |

| 8 pin plastic DIP | N      | 49         | 110        |

| 16 pin Power SOIC | DP     | 20         | 36-58      |

| 16 pin SOIC-wide  | DW     | 27         | 50-100     |

| 8 pin ceramic DIP | J      | 26         | 160        |

#### **CONNECTION DIAGRAMS**

# **INPUT/OUTPUT TABLE**

| Inp    | uts (V <sub>IN_L</sub> , V <sub>IN</sub> | і_н)   | UCC  | UCC37523 UCC37524 |      | UCC  | 37525 |      |

|--------|------------------------------------------|--------|------|-------------------|------|------|-------|------|

| ENBL   | INA                                      | INB    | OUTA | OUTB              | OUTA | OUTB | OUTA  | OUTB |

| < 1.6V | < 1.6V                                   | < 1.6V | VOH  | VOH               | VOL  | VOL  | VOH   | VOL  |

| < 1.6V | < 1.6V                                   | > 2.4V | VOH  | VOH               | VOL  | VOL  | VOH   | VOL  |

| < 1.6V | > 2.4V                                   | < 1.6V | VOH  | VOH               | VOL  | VOL  | VOH   | VOL  |

| < 1.6V | > 2.4V                                   | > 2.4V | VOH  | VOH               | VOL  | VOL  | VOH   | VOL  |

| > 2.4V | > 1.6V                                   | < 1.6V | VOH  | VOH               | VOL  | VOL  | VOH   | VOL  |

| > 2.4V | > 1.6V                                   | > 2.4V | VOH  | VOL               | VOL  | VOH  | VOH   | VOH  |

| > 2.4V | < 2.4V                                   | < 1.6V | VOL  | VOH               | VOH  | VOL  | VOL   | VOL  |

| > 2.4V | < 2.4V                                   | > 2.4V | VOL  | VOL               | VOH  | VOH  | VOL   | VOH  |

# **PART VERSIONS**

# **ELECTRICAL CHARACTERISTICS**: Unless otherwise specified, the MIN and MAX specifications apply for $4.5 \text{VDD} \le 18 \text{V}$ , $T_J = T_A$ . Unless otherwise specified, the TYP specifications apply for VDD = 12V, $T_A = 25 \,^{\circ}\text{C}$ , $T_J = T_A$ .

| PARAMETER                                                       | TEST CONDITIONS             | MIN   | TYP   | MAX   | UNITS |

|-----------------------------------------------------------------|-----------------------------|-------|-------|-------|-------|

| Input Section                                                   |                             | •     |       | •     |       |

| V <sub>IN_H</sub> , Logic 1 Input Threshold<br>(INA, INB, ENBL) |                             | 2.4   |       |       | V     |

| V <sub>IN_L</sub> , Logic 0 Input Threshold (INA, INB, ENBL)    |                             |       |       | 1.6   | V     |

| Input current (INA, INB)                                        | $0V \le V(IN[AB]) \le VDD$  | -10   | 0     | 10    | μΑ    |

| Input current (ENBL)                                            | V (ENBL) = 0                | -50   | -10   | 10    | μΑ    |

|                                                                 | V (ENBL) = VDD              | -10   | 0     | 10    | μΑ    |

| Output Section                                                  |                             |       |       |       |       |

| V <sub>OH</sub> , Output OUTA, OUTB High Level                  | $V_{OH} = V_{DD} - V_{OUT}$ |       | 0.001 | 0.025 | V     |

| V <sub>OL</sub> , Output OUTA, OUTB Low Level                   |                             |       | 0.001 | 0.025 | V     |

| Output Resistance High                                          | I(OUT)=10mA, VDD = 18V      |       | 1.2   | 8     | Ω     |

| Output Resistance Low                                           | I(OUT)=10mA, VDD = 18V      |       | 3.5   | 8     | Ω     |

| Peak Output Current                                             | (Note 1)                    |       | 3     |       | Α     |

| Latch-up Protection                                             | (Note 1)                    | > 500 |       |       | mA    |

**ELECTRICAL CHARACTERISTICS**: Unless otherwise specified, the MIN and MAX specifications apply for  $4.5V \le VDD \le 18V$ ,  $T_J = T_A$ . Unless otherwise specified, the TYP specifications apply for VDD = 12V,  $T_A = 25$  °C,  $T_J = T_A$ .

| PARAMETER                                           | TEST CONDITIONS                            | MIN | TYP | MAX | UNITS |

|-----------------------------------------------------|--------------------------------------------|-----|-----|-----|-------|

| Switching Time Section                              |                                            |     |     |     |       |

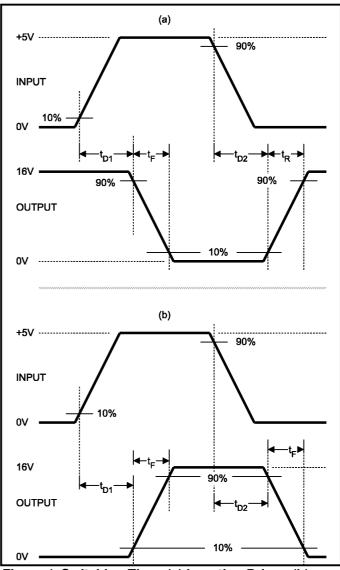

| t <sub>R</sub> , OUTA,OUTB Rise Time                | C <sub>LOAD</sub> = 1800 pF (See Figure 1) |     | 20  | 60  | ns    |

| t <sub>F</sub> , OUTA,OUTB Fall Time                | C <sub>LOAD</sub> = 1800 pF (See Figure 1) |     | 25  | 60  | ns    |

| t <sub>D1</sub> , Delay (IN[AB] to OUT[AB]) Rising  | C <sub>LOAD</sub> = 1800 pF (See Figure 1) |     | 50  | 100 | ns    |

| t <sub>D2</sub> , Delay (IN[AB] to OUT[AB]) Falling | C <sub>LOAD</sub> = 1800 pF (See Figure 1) |     | 50  | 100 | ns    |

| Undervoltage Lockout Section                        |                                            |     |     |     |       |

| Start Threshold                                     |                                            | 4.2 | 4.3 | 4.5 | V     |

| Start to Stop Hysteresis                            |                                            | 0.4 | 0.6 | 0.9 | V     |

| Leading Edge Blanking Section                       |                                            |     |     |     |       |

| Output LEB Low Level                                | I(LEB) = 1.25mA                            |     | 0.1 | 0.2 | V     |

| Power Supply Section                                |                                            |     |     |     |       |

| Operating Current                                   | Static, Inputs = 0V                        |     | 3.5 | 5   | mA    |

Note 1: Guaranteed by design. Not 100% tested in production.

#### PIN DESCRIPTIONS

ENBL: Enable input with logic compatible threshold and hysteresis. Both driver outputs can be enabled/disabled with this input. The ENBL function is active high. That is, when ENBL is low, the IC will be disabled. When ENBL is high, the IC is enabled. The ENBL pin has an active pull- up such that the default state for the pin is to enable the IC. The output states when the IC is disabled will be the same as if the inputs was low during normal operation. For example, outputs of UCC37523 (inverting) will be held high, outputs of UCC37524 (non-inverting) will be held low and outputs of UCC37525 (inverting + non-inverting) will be held high and low respectively for OUTA and OUTB. Under this mode, the inverting outputs on UCC37523 and OUTA of UCC37525 will track VDD.

**GND:** Common ground. This ground should be connected very closely to the source of the power MOSFET which the driver is driving.

**INA:** Input A. Input signal for the A driver, logic compatible threshold and hysteresis.

**INB:** Input B. Input signal for the B driver, logic compatible threshold and hysteresis.

**LEB:** Leading Edge Blanking output. This pin should be connected to the current sense node of the power converter. During the leading edge blanking period, a pull-down device will connect the node to ground, "blanking" any leading edge noise spikes. This pin is the logical OR of the LEB sensing circuits on both drivers OUTA and OUTB.

**OUTA:** Driver output A. This complementary MOS output swings to both VDD and GND.

**OUTB:** Driver output B. This complementary MOS output swings to both VDD and GND.

**VDD:** Supply voltage. This is the supply voltage for the IC. Good bypassing is required between VDD and GND.

#### APPLICATION INFORMATION

#### **Supply Section**

The IC operates over a wide supply range, from 4.5V to 18V.

#### **Input Section**

The input circuit contains hysteresis to maximize noise immunity. The inputs are designed such that they can swing up to 5V below GND without damage to the IC.

## **Output Section**

The output circuit is designed to drive a MOSFET gate on and off in 25nsec typically. The output will supply a high peak output current (3A peak). The output of the driver uses complementary devices and will swing the gate fully between the two supply rails. The outputs are designed to withstand 500mA reverse current without either damage or logic upset. The outputs are actively pulled down during undervoltage lockout even in the absence of VDD power.

Inverting outputs of UCC37523 and OUTA of UCC37525 are intended to drive external P-channel MOSFETs. Non-inverting outputs of UCC37524 and OUTB of UCC37525 are intended to drive N-channel MOSFETs.

# **Undervoltage Lockout Section**

The under voltage detection circuit prevents the outputs from turning on the external power MOSFET when VDD is below a preset value.

When the IC is in an Undervoltage mode, the output states will be the same as if the input was low during normal operation. For example, outputs of UCC37523 (inverting) will be held high, outputs of UCC37524 (non-inverting) will be held low and outputs of UCC37525 (inverting + non-inverting) will be held high and low respectively for OUTA and OUTB. Under this mode, the inverting outputs on UCC37523 and OUTA of UCC37525 will track VDD.

## **Leading Edge Blanking Section**

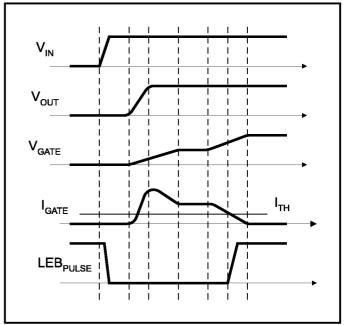

The UCC37523/37524/37525 features a Patent Pending Adaptive Leading Edge Blanking circuit. An open drain FET output at the LEB pin is used to shunt the current sense signal of the PWM to ground, thus providing leading edge blanking. When the driver is turned on, an internal NMOS switch is turned on whose drain is brought out to the LEB pin. This should be connected to the current sense input of the current mode control IC. After the power MOS gate is charged, the LEB is removed by turning off this NMOS device.

#### **Adaptive Leading Edge Blanking Principle**

During a power MOSFET turn-on process, the leading edge current sense signal from the output will have an undesirable noise spike falsely triggering the overcurrent protection circuit due to the internal gate impedance. The traditional implementation of Leading Edge Blanking (LEB) in a power control application is to blank the output signal for a fixed amount of time either by an external component or provided by the PWM controller. However, the interval width of the unwanted leading edge noise changes with gate resistance, load current, temperature, diode speed and MOSFET size and technology that is being used. With UCC37523/4/5 family of drivers, the leading edge blanking pulse width is varied as needed with the changing conditions.

Figure 1. Switching Time (a) Inverting Driver (b) Non-Inverting Driver

# **APPLICATION INFORMATION (cont.)**

Adaptive blanking in these drivers is accomplished by monitoring both the input signal and charge current from the driver IC to MOSFET gate. The leading edge current spike only occurs while the power MOSFET is being switched ON or OFF. This is also the time when gate charge current is also flowing. As shown in Fig. 2., the LEB signal is initiated on a rising edge of the input signal ( $V_{IN}$ ). The LEB control circuit monitors the gate charge current and releases the blanking signal when the gate current falls below the predefined threshold level. ( $I_{TH}$ )

The advantages of this adaptive approach are many. This method does not depend on inaccurate timing circuits, eliminates the need of filter capacitor on the current sense inputs of PWM controllers (the series resistor is still needed), provides a minimum blanking interval to support higher frequency designs, allows for effective short circuit protection, and is fully adaptive to varying component and operating conditions.

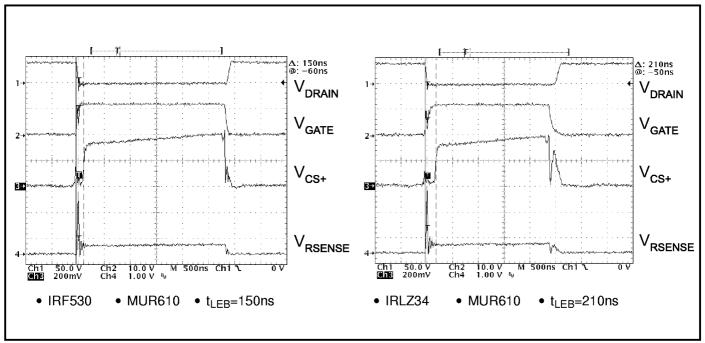

Fig.3. shows two operating waveforms using the UCC37523/4/5 family of drivers with different MOSFET component selection.  $V_{RSENSE}$  is the unfiltered current sense signal and VCS+ is current sense signal with LEB. As can be seen, the LEB pulse width measurements accommodates the changing operating conditions.

Figure 2. Leading Edge Blanking Principle

Figure 3. Operating Waveforms (f<sub>S</sub>=135kHz)

# 8-PIN PLASTIC DIP ~ N PACKAGE SUFFIX

|    | DIMENSIONS |        |      |             |   |  |  |

|----|------------|--------|------|-------------|---|--|--|

|    | INC        | INCHES |      | MILLIMETERS |   |  |  |

|    | MIN        | MAX    | MIN  | MAX         |   |  |  |

| Α  | .245       | .260   | 6.22 | 6.60        | 1 |  |  |

| В  | .320       | .400   | 9.40 | 10.16       | 1 |  |  |

| С  | •          | .210   | -    | 5.33        |   |  |  |

| C1 | .125       | .150   | 3,18 | 3.81        |   |  |  |

| C2 | .015       | .055   | 0.38 | 1.40        | 2 |  |  |

| D  | .300       | .325   | 7.62 | 8.26        | 3 |  |  |

| E  | .100       | BSC    | 2.54 | BSC         | 4 |  |  |

| F  | .014       | .022   | 0.35 | 0.56        |   |  |  |

| F1 | .045       | .070   | 1.14 | 1.78        |   |  |  |

| F2 | .008       | .014   | 0.20 | 0.35        |   |  |  |

| G  | .300       | .400   | 7.62 | 10.16       | 5 |  |  |

| Н  | .005       | -      | 0.13 | -           |   |  |  |

| L  | .115       | .160   | 2.92 | 4.06        |   |  |  |

## **NOTES:**

- 1. 'A' AND 'B' DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.006 IN. PER SIDE.

- 2. 'C2' SHALL BE MEASURED FROM THE SEATING PLANE TO THE BASE PLANE.

- 3. 'D' SHALL BE MEASURED WITH THE LEADS CONSTRAINED TO BE PERPENDICULAR TO THE BASE PLANE.

- 4. THE BASIC LEAD SPACING IS 0.100 IN. BETWEEN CENTERLINES. EACH LEAD CENTERLINE SHALL BE LOCATED WITHIN  $\pm 0.010$  IN. OF ITS EXACT TRUE POSITION.

- 5. 'G' SHALL BE MEASURED AT THE LEAD TIPS WITH THE LEADS UNCONSTRAINED.

- 6. CONTROLLING DIMENSION: INCHES. MILLIMETERS SHOWN FOR REFERENCE ONLY.

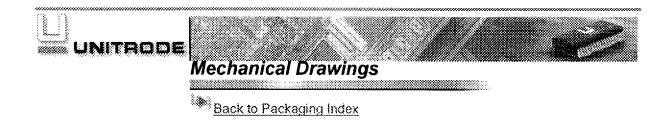

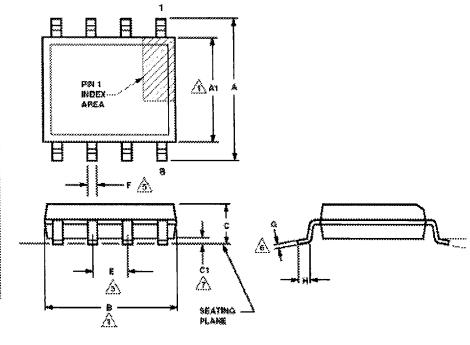

# 8-PIN SOIC SURFACE MOUNT~ D, DP PACKAGE SUFFIX

|    |      | DIMENS  | SIONS  |        |

|----|------|---------|--------|--------|

|    | INC  | HES     | MILLIM | IETERS |

|    | MIN  | MIN MAX |        | MAX    |

| Α  | .228 | .244    | 5.80   | 6.20   |

| Α1 | .150 | .158    | 3.80   | 4.00   |

| В  | .189 | .196    | 4.80   | 4.98   |

| С  | .053 | .069    | 1.35   | 1.75   |

| C1 | .004 | .009    | 0.10   | 0.23   |

| Ε  | .050 | BSC     | 1.27   | BSC    |

| F  | .014 | .019    | 0.35   | 0.48   |

| G  | .007 | .010    | 0.19   | 0.25   |

| Н  | .016 | .035    | 0.41   | 0.89   |

| 8  | 0°   | 8°      | 0°     | 8°     |

#### NOTES:

'Al' AND 'B' DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSION SHALL NOT EXCEED 0.006 IN. PER SIDE.

2. LEADS SHALL BE COPLANAR WITHIN 0.004 IN. AT THE SEATING PLANE.

THE BASIC LEAD SPACING IS 0.050 IN. BETWEEN CENTERLINES. EACH LEAD CENTERLINE SHALL BE LOCATED WITHIN ±0.004 IN. OF ITS EXACT TRUE POSITION.

4. CONTROLLING DIMENSION: INCHES. MILLIMETERS SHOWN FOR REFERENCE ONLY.

DIMENSION 'F' DOES NOT INCLUDE DAMBAR PROTRUSION. THE DAMBAR PROTRUSION(S) SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 'F' MAXIMUM BY MORE THAN 0.003 IN. DAMBAR CAN NOT BE LOCATED ON THE LOWER RADIUS OR THE LEAD FOOT.

THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.004 IN. AND 0.010 IN. FROM THE LEAD TIP.

'C1' IS DEFINED AS THE DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT OF THE PACKAGE BODY (BASE PLANE).

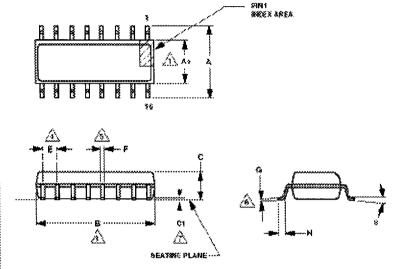

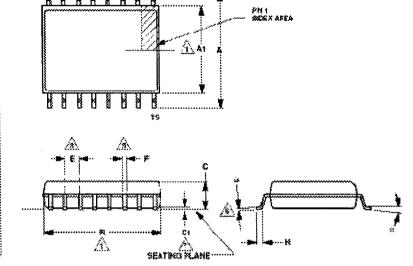

# 16-PIN SOIC SURFACE MOUNT~ D, DP, DS PACKAGE SUFFIX

| DIMENSIONS |      |        |      |        |  |  |

|------------|------|--------|------|--------|--|--|

|            | INC  | INCHES |      | IETERS |  |  |

|            | MIN  | MAX    | MIN  | MAX    |  |  |

| Α          | .228 | .244   | 5.80 | 6.20   |  |  |

| A1         | .150 | .158   | 3.80 | 4.00   |  |  |

| В          | .386 | .393   | 9.80 | 9.98   |  |  |

| С          | .053 | .069   | 1.35 | 1.75   |  |  |

| C1         | .004 | .009   | 0.10 | 0.22   |  |  |

| E          | .050 | BSC    | 1.27 | BSC    |  |  |

| F          | .014 | .019   | 0.36 | 0.48   |  |  |

| G          | .007 | .010   | 0.19 | 0.25   |  |  |

| Н          | .016 | .035   | 0.41 | 0.89   |  |  |

| θ          | O°   | 8°     | 0°   | 8°     |  |  |

#### **NOTES:**

'A1' AND 'B' DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.006 IN. PER SIDE.

2 LEADS SHALL BE COPLANAR WITHIN 0.004 IN. AT THE SEATING PLANE.

4 CONTROLLING DIMENSION: INCHES. MILLIMETERS SHOWN FOR REFERENCE ONLY.

DIMENSION T' DOES NOT INCLUDE DAMBAR PROTRUSION. THE DAMBAR PROTRUSION(S) SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED T' MAXIMUM BY MORE THAN 0.003 IN. DAMBAR CAN NOT BE LOCATED ON THE LOWER RADIUS OR THE LEAD FOOT.

THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.004 IN. AND 0.010 IN. FROM THE LEAD TIP.

'C1' IS DEFINED AS THE DISTANCE FROM THE SEATING PLANE TO THE TO THE LOWEST POINT OF THE PACKAGE BODY (BASE PLANE).

9 8 9 9

#### 16-PIN SOIC SURFACE MOUNT~ DW PACKAGE SUFFIX

|    | DIMENSIONS |      |        |       |  |  |  |

|----|------------|------|--------|-------|--|--|--|

|    | INC        | HES  | MILLIM | ETERS |  |  |  |

|    | MIN        | MAX  | MIN    | MAX   |  |  |  |

| Α  | .394       | .419 | 10.00  | 10.64 |  |  |  |

| A1 | .292       | .299 | 7.42   | 7.59  |  |  |  |

| В  | .403       | .413 | 10.24  | 10.49 |  |  |  |

| С  | .097       | .104 | 2.48   | 2.64  |  |  |  |

| C1 | .004       | .011 | 0.10   | 0.28  |  |  |  |

| E  | .050       | BSC  | 1.27   | BSC   |  |  |  |

| F  | .014       | .019 | 0.36   | 0.48  |  |  |  |

| G  | .009       | .012 | 0.23   | 0.30  |  |  |  |

| Н  | .018       | .035 | 0.46   | 0.89  |  |  |  |

| Ü  | 0°         | 8°   | 0°     | 8°    |  |  |  |

#### **NOTES:**

- 'A1' AND 'B' DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.006 IN. PER SIDE.

- 2. LEADS SHALL BE COPLANAR WITHIN 0.004 IN. AT THE SEATING PLANE.

- THE BASIC LEAD SPACING IS 0.050 IN. BETWEEN CENTERLINES. EACH LEAD CENTERLINE SHALL BE LOCATED WITHIN ±0.004 IN. OF ITS EXACT TRUE POSITION.

- 4. CONTROLLING DIMENSION: INCHES. MILLIMETERS SHOWN FOR REFERENCE ONLY.

- DIMENSION 'F' DOES NOT INCLUDE DAMBAR PROTRUSION. THE DAMBAR PROTRUSION(S) SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 'F' MAXIMUM BY MORE THAN 0.003 IN. DAMBAR CAN NOT BE LOCATED ON THE LOWER RADIUS OR THE LEAD FOOT.

- THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.004 IN. AND 0.010 IN. FROM THE LEAD TIP.

- 'C1' IS DEFINED AS THE DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT OF THE PACKAGE BODY (BASE PLANE).

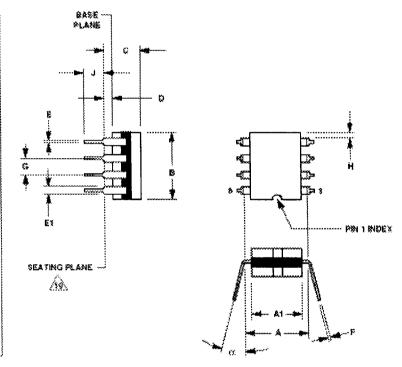

#### 8-PIN CERAMIC DIP ~ J PACKAGE SUFFIX

|    | INCI  | INCHES |      | MILLIMETERS |   |  |

|----|-------|--------|------|-------------|---|--|

|    | MIN   | MAX    | MIN  | MAX         |   |  |

| Α  | 0.290 | 0.320  | 7.37 | 8.13        | 7 |  |

| Α1 | 0.220 | 0.310  | 5.59 | 7.87        | 4 |  |

| В  | -     | 0.405  | -    | 10.29       | 4 |  |

| С  | -     | 0.200  | -    | 5.08        |   |  |

| D  | 0.015 | 0.060  | 0.38 | 1.52        | 3 |  |

| Ε  | 0.014 | 0.026  | 0.36 | 0.66        | 8 |  |

| E1 | 0.045 | 0.065  | 1.14 | 1.65        | 2 |  |

| F  | 0.008 | 0.018  | 0.20 | 0.46        | 8 |  |

| G  | 0.100 | BSC    | 2.54 | BSC         | 5 |  |

| Н  | 0.005 | -      | 0.13 | -           | 6 |  |

| J  | 0.125 | 0.200  | 3.18 | 5,08        |   |  |

| ø. | 0°    | 15°    | 0°   | 15°         | : |  |

# NOTES:

- 1. INDEX AREA: A NOTCH OR A PIN ONE IDENTIFICATION MARK SHALL BE LOCATED ADJACENT TO PIN ONE. THE MANUFACTURER'S IDENTIFICATION SHALL NOT BE USED AS A PIN ONE IDENTIFICATION MARK.

- 2. THE MINIMUM LIMIT FOR DIMENSION 'E1' MAY BE 0.023 (0.58mm) FOR LEADS NUMBER 1, 4, 5 AND 8 ONLY.

- **3.** DIMENSION 'D' SHALL BE MEASURED FROM THE SEATING PLANE TO THE BASE PLANE.

- THIS DIMENSION ALLOWS FOR OFF-CENTER LID, MENISCUS AND GLASS OVERRUN.

- 5. THE BASIC PIN SPACING IS 0.100 (2.54mm) BETWEEN CENTERLINES. EACH PIN CENTERLINE SHALL BE LOCATED WITHIN ±0.010 (0.25mm) OF ITS EXACT TRUE POSITION

- 6. APPLIES TO ALL FOUR CORNERS (LEADS NUMBER 1, 4, 5 AND 8).

- 7. DIMENSION 'A' SHALL BE MEASURED AT THE CENTERLINE OF THE LEADS WHEN  $\alpha = 0^{\circ}$ .

- 8. THE MAXIMUM LIMITS OF DIMENSIONS 'E' AND 'F' SHALL BE MEASURED AT THE CENTER OF THE FLAT WHEN SOLDER DIP IS APPLIED.

- 9. CONTROLLING DIMENSION: INCHES. MILLIMETERS SHOWN FOR REFERENCE ONLY.

- THE SEATING PLANE IS LOCATED AT THE LOWEST POINT ON THE LEAD AT WHICH THE LEAD WIDTH EXCEEDS 0.040 (1.02mm) MINIMUM, EXCLUDING ANY HALF LEADS AT THE PACKAGE ENDS.