# RENESAS 2.5V Single Data Rate 1:5 Clock Buffer Terabuffer™ Jr.

# **DATA SHEET**

#### **FEATURES**:

- Optimized for 2.5V LVTTL

- Guaranteed Low Skew < 25ps (max)</li>

- Very low duty cycle distortion < 300 (max)</li>

- High speed propagation delay < 1.8ns. (max)

- Up to 200MHz operation

- Very low CMOS power levels

- · Hot insertable and over-voltage tolerant inputs

- 1:5 fanout buffer

- 2.5V VDD

- Available in TSSOP package

- For New Designs use functional replacement 8L30110

FUNCTIONAL BLOCK DIAGRAM

### **APPLICATIONS:**

Clock and signal distribution

### **DESCRIPTION**:

The 5T9050 2.5V single data rate (SDR) clock buffer is a single-ended input to five single-ended outputs buffer built on advanced metal CMOS technology. The SDR clock buffer fanout from a single input to five single-ended outputs reduces the loading on the preceding driver and provides an efficient clock distribution network. Multiple power and grounds reduce noise.

# GL D G OUTPUT 🔁 Q1 CONTROL OUTPUT D Q2 CONTROL А OUTPUT ─ Q3 CONTROL OUTPUT ⊃ Q4 CONTROL OUTPUT $ightarrow Q_5$ CONTROL

#### 5T9050 REVISION A 11/2/15

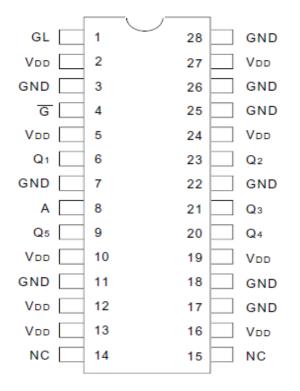

#### **PIN CONFIGURATION**

### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Symbol | Description          | Max              | Unit |

|--------|----------------------|------------------|------|

| Vdd    | Power Supply Voltage | -0.5 to +3.6     | V    |

| VI     | Input Voltage        | -0.5 to +3.6     | V    |

| Vo     | Output Voltage       | -0.5 to VDD +0.5 | V    |

| TSTG   | Storage Temperature  | –65 to +165      | °C   |

| τJ     | Junction Temperature | 150              | °C   |

NOTE:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **CAPACITANCE(1)** (TA = +25°C, F = 1.0MHz)

| Symbol | Parameter         | Min | Tvp. | Max. | Unit |

|--------|-------------------|-----|------|------|------|

| Cin    | Input Capacitance | _   | 6    | _    | pF   |

NOTE:

1. This parameter is measured at characterization but not tested.

### TSSOP TOP VIEW

# **RECOMMENDED OPERATING RANGE**

| Symbol | Description                   | Min. | Тур. | Max. | Unit |

|--------|-------------------------------|------|------|------|------|

| ТА     | Ambient Operating Temperature | -40  | +25  | +85  | °C   |

| Vdd    | Internal Power Supply Voltage | 2.3  | 2.5  | 2.7  | V    |

### **PIN DESCRIPTION**

| Symbol | I/O | Tvpe  | Description                                                                                                                                                                                               |

|--------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A      |     | LVTTL | Clock input                                                                                                                                                                                               |

| G      | Ι   | LVTTL | Gate control for Qn outputs. When $\overline{G}$ is LOW, these outputs are enabled. When $\overline{G}$ is HIGH, these outputs are asynchronously disabled to the level designated by GL <sup>(1)</sup> . |

| GL     |     | LVTTL | Specifies output disable level. If HIGH, the outputs disable HIGH. If LOW, the outputs disable LOW.                                                                                                       |

| Qn     | 0   | LVTTL | Clock outputs                                                                                                                                                                                             |

| Vdd    |     | PWR   | Power supply for the device core, inputs, and outputs                                                                                                                                                     |

| GND    |     | PWR   | Power supply return for power                                                                                                                                                                             |

NOTE:

1. Because the gate controls are asynchronous, runt pulses are possible. It is the user's responsibility to either time the gate control signals to minimize the possibility of runt pulses or be able to tolerate them in down stream circuitry.

# DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE<sup>(1)</sup>

| Symbol | Parameter                    | Test Conditions         | Min.      | Typ. <sup>(4)</sup> | Max   | Unit |

|--------|------------------------------|-------------------------|-----------|---------------------|-------|------|

| Lн     | Input HIGH Current           | VDD = 2.7V VI = VDD/GND | _         |                     | ±5    | μA   |

| lı.    | Input LOW Current            | VDD = 2.7V VI = GND/VDD |           |                     | ±5    |      |

| Vik    | Clamp Diode Voltage          | VDD = 2.3V, IN = -18mA  |           | - 0.7               | - 1.2 | V    |

| Vin    | DC Input Voltage             |                         | - 0.3     |                     | +3.6  | V    |

| Vih    | DC Input HIGH <sup>(2)</sup> |                         | 1.7       |                     | _     | V    |

| VIL    | DC Input LOW <sup>(3)</sup>  |                         | _         |                     | 0.7   | V    |

| Vон    | Output HIGH Voltage          | lон = -12mA             | Vdd - 0.4 |                     |       | V    |

|        |                              | Іон = -100μА            | Vdd - 0.1 |                     | _     | V    |

| Vol    | Output LOW Voltage           | $I_{OL} = 12mA$         | _         |                     | 0.4   | V    |

|        |                              | lol = 100μA             | -         |                     | 0.1   | V    |

NOTES:

1. See RECOMMENDED OPERATING RANGE table.

2. Voltage required to maintain a logic HIGH.

3. Voltage required to maintain a logic LOW.

4. Typical values are at VDD = 2.5V, +25°C ambient.

# **POWER SUPPLY CHARACTERISTICS**

| Symbol | Parameter                                      | Test Conditions <sup>(1)</sup>                                                         | Тур. | Max | Unit   |

|--------|------------------------------------------------|----------------------------------------------------------------------------------------|------|-----|--------|

| Idda   | Quiescent Vod Power Supply Current             | V <sub>DD</sub> = Max., Reference Clock = LOW<br>Outputs enabled, All outputs unloaded | 1    | 1.5 | mA     |

| Iddd   | Dynamic Vod Power Supply<br>Current per Output | V <sub>DD</sub> = Max., C <sub>L</sub> = 0pF                                           | 100  | 150 | μA/MHz |

| Ітот   | Total Power Vod Supply Current                 | Vdd = 2.5V., Freference clock = $100MHz$ , Cl = $15pF$                                 | 50   | 65  | mA     |

|        |                                                | VDD = 2.5V., FREFERENCE CLOCK = 200MHz, CL = 15pF                                      | 75   | 100 |        |

NOTE:

1. The termination resistors are excluded from these measurements.

### INPUT AC TEST CONDITIONS

| Symbol | Parameter                                               | Value | Units |

|--------|---------------------------------------------------------|-------|-------|

| VIH    | Input HIGH Voltage                                      | Vdd   | V     |

| VIL    | Input LOW Voltage                                       | 0     | V     |

| Vth    | Input Timing Measurement Reference Level <sup>(1)</sup> | Vdd/2 | V     |

| tr, tr | Input Signal Edge Rate <sup>(2)</sup>                   | 2     | V/ns  |

NOTES:

1. A nominal 1.25V timing measurement reference level is specified to allow constant, repeatable results in an automatic test equipment (ATE) environment.

2. The input signal edge rate of 2V/ns or greater is to be maintained in the 10% to 90% range of the input waveform.

### AC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE<sup>(4)</sup>

| Symbol           | Parameter                                              | Min. | Тур. | Max      | Unit |

|------------------|--------------------------------------------------------|------|------|----------|------|

| Skew Parameters  |                                                        |      | •    | <u>.</u> |      |

| tsк(o)           | Same Device Output Pin-to-Pin Skew <sup>(1)</sup>      |      | _    | 25       | ps   |

| tsk(p)           | Pulse Skew <sup>(2)</sup>                              |      | _    | 300      | ps   |

| tsk(pp)          | Part-to-Part Skew <sup>(3)</sup>                       | _    | _    | 300      | ps   |

| Propagation Dela | У                                                      |      |      | _        |      |

| <b>t</b> PLH     | Propagation Delay A to Qn                              | _    | -    | 1.8      | ns   |

| teнi             |                                                        |      |      |          |      |

| tr               | Output Rise Time (20% to 80%)                          | 350  | _    | 850      | ps   |

| tF               | Output Fall Time (20% to 80%)                          | 350  | _    | 850      | DS   |

| fo               | Frequency Range                                        | _    | _    | 200      | MHz  |

| Output Gate Enab | 1 3 0                                                  |      |      |          |      |

| <b>t</b> PGE     | Output Gate Enable to On                               |      | _    | 3.5      | ns   |

| tpgd             | Output Gate Enable to Qn Driven to GL Designated Level | _    | _    | 3        | ns   |

NOTES:

1. Skew measured between all outputs under identical input and output transitions and load conditions on any one device.

2. Skew measured is the difference between propagation delay times tPHL and tPLH of any output under identical input and output transitions and load conditions on any one device.

3. Skew measured is the magnitude of the difference in propagation times between any outputs of two devices, given identical transitions and load conditions at identical VDD levels and

temperature.

4. Guaranteed by design.

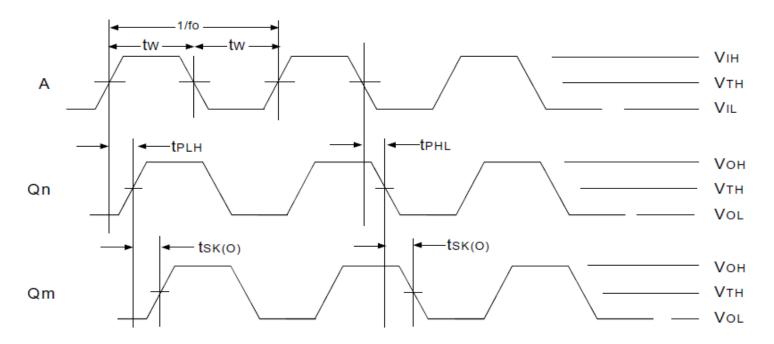

# AC TIMING WAVEFORMS

#### Propagation and Skew Waveforms

NOTE: Pulse Skew is calculated using the following expression:

tsk(p) = | tphl - tplh |

where tPHL and tPLH are measured on the controlled edges of any one output from rising and falling edges of a single pulse. Please note that the tPHL and tPLH shown are not valid measurements for this calculation because they are not taken from the same pulse.

NOTE:

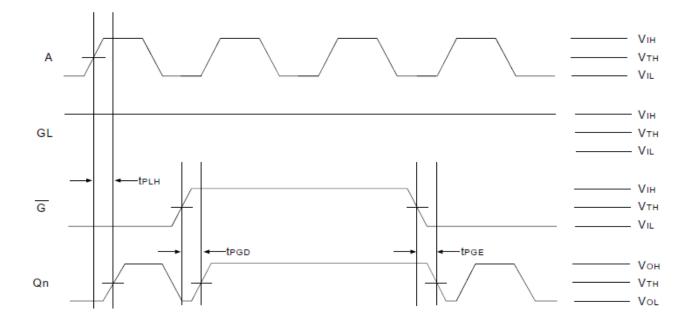

#### Gate Disable/Enable Showing Runt Pulse Generation

As shown, it is possible to generate runt pulses on gate disable and enable of the outputs. It is the user's responsibility to time their  $\overline{G}$  signal to avoid this problem.

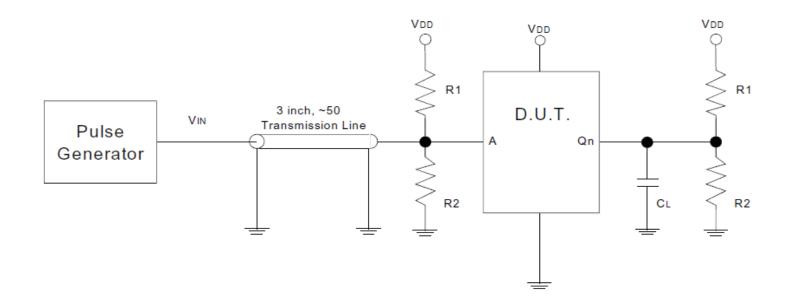

# **TEST CIRCUIT AND CONDITIONS**

Test Circuit for Input/Output

| Symbol | $V_{DD} = 2.5V \pm 0.2V$ | Unit |

|--------|--------------------------|------|

| VTH    | Vdd / 2                  | V    |

| R1     | 100                      | Ω    |

| R2     | 100                      | Ω    |

| CL     | 15                       | pF   |

# **INPUT/OUTPUT TEST CONDITIONS**

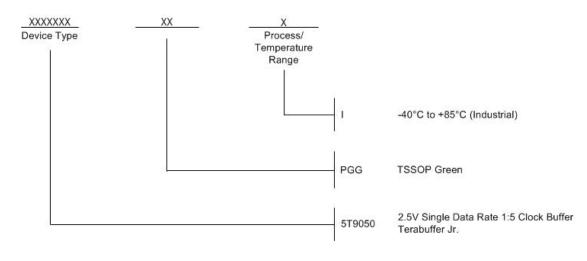

# **ORDERING INFORMATION**

# **REVISION HISTORY**

| Rev | Table | Page | Discription of Change                                                              | Date    |

|-----|-------|------|------------------------------------------------------------------------------------|---------|

| A   |       | 1    | NRND - Not Recommended for New Designs                                             | 5/5/13  |

| А   |       | 1    | Product Discontinuation Notice - Last time buy expires 11/2/2016.<br>PDN# CQ-15-05 | 11/2/15 |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/