#### **PRELIMINARY**

# August 1995

# DM74ALS996 TRI-STATE® Octal **D-Type Edge-Triggered Readback Latches**

# **General Description**

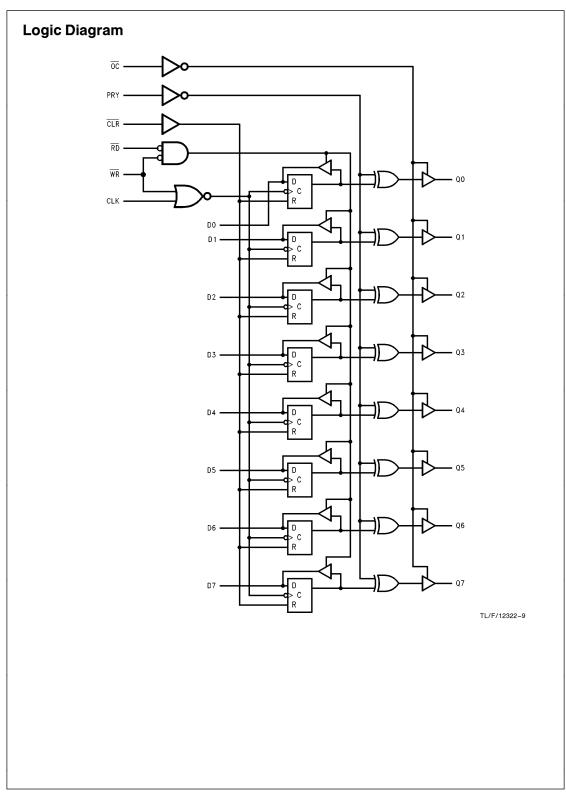

These 8-bit registers are designed specifically for storing the contents of the input data bus plus providing the capability of reading-back the stored data onto that bus. The Q outputs are designed with bus driving capability.

The edge-triggered flip-flops enter the data on the low-tohigh transition of the clock (CLK) when enable (WR) is low. Data can be read-back onto the data inputs by taking the read input (RD) low, in addition to having WR low. Whenever WR is high, both the read-back and write modes are disabled. Transitions on WR should only be made with CLK high in order to prevent false clocking.

The polarity of the Q outputs can be controlled by the polarity input PRY. When PRY is high, Q will be the same as is stored in the flip-flops. When PRY is low, the output data will be inverted. The Q outputs can be placed into TRI-STATE by taking the output control (OC) high. The output control OC does not affect the internal operations of the register. Old data can be retained or new data can be entered while the outputs are off.

A low level at the clear input (CLR) resets the internal registers low. The clear function is asynchronous and overrides all other register functions.

#### **Features**

- TRI-STATE I/O-type read-back inputs

- TRI-STATE bus-driving outputs

- Bus-structured pinout

- True or complementary data at Q outputs

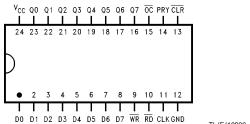

# **Connection Diagram**

TL/F/12322-1

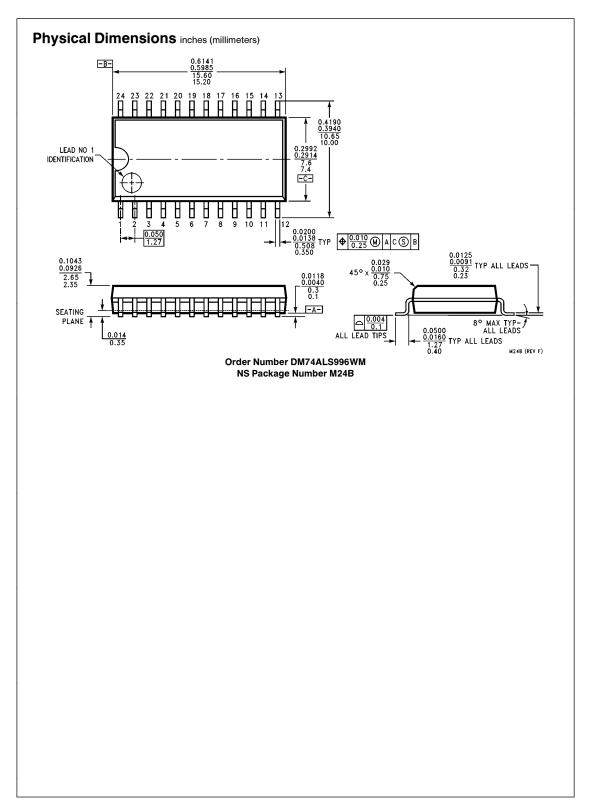

Order Number DM74ALS996WM or DM74ALS996NT See NS Package Number M24B or N24C

# **Absolute Maximum Ratings** (Note 1)

| Supply Voltage                       | 7V                                              |

|--------------------------------------|-------------------------------------------------|

| Input Voltage (Control Pins)         | 7V                                              |

| Input Voltage (D Inputs and          |                                                 |

| Disabled TRI-STATE Outputs)          | 5.5V                                            |

| Operating Free Air Temperature Range | 0°C to +70°C                                    |

| Storage Temperature Range            | $-65^{\circ}\text{C}$ to $+150^{\circ}\text{C}$ |

Note 1: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the "Electrical Characteristics" table are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

# **Recommended Operating Conditions**

| Parameter                             | Min  | Nom | Max  | Unit |

|---------------------------------------|------|-----|------|------|

| Supply Voltage (V <sub>CC</sub> )     | 4.5  | 5.5 | 5.5  | V    |

| High-Level Input Voltage (VIH)        | 2    |     |      | V    |

| Low-Level Input Voltage (VIL)         |      |     | 8.0  | V    |

| High-Level Output Current (IOH)       |      |     |      |      |

| Q                                     |      |     | -2.6 | mΑ   |

| D                                     |      |     | -0.4 | mA   |

| Low-Level Output Current (IOL)        |      |     |      |      |

| Q                                     |      |     | 24   | mΑ   |

| D                                     |      |     | 8    | mΑ   |

| Clock Frequency (f <sub>CLOCK</sub> ) | 0    |     | 35   | MHz  |

| Pulse Duration                        |      |     |      |      |

| CLR Low                               | 10   |     |      |      |

| CLK Low                               | 14.5 |     |      | ns   |

| CLK High                              | 14.5 |     |      |      |

| Setup Time (t <sub>SU</sub> )         |      |     |      |      |

| Data before CLK                       | 15   |     |      |      |

| CLK High before WR                    | 15   |     |      | ns   |

| CLR High (Inactive) before CLK        | 10   |     |      |      |

| Hold Time (t <sub>H</sub> )           |      |     |      |      |

| Data after CLK                        | 0    |     |      | no   |

| RD High after CLK                     | 5    |     |      | ns   |

# **Electrical Characteristics**

| Symbol           | Parameter                 |                       | Co                                                  | nditions                                                  | Min                       | Тур            | Max            | Units |

|------------------|---------------------------|-----------------------|-----------------------------------------------------|-----------------------------------------------------------|---------------------------|----------------|----------------|-------|

| $V_{IK}$         | Input Clamp Voltage       |                       | $V_{CC} = 4.5V$                                     | $I_{\text{I}} = -18 \text{ mA}$                           |                           |                | -1.2           | V     |

| V <sub>OH</sub>  | High-Level Output Voltage | All Outputs<br>Q      | $V_{CC} = 4.5V \text{ to } 5.5V$<br>$V_{CC} = 4.5V$ | $I_{OH} = -0.4 \text{ mA}$<br>$I_{OH} = -2.6 \text{ mA}$  | V <sub>CC</sub> -2<br>2.4 | 3.2            |                | V     |

| V <sub>OL</sub>  | Low-Level Output Voltage  | D Outputs             | $V_{CC} = 4.5V$ $V_{CC} = 4.5V$                     | $I_{OL} = 4 \text{ mA}$<br>$I_{OL} = 8 \text{ mA}$        |                           | 0.25<br>0.35   | 0.4<br>0.5     | V     |

| V <sub>OL</sub>  | Low-Level Output Voltage  | Q Outputs             | $V_{CC} = 4.5V$ $V_{CC} = 4.5V$                     | $I_{OL} = 12 \text{ mA}$<br>$I_{OL} = 24 \text{ mA}$      |                           | 0.25<br>0.35   | 0.4<br>0.5     | V     |

| l <sub>OZH</sub> |                           | Q Outputs             | $V_{CC} = 5.5V$                                     | $V_I = 2.7V$                                              |                           |                | 20             | μΑ    |

| l <sub>OZL</sub> |                           | Q Outputs             | $V_{CC} = 5.5V$                                     | $V_I = 0.4V$                                              |                           |                | -20            | μΑ    |

| lį               |                           | D Inputs<br>All Other | $V_{CC} = 5.5V$ $V_{CC} = 5.5V$                     | $V_{I} = 5.5V$<br>$V_{I} = 5.5V$                          |                           |                | 0.1<br>0.1     | mA    |

| I <sub>IH</sub>  |                           | D Inputs<br>All Other | $V_{CC} = 5.5V$                                     | $V_I = 2.7V$                                              |                           |                | 20<br>20       | μΑ    |

| I <sub>IL</sub>  |                           | D Inputs<br>All Other | $V_{CC} = 5.5V$                                     | $V_I = 0.4V$                                              |                           |                | -0.1<br>-0.1   | mA    |

| Io               |                           |                       | $V_{CC} = 5.5V$                                     | $V_{O} = 2.25V$                                           | -30                       |                | -112           | mA    |

| Icc              |                           |                       | V <sub>CC</sub> = 5.5V<br>WR, RD Low                | Q Outputs High<br>Q Outputs Low<br>Q Outputs in TRI-STATE |                           | 35<br>55<br>42 | 55<br>85<br>85 | mA    |

Note 1: All typical values are at  $V_{CC}=5V,\,T_A=25^{\circ}C.$

Note 2: For I/O ports, the parameter  $I_{\mbox{\scriptsize IH}}$  and  $I_{\mbox{\scriptsize IL}}$  include the TRI-STATE output current.

Note 3: The output conditions have been chosen to produce current that closely approximates one-half of the true I<sub>OS</sub> current.

| Switchin | ıg Characteı | <b>istics</b> (Not | e 1) |

|----------|--------------|--------------------|------|

|          |              |                    |      |

| Parameter           | From<br>(Input) | To<br>(Output) | $egin{aligned} \mathbf{V_{CC}} &= \mathbf{5V} \\ \mathbf{C_L} &= 50  \mathbf{pF} \\ \mathbf{T_A} &= \mathbf{25^{\circ}C} \end{aligned}$ |     |     | $V_{CC}=4.5V$ to 5.5V $C_L=50$ pF $T_A=0^{\circ}C$ to $+70^{\circ}C$ |     | Units |

|---------------------|-----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----------------------------------------------------------------------|-----|-------|

|                     |                 |                | Min                                                                                                                                     | Тур | Max | Min                                                                  | Max |       |

| f <sub>MAX</sub>    |                 |                |                                                                                                                                         | 40  |     | 35                                                                   |     | MHz   |

| t <sub>PLH</sub>    | CLK             | Q              |                                                                                                                                         | 15  | 24  | 5                                                                    | 28  | ns    |

| t <sub>PHL</sub>    | (PRY=H or L)    |                |                                                                                                                                         | 16  | 24  | 5                                                                    | 28  |       |

| t <sub>PLH</sub>    | CLR (PRY=L)     | Q              |                                                                                                                                         | 15  | 23  | 7                                                                    | 27  | ns    |

| t <sub>PHL</sub>    | CLR (PRY=H)     |                |                                                                                                                                         | 13  | 19  | 7                                                                    | 23  | ns    |

| t <sub>PLH</sub>    | PRY             | Q              |                                                                                                                                         | 13  | 20  | 5                                                                    | 23  | ns    |

| t <sub>PHL</sub>    |                 |                |                                                                                                                                         | 13  | 20  | 5                                                                    | 23  | ns    |

| t <sub>PHL</sub>    | CLR             | D              |                                                                                                                                         | 19  | 25  | 8                                                                    | 30  | ns    |

| t <sub>PZL/ZH</sub> | RD              | D              |                                                                                                                                         | 9   | 15  | 3                                                                    | 16  | ns    |

| t <sub>PHZ/LZ</sub> |                 |                |                                                                                                                                         | 10  | 16  | 3                                                                    | 19  | ns    |

| t <sub>PZL/ZH</sub> | WR              | D              |                                                                                                                                         | 9   | 14  | 3                                                                    | 16  | ns    |

| t <sub>PHZ/LZ</sub> |                 |                |                                                                                                                                         | 10  | 16  | 3                                                                    | 19  | ns    |

| t <sub>PZL/ZH</sub> | ОС              | Q              |                                                                                                                                         | 8   | 13  | 4                                                                    | 15  | ns    |

| t <sub>PHZ/LZ</sub> |                 |                |                                                                                                                                         | 4   | 8   | 1                                                                    | 10  | ns    |

Note 1: See Section 5 for test waveforms and output load.

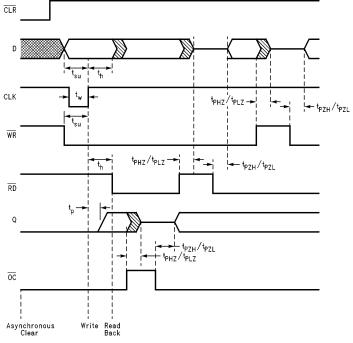

# **Timing Diagram**

TL/F/12322-8

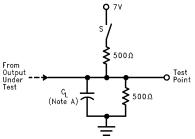

# **Parameter Measurement Information**

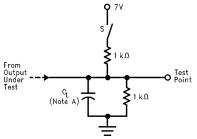

### **Test Circuit for Q Outputs**

TL/F/12322-2

### **Test Circuit for D Outputs**

TL/F/12322-3

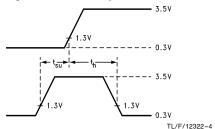

#### Voltage Waveforms—Setup and Hold Times

### Voltage Waveforms—Setup and Hold Times

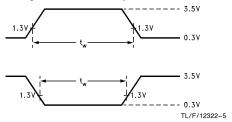

## Voltage Waveforms—Propagation Delay Times

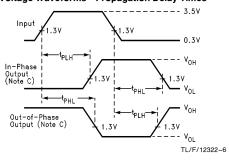

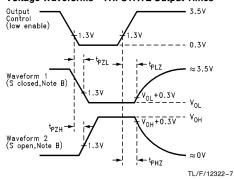

#### Voltage Waveforms—TRI-STATE Output Times

Note A: C<sub>L</sub> includes probe and jig capacitance

Note B: Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control.

Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

$\textbf{Note C:} \ \ \textbf{When measuring propagation delay times of TRI-STATE outputs, switch S is open.}$

**Note D:** All input pulses have the following characteristics: frequency = 1 MHz,  $t_f = t_f = 2$  ns,  $Z_O = 50\Omega$ .

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor**

National Semiconducto Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

**National Semiconductor** Europe

Fax: (+49) 0-180-530 85 86 Fax: (+49) U-18U-35U oo oo Email: onjwege tevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tei: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80 **National Semiconductor** Hong Kong Ltd.

13th Floor, Straight Block,

Ocean Centre, 5 Canton Rd.

Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2408