# BURST EDO

# 1 MEG x 16

#### **FEATURES**

- Burst order, interleave or linear, programmed by executing WCBR cycle after initialization

- Single power supply: +3.3V ±5%

- All inputs and outputs are LVTTL compatible with 5V input/output tolerance

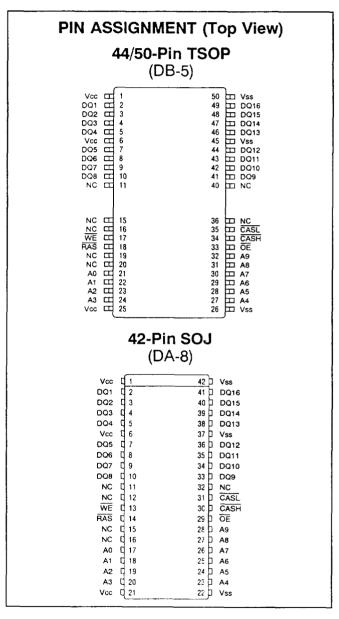

- Industry-standard x16 pinout and packages

- High-performance CMOS silicon-gate process

- Refresh: CAS-BEFORE-RAS (CBR) or RAS ONLY

- 1,024-cycle refresh (10 row-, 10 column-addresses)

- Four-cycle Extended Data-Out (EDO) burst accesses

| OPTIONS                                                                                                                         | MARKING        |

|---------------------------------------------------------------------------------------------------------------------------------|----------------|

| <ul> <li>Timing</li> <li>52ns access; 15ns cycle</li> <li>60ns access; 16.6ns cycle</li> <li>70ns access; 20ns cycle</li> </ul> | -5<br>-6<br>-7 |

| • Packages<br>Plastic TSOP (400 mil)<br>Plastic SOJ (400 mil)                                                                   | TG<br>DJ       |

| · Refresh<br>Standard (1,024 cycles at 16ms)                                                                                    | None           |

# · Part Number Example: MT4LC1M16H5TG-7

# **GENERAL DESCRIPTION**

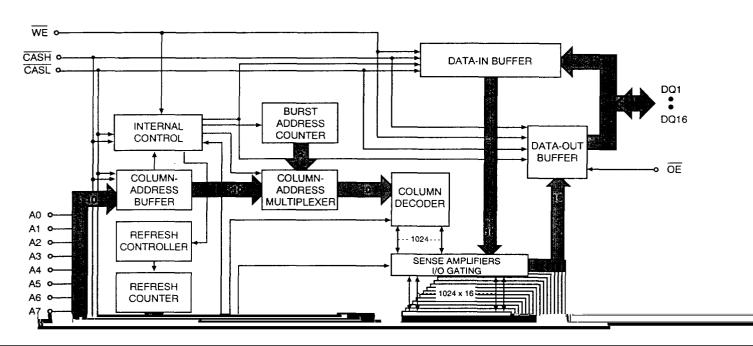

The MT4LC1M16H5 is a randomly accessed solid-state memory containing 16,777,216 bits organized in a  $\times$ 16 configuration. During READ or WRITE cycles, each bit is uniquely addressed through the 20 address bits, which are entered 10 bits (A0-A9) at  $\overline{RAS}$  time and 10 bits (A0-A9) at  $\overline{CAS}$  time.

The MT4LC1M16H5 is a burst access DRAM in which all IEAD and WORD WRITE access cycles occur in bursts of four. The bursts wrap around on a 4-byte boundry. This means that the two least significant bits of the  $\overline{CAS}$  ( $\overline{CASL}$  and  $\overline{CASH}$ ) address are modified internally to produce each address of the burst sequence. The burst type, interleave or linear, is determined by executing a VCBR cycle (CBR cycle with  $\overline{WE}$  LOW) with address A0 set to either HIGH or LOW. A0 LOW will program the device to execute linear bursts, A0 HIGH will program the bursts to be interleave. For future compatability it is strongly recommended that the information (0010 000x<sub>B</sub>) where  $\Xi = A0$  is supplied on addresses A7-A0 during the WCBR

cycle. The WCBR cycle must be followed by a  $\overline{RAS}$ -ONLY or CBR REFRESH cycle to exit this programming mode.

RASHIGH and CASHIGH (CASL and CASH) terminates burst operations in the selected row, resets the burst counter, closes that row and decreases chip current to a reduced standby level. The chip is precharged for the next access during the RAS HIGH time.

## FEAD CYCLE

A READ cycle is selected by WE input HIGH prior to the first CAS LOW transition of the burst (CASL or CASH). Euring the READ burst cycle the WE input must remain FIGH for the burst to continue. Transition of the WE input during a burst causes the burst to terminate and places the outputs in a High-Z state. After a terminated burst, the next falling edge of CAS (CASL or CASH) will start a new burst a cess at the address present on the external address bus.

READ cycles always produce 16 bits of data (word). The READ timing is determined by the first  $\overline{CAS}$  ( $\overline{CASL}$  or  $\overline{CASH}$ ) to transition LOW and the last  $\overline{CAS}$  to transition b tck HIGH. Both  $\overline{CAS}$  signals may transistion but only one  $\overline{CAS}$  is required for READ operations. If only one  $\overline{CAS}$  is used for READ operations, the unused  $\overline{CAS}$  must be held F IGH during the READ cycle.

## **WORD WRITE CYCLE**

A WORD WRITE cycle is selected by WE input LOW during the first CASL and CASH LOW transition of the burst. Since CASL controls the lower byte (DQ1-DQ8) and CASH controls the upper byte (DQ9-DQ16), both CASL and CASH must transition for both bytes to be written. If only CASL or CASH transitions then only that corresponding byte will be written.

During a WORD WRITE cycle, data-in (D) is latched by the falling edge of  $\overline{CAS}$  ( $\overline{CASL}$  and  $\overline{CASH}$ ). WE must be LDW prior to  $\overline{CAS}$  ( $\overline{CASL}$  and  $\overline{CASH}$ ) going LOW. This p aces the input/output pins in the High-Z state allowing the data-in (D) to be driven on the bus. WE must remain LDW during the burst operation for the burst to complete.  $\overline{V}'\overline{E}$  going HIGH during the burst terminates the burst operation and places the DQ pins in the High-Z state.

# EYTE WRITE CYCLE

BYTE WRITE cycles can occur as bursts similar to word  $V^TRITE$  cycles. A transition on  $\overline{CASH}$  or  $\overline{CASL}$  increments the burst counter from which both bytes are internally

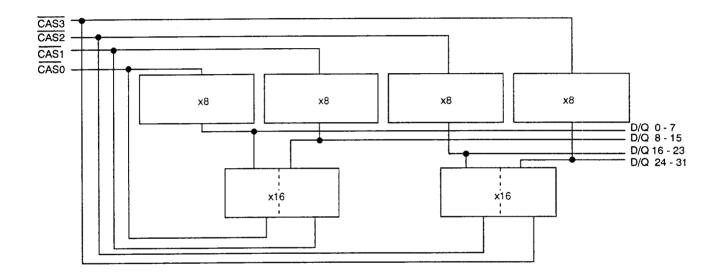

addressed. During WRITEs (WE held LOW), CASL controls the lower byte (DQ1-DQ8) and CASH controls the upper byte DQ9-DQ16). However, in all practicality burst BYTE WRITE cycles do not make sense in most applications and therefore most BYTE WRITEs are single BYTE WRITE cycles. The full bus width needs to be burst accessed to keep the burst counters between devices from becoming out of step with each other. By performing a burst BYTE WRITE, only one of the CAS lines is being toggled, which causes the burst counter to be incremented for the byte not selected. This situation results in the burst counters on separate devices to become out of step with each other. Figure 1 demonstrates a 64-bit bus with two banks of Burst EDO DRAM. The first bank is composed of x8 devices and the second bank uses x16 devices. CAS0 - CAS3 are transitioned first together then independently. When CAS signals of all DRAMs that make up the bus width transition, the bytes are read from the DRAM array as expected and are in step between the DRAM devices. However, when some CAS signals are not transitioned 10 BYTE WRITES, the DRAMs get out of step with each other. Depending on what organization of DRAM is being addressed, different results will occur. This comes from the fact that for x4 and x8 devices, a burst counter controls no more than one byte. However, for x16 devices, the burst counter controls a word (16 bits). This means that on a x16 device a LOW transition of either CASL and CASH will increment both the high byte and low byte burst counter.

Hence, byte WRITE cycles will almost always be a single BYTE WRITE followed by a terminate. Like a WORD WRITE cycle, the first  $\overline{CAS}$  ( $\overline{CASL}$  or  $\overline{CASH}$ ) LOW transition when the  $\overline{WE}$  input is LOW will start the WRITE burst cycle. Successive falling edges of  $\overline{CAS}$  will WRITE to the next address locations in the burst sequence. The burst is terminated by transitioning the  $\overline{WE}$  input.  $\overline{CASL}$  LOW will WRITE the lower BYTE (DQ1-DQ8) while  $\overline{CASH}$  is held HIGH.  $\overline{CASH}$  LOW will WRITE the upper BYTE (DQ9-DQ16) while  $\overline{CASL}$  is held HIGH.

# **MEMORY ARRAY ORGANIZATION**

| D0-7    | D8-15   | D16-23  | D24-31  |

|---------|---------|---------|---------|

| byte 0  | byte 1  | byte 2  | byte 3  |

| byte 4  | byte 5  | byte 6  | byte 7  |

| byte 8  | byte 9  | byte 10 | byte 11 |

| byte 12 | byte 13 | byte 14 | byte 15 |

# **CAS WRITE SEQUENCE**

|                    |     | X       | 8    |     | x16 |     |        |     |

|--------------------|-----|---------|------|-----|-----|-----|--------|-----|

| Beginning          | B0° | ' - B1∄ | B2 🔩 | B3  | В0  | B1  | B2.    | B3  |

| CAS 0-3 transition | B4  | B5      | B6   | B7  | B4  | B5  | - B6 ≜ | B7  |

| CAS 0 tansition    | ∗B8 | ) X     | Χ    | Χ   | B8  | Χ   | Χ      | Х   |

| CAS 1 transition   | X   | B9      | Χ    | Χ   | Х   | B13 | Χ      | Χ   |

| CAS 2 transition   | X   | X       | B10  | Χ   | Х   | Χ   | B10    | Χ   |

| CAS 3 transition   | X   | X       | Χ    | B11 | Х   | Χ   | Χ      | B15 |

<sup>\*</sup>Shaded areas indicate that the byte was written by the  $\overline{\text{CAS}}$  transition, X indicates byte not written.

Figure 1

BYTE WRITE EXAMPLES

**31.** 71.

# MT4LC1M16H5 1 MEG x 16 BURST EDO DRAM

# FUNCTIONAL BLOCK DIAGRAM Burst EDO

# **EDO BURST MODE TRUTH TABLE**

|               |                        |     |      |      |      |    | ADDR | ESSES  | DATA     |

|---------------|------------------------|-----|------|------|------|----|------|--------|----------|

| PRESENT STATE | RESULTING STATE        | RAS | CASL | CASH | WE   | 0E | Row  | Column | DQ       |

| ،\ny          | ldle                   | L→H | Н    | Н    | Х    | Χ  | Х    | X      | High-Z   |

| Idle          | Row Open               | H→L | Н    | Н    | Х    | Х  | ROW  | Х      | High-Z   |

| Idle          | CBR REFRESH            | H→L | L    | L    | Н    | Χ  | X    | X      | High-Z   |

| Row Open      | RAS-ONLY REFRESH       | L   | Н    | Н    | Х    | Х  | ROW  | X      | High-Z   |

| Row Open      | WORD READ burst        | L   | H→L  | Н    | Н    | L  | Х    | COL    | Data-Out |

| Row Open      | WORD READ burst        | L   | Н    | H→L  | Н    | L  | X    | COL    | Data-Out |

| Row Open      | WORD WRITE burst       | L.  | H→L  | H→L  | اــا | Χ  | Х    | COL    | Data-In  |

| Row Open      | LOWER BYTE WRITE burst | L   | H→L  | Н    | L    | Χ  | Х    | COL    | Data-In  |

| Row Open      | UPPER BYTE WRITE burst | L   | Н    | H→L  |      | X  | X    | COL    | Data-In  |

| READ burst    | TERMINATE READ burst   | L   | H/L  | H/L  | H→L  | Χ  | X    | Х      | High-Z   |

| WRITE burst   | TERMINATE WRITE burst  | L   | H/L  | H/L  | L→H  | X  | Х    | X      | High-Z   |

| dle           | PROGRAM burst type     | H→L | L    | L    |      | X  | A01  | Х      | High-Z   |

| PROGRAM       | EXIT PROGRAM MODE      | H→L | L    | L    | Η    | Х  | Х    | Х      | High-Z   |

| PROGRAM       | EXIT PROGRAM MODE      | L   | Н    | Н    | Х    | X  | ROW  | X      | High-Z   |

1. A WCBR cycle determines the burst sequence. A0=LOW sets the burst sequence to linear, A0=HIGH set the burst sequence to interleave. A8 through A9 are "don't cares." A7-A0 should contain the sequence (0010 000x, where x=A0) to ensure future compatability. A refresh cycle (RAS ONLY or CBR) must follow the WCBR cycle to exit the programming mode.

# **INTERLEAVE BURST SEQUENCE TABLE**

|                                             | ADDRESSES USED     |               |               |  |  |  |  |

|---------------------------------------------|--------------------|---------------|---------------|--|--|--|--|

| OPERATION                                   | A9 - A2            | A1            | A0            |  |  |  |  |

| First access, register external CAS address | A9 - A2            | A1            | A0            |  |  |  |  |

| Second access, (first burst address)        | registered A9 - A2 | registered A1 | registered A0 |  |  |  |  |

| Third access (second burst address)         | registered A9 - A2 | registered A1 | registered A0 |  |  |  |  |

| Fourth access (third burst address)         | registered A9 - A2 | registered A1 | registered A0 |  |  |  |  |

# **INTERLEAVE BURST ADDRESS TABLE**

| FIRST ADDRESS | SECOND ADDRESS | THIRD ADDRESS | FOURTH ADDRESS |

|---------------|----------------|---------------|----------------|

| XX00          | XX01           | XX10          | XX11           |

| XX01          | XX00           | XX11          | XX10           |

| XX10          | XX11           | XX00          | XX01           |

| XX11          | XX10           | XX01          | XX00           |

# LINEAR BURST ADDRESS TABLE

| FIRST ADDRESS | SECOND ADDRESS | THIRD ADDRESS | FOURTH ADDRESS |

|---------------|----------------|---------------|----------------|

| XX00          | XX01           | XX10          | XX11           |

| XX01          | XX10           | XX11          | XX00           |

| XX10          | XX11           | XX00          | XX01           |

| XX11          | XX00           | XX01          | XX10           |

# **ABSOLUTE MAXIMUM RATINGS\***

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## ELECTRICAL CHARACTERISTICS AND RECOMMENDED DC OPERATING CONDITIONS

(Notes: 1, 11) ( $Vcc = +3.3V \pm 5\%$ )

| PARAMETER/CONDITION                                                                        | SYMBOL | MIN  | MAX  | UNITS | NOTES |

|--------------------------------------------------------------------------------------------|--------|------|------|-------|-------|

| Supply Voltage                                                                             | Vcc    | 3.13 | 3.47 | V     |       |

| Input High (Logic 1) Voltage, all inputs                                                   | Vih    | 2.0  | 5.5  | V     | 2     |

| Input Low (Logic 0) Voltage, all inputs                                                    | VIL    | -1.0 | 0.8  | V     | 2     |

| INPUT LEAKAGE CURRENT<br>Any input 0V ≤ VIN ≤ 5.5V<br>(All other pins not under test = 0V) | lı     | -2   | 2    | μΑ    |       |

| OUTPUT LEAKAGE CURRENT (Q is disabled; 0V ≤ Vouт ≤ 5.5V)                                   | loz    | -10  | 10   | μΑ    |       |

| OUTPUT LEVELS Output High Voltage (Iouт ≈ -2mA)                                            | Vон    | 2.4  |      | ٧     | 21    |

| Output Low Voltage (Iout = 2mA)                                                            | Vol    |      | 0.4  | V     | 21    |

|                                                                                                                                                                                         |      |     | MAX |     | ]     |       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|-----|-------|-------|

| PARAMETER/CONDITION                                                                                                                                                                     | SYM  | -5  | -6  | -7  | UNITS | NOTES |

| STANDBY CURRENT: (TTL)<br>(RAS = CASL = CASH = VIH)                                                                                                                                     | Icc1 | 2   | 2   | 2   | mA    |       |

| STANDBY CURRENT: (CMOS)<br>(RAS = CASL = CASH = Vcc -0.2V)                                                                                                                              | Icc2 | 500 | 500 | 500 | μА    |       |

| OPERATING CURRENT: Closed Row Burst READ/WRITE Average power supply current; (PC = PC [MIN]; 50% duty cycle on RAS; Open Row, four Cycle Burst, Close Row)                              | lcc3 | 150 | 140 | 130 | mA    | 5, 17 |

| OPERATING CURRENT: Open Row Burst READ/WRITE Average power supply current (Alternating four cycle burst followed by four cycles of inactivity; <sup>t</sup> PC = <sup>t</sup> PC [MIN]) | ICC4 | 110 | 100 | 90  | mA    | 5, 17 |

| REFRESH CURRENT: RAS ONLY Average power supply current (Address Cycling; RAS Cycling; CASL,CASH = VIH; 'RAS = 'RAS [MIN]; 'RP = 'RP [MIN])                                              | Iccs | 190 | 180 | 160 | mA    | 4, 17 |

| REFRESH CURRENT: CBR Average power supply current (RAS, CASL, CASH, Cycling: ¹RAS = ¹RAS [MIN]; ¹RP = ¹RP [MIN])                                                                        | Icc6 | 170 | 160 | 150 | mA    | 4, 6  |

# **CAPACITANCE**

| PARAMETER                            | SYMBOL          | MIN | MAX | UNITS | NOTES |

|--------------------------------------|-----------------|-----|-----|-------|-------|

| Input Capacitance: Addresses, WE, OE | C <sub>I1</sub> |     | 5   | pF    | 3     |

| Input Capacitance: RAS               | C <sub>12</sub> |     | 6   | pF    | 3     |

| Input Capacitance: CASL, CASH        | Сіз             |     | 4   | pF    | 3     |

| Input/Output Capacitance: DQ         | Cio             |     | 7   | рF    | 3     |

# **ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS**

(Notes: 7, 8, 9, 10, 15) ( $Vcc = +3.3V \pm 5\%$ )

| AC CHARACTERISTICS                      |                   |     | -5      |      | -6       |     | -7      |       |             |

|-----------------------------------------|-------------------|-----|---------|------|----------|-----|---------|-------|-------------|

| PARAMETER                               | SYM               | MIN | MAX     | MIN  | MAX      | MIN | MAX     | UNITS | NOTES       |

| Access time from CAS                    | ¹AA               |     | 25      |      | 28.2     |     | 35      | ns    | 12          |

| Column-address setup time               | tASC.             | 1.5 |         | 1.5  |          | 1.5 |         | ns    |             |

| Row-address setup time                  | †ASR              | 1.5 |         | 1.5  |          | 1.5 |         | ns    |             |

| Burst terminate hold time               | <sup>t</sup> BTH  | 3   |         | 3    |          | 3   |         | ns    |             |

| Output disable from burst terminate     | <sup>t</sup> BTHZ | 7   | 13      | 7    | 13       | 7   | 13      | ns    | 13, 16      |

| Access time from CAS                    | <sup>t</sup> CAC  |     | 10      |      | 11.6     |     | 15      | ns    |             |

| Column-address hold time                | <sup>t</sup> CAH  | 8.5 |         | 8.5  |          | 8.5 |         | ns    |             |

| CAS pulse width                         | ¹CAS              | 5   | 10,000  | 5    | 10,000   | 5   | 10,000  | ns    | <u> </u>    |

| CASL and CASH coincident HIGH time      | ¹CCH              | 5   |         | 5    |          | 5   |         | ns    | 18          |

| CAS hold time (CBR or WCBR)             | <sup>t</sup> CHR  | 15  |         | 15   |          | 15  |         | ns    | 6           |

| CAS to output in Low-Z                  | ¹CLZ              | 3   |         | 3    |          | 3   |         | ns    | 13          |

| Data Hold time from CAS LOW             | 1СОН              | 3   |         | 3    |          | 3   |         | ns    | <u> </u>    |

| CAS precharge time                      | ¹CP               | 5   |         | 5    |          | 5   |         | ns    |             |

| CAS precharge time (CBR or WCBR)        | <sup>t</sup> CPN  | 10  |         | 10   |          | 10  |         | ns    |             |

| CAS to RAS precharge time               | <sup>t</sup> CRP  | 10  |         | 10   |          | 10  |         | ns    |             |

| CAS LOW to RAS HIGH (WRITE only)        | ¹CRW              | 15  |         | 16.6 |          | 20  |         | ns    |             |

| Skew between CASL and CASH (WRITE only) | <sup>t</sup> CSK  |     | 2       |      | 2        |     | 2       | ns    | 19          |

| CAS setup time (CBR or WCBR)            | <sup>†</sup> CSR  | 10  |         | 10   |          | 10  |         | ns    | 6           |

| Data-in hold time                       | †DH               | 5   |         | 5    |          | 5   |         | ns    |             |

| Data-in setup time                      | <sup>t</sup> D\$  | 3   |         | 3    |          | 3   |         | ns    |             |

| Ouput Disable                           | 'OD               | 4   | 10      | 4    | 10       | 4   | 15      | ns    | 13          |

| Ouput Enable access time                | <sup>t</sup> OEA  |     | 10      |      | 12       |     | 15      | ns    |             |

| Ouput Enable hold (only near CAS)       | <sup>t</sup> OEH  | 5   |         | 5    |          | 5   |         | ns    | f           |

| OE to output in Low-Z                   | ¹0ELZ             | 3   |         | 3    |          | 3   |         | ns    | 13          |

| OE HIGH pulse width                     | <sup>t</sup> OEP  | 10  |         | 10   |          | 10  |         | ns    |             |

| Ouput Enable setup (only near CAS)      | ¹0ES              | 3   |         | 3    |          | 3   |         | ns    |             |

| Output buffer turn-off delay            | ¹OFF              | 4   | 10      | 4    | 10       | 4   | 15      | ns    | 13          |

| Burst EDO cycle time                    | <sup>t</sup> PC   | 15  |         | 16.6 |          | 20  |         |       | <del></del> |

| Access time from RAS                    | †RAC              |     | 52      |      | 60       |     | 70      | ns    |             |

| Row-address hold time                   | <sup>t</sup> RAH  | 8.5 |         | 8.5  |          | 8.5 | 1       | ns    | <u> </u>    |

| RAS pulse width                         | <sup>t</sup> RAS  | 50  | 125,000 | 60   | 125,000  | 70  | 125,000 | ns    |             |

| Random Read or Write cycle time         | ¹RC               | 90  |         | 110  |          | 130 | 1       |       |             |

| RAS to CAS ce ay time                   | ¹RCD1             | 15  |         | 16.6 |          | 20  |         | ns    |             |

| RAS to CAS de ay time                   | <sup>t</sup> RCD2 | 40  |         | 46.6 |          | 55  |         | ns    |             |

| Read command hold time                  | ¹RCH              | 5   |         | 5    | <u> </u> | 5   |         | ns    |             |

# **ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS**

(Notes: 7, 8, 9, 10, 15) ( $Vcc = +3.3V \pm 5\%$ )

| AC CHARACTERISTICS             |                  |     | -5  | -   | 6   |     | 7   |       |        |

|--------------------------------|------------------|-----|-----|-----|-----|-----|-----|-------|--------|

| PARAMETER                      | SYM              | MIN | MAX | MIN | MAX | MIN | MAX | UNITS | NOTES  |

| Read command setup time        | ¹RCS             | 3   |     | 4   |     | 5   |     | ns    | 1      |

| Refresh period (1,024 cycles)  | ¹REF             |     | 16  |     | 16  |     | 16  | ms    | 1      |

| RAS precharge time             | t <sub>RP</sub>  | 30  |     | 40  |     | 50  |     | ns    |        |

| RAS to CAS precharge time      | <sup>t</sup> RPC | 5   |     | 5   |     | 5   |     | ns    |        |

| RAS hold time                  | <sup>t</sup> RSH | 0   |     | 0   |     | 0   |     | ns    |        |

| Fransition time (rise or fall) | ŤΤ               | 1.5 | 50  | 1.5 | 50  | 1.5 | 50  | ns    |        |

| Burst Terminate pulse width    | ήΡ               | 6   |     | 6   |     | 8   |     | ns    | 14     |

| Write command hold time        | †WCH             | 5   |     | 5   |     | 5   |     | ns    |        |

| WE command setup time          | ¹wcs             | 3   |     | 4   |     | 5   |     | ns    |        |

| Duput Disable from WE LOW      | †WHZ             | 4   | 10  | 4   | 10  | 4   | 15  | ns    | 13, 16 |

| WE hold time (CBR or WCBR)     | †WRH             | 10  |     | 10  |     | 10  |     | ns    |        |

| WE setup time (CBR or WCBR)    | <sup>t</sup> WRP | 10  |     | 10  |     | 10  |     | ns    | 1      |

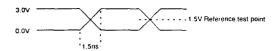

#### Output timing waveform:

Figure 2

TIMING SPECIFICATIONS

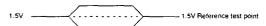

Figure 3 HIGH-Z OUTPUT LOAD

# Q $Z = 50 \Omega$ $0 \times 1.5V$ $0 \times 1.5$

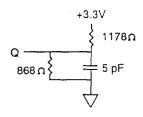

Figure 4

AC TIMING OUTPUT LOAD EQUIVALENT

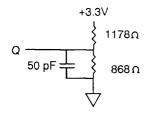

Figure 5

OUTPUT LOAD EQUIVALENT

#### NOTES

- 1. All voltages referenced to Vss.

- 2. Input Power-up:  $V_{\text{IH}} \le +5.5V$  and  $V_{\text{CC}} \le +3.13V$  for  $t \le 200 \text{ms}$ .

- 3. This parameter is sampled. VCC =  $3.3V \pm 5\%$ ; f = 1 MHz.

- 4. Icc is dependent on cycle rates.

- 5. Icc is dependent on output loading and cycle rates. Specified values are obtained with minimum <sup>t</sup>PC and 50 percent duty cycle. The outputs are open.

- *t*. Enables on-chip refresh and address counters.

- 7. Initialization consists of an initial pause of 100µs after power-up followed by eight RAS refresh cycles (RAS ONLY or CBR with WE HIGH). This sequence must be executed before proper device operation is assured. The eight RAS cycle wake-ups should be repeated any time the tREF refresh requirement is exceeded. A WCBR cycle must be executed to initalize the burst type, interleave or linear followed by a RASONLY or CBR REFRESH cycle.

- $\xi$ . AC characteristics assume  ${}^{t}T = 1.5$ ns.

- 4. All output timings are referenced to 1.5V and all input timings are referenced to 1.5V, unless otherwise specified. Inputs must be driven to the appropriate voltage levels indicated by the corresponding timing diagrams when AC specifications are measured, as shown in Figure 2.

- 0. In addition to meeting the transition rate specification, all input signals must transit between VIH and VII. (or between VII and VIH) in a monotonic manner.

- 11. NC pins are assumed to be left floating and are not tested for leakage.

- 12. <sup>t</sup>AA is a calculated specification which is the sum of <sup>t</sup>PC and <sup>t</sup>CAC.

- 13. Output loading is specified with  $C_L = 5pF$  as in Figure 3. Transition is measured  $\pm 200mV$  from steady state voltage. These parameters are sampled.

- 14. Applies only during burst termination operation.

- 15. AC output loading is specified with  $C_L = 50 \text{pF}$  as in Figure 4. Figure 5 is shown for reference. Transition is measured at the 1.5V reference level.

- 16. The DQs will continue to drive data out until both tBTHZ (MIN) and tWHZ (MIN) have been satisfied and will reach the High-Z state once both tBTHZ (MAX) and tWHZ (MAX) have been satisfied.

- 17. Address transitions once per burst access.

- 18. The CASL and CASH HIGH pulse widths must be concurrently HIGH for at least this limit.

- 19. The skew between CASL and CASH is only required for WRITE cycles and is required only between the CASL and CASH for a specific device.

- 20. tCPC is specified for back to back cycles where either CASL or CASH starts the first cycle and the other CAS starts the following cycle.

- 21. The outputs are designed to drive -5mA (IOH) and 4.2mA (IOL) when the 5V-tolerant I/Os are connected to a 5V bus rather than a 3.3V bus.

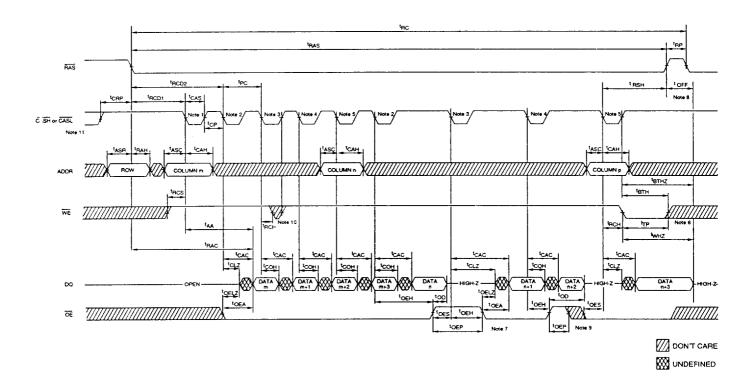

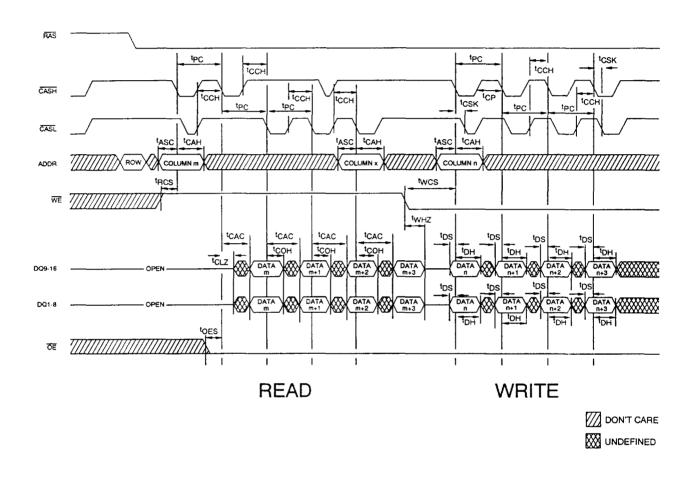

# **BURST EDO READ CYCLE**

- NOTE: 1. Latch column address; start READ cycle.

- 2. Output data 1; increment burst counter.

- 3. Output data 2: increment burst counter.

- 4. Output data 3; increment burst counter.

- 5. Output data 4; latch column address; start READ cycle.

- 6. WE transitioning LOW will terminate the burst and reset the burst counter provided <sup>t</sup>TP and <sup>t</sup>BTH are satisfied. The DQs will continue to drive data out until both tBTHZ (MIN) and tWHZ (MIN) have been satisfied and will reach the High-Z state once both tBTHZ (MAX) and tWHZ (MAX) have been satisfied.

- 7. OES and OEH are only required when OE transitions around the falling edge of CASL and CASH.

- 8. The combination of RAS and CAS HIGH close the row and place the DQs in the High-Z state. OFF is measured from the last signal (RAS or CAS) that transitions HIGH.

- 9. When OE transitions HIGH, the DQ pins are placed in the High-Z state and will remain in the High-Z state until another CAS LOW transition occurs, regardless of the state of OE.

- 10. WE transitioning LOW and returning HIGH prior to CAS going HIGH will not terminate the burst.

- 11. CASE and CASH are shown as if they are tied together and create a single CAS. If not connected, either or both CASL and CASH may toggle. If only one CAS toggles, the other CAS must be held HIGH.

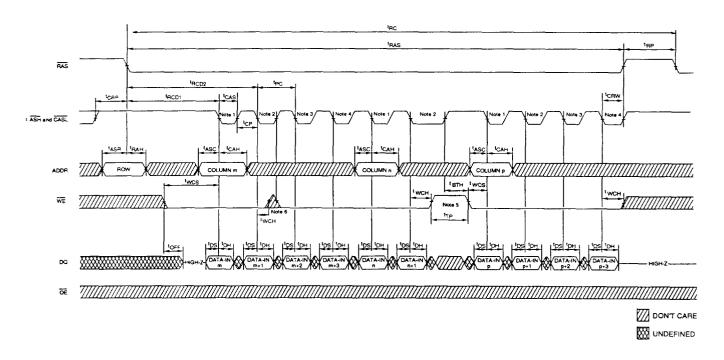

# **BURST EDO** WORD WRITE CYCLE

- 1. Latch column address; start burst WRITE cycle; write data 1.

- 2. Increment burst counter; write data 2.

- 3. Increment burst counter; write data 3.

- 4. Increment burst counter; write data 4.

- 5. WE transitioning HIGH will terminate the burst and reset the burst counter provided <sup>t</sup>TP and <sup>t</sup>BTH are

- 6. WE transitioning HIGH and returning LOW prior to CAS going HIGH will not terminate the burst.

- 7. CASL and CASH are shown as if they are tied together and create a single CAS. If not connected, both CASL and CASH must toggle. If only one CAS toggles, the other CAS must be held HIGH.

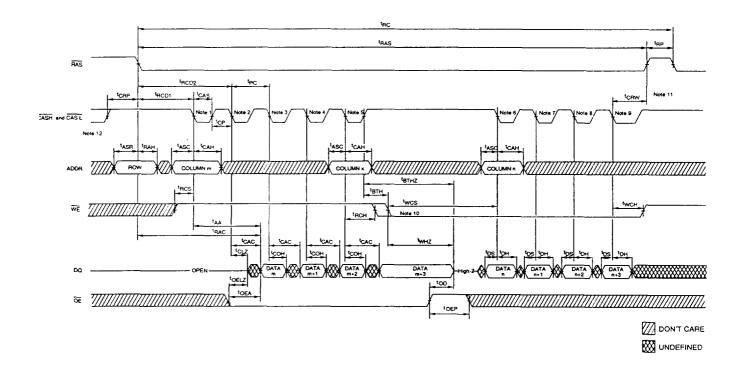

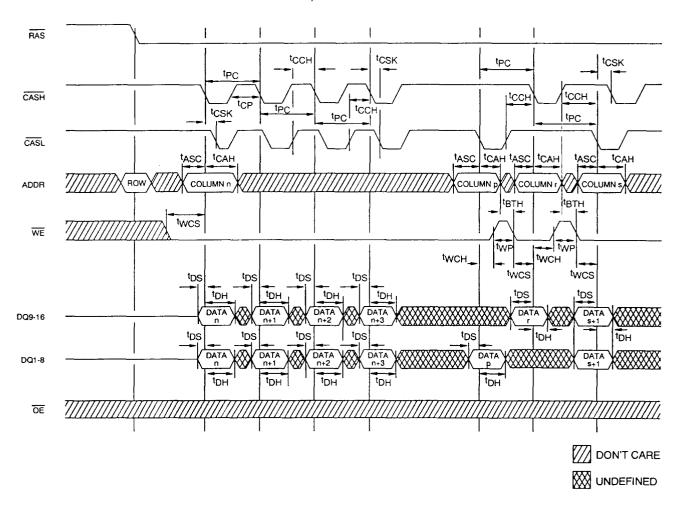

# BURST EDO READ/WRITE (WORD) CYCLE

NOTE

- 1. Latch column address; start burst READ cycle.

- 2. Output data 1; increment burst counter.

- 3. Output data 2; increment burst counter.

- 4. Output data 3; increment burst counter.

- 5. Output data 4; latch column address; start burst READ cycle.

- 6. Latch column address; start burst WRITE cycle; write data 1.

- 7. Increment burst counter; write data 2.

- 8. Increment burst counter; write data 3.

- 9. Increment burst counter; write data 4.

- 10. WE transitioning LOW will terminate the burst and reset the burst counter provided <sup>t</sup>TP and <sup>t</sup>BTH are satisfied. <sup>t</sup>TP is met by the READ burst being terminated by a WRITE burst. The DQs will continue to drive data out until both <sup>t</sup>BTHZ (MIN) and <sup>t</sup>WHZ (MIN) have been satisfied and will reach the High-Z state once both <sup>t</sup>BTHZ (MAX) and <sup>t</sup>WHZ (MAX) have been satisfied.

- 11. The combination of RAS and CAS HIGH close the row and place the DQ pins in the High-Z state.

- 12. CASL and CASH are shown as if they are tied together and create a single CAS. If not connected, either or both CASL and CASH may toggle during READs but they must both toggle during WRITEs to perform a WORD WRITE. If only one CAS toggles, the other CAS must be held HIGH.

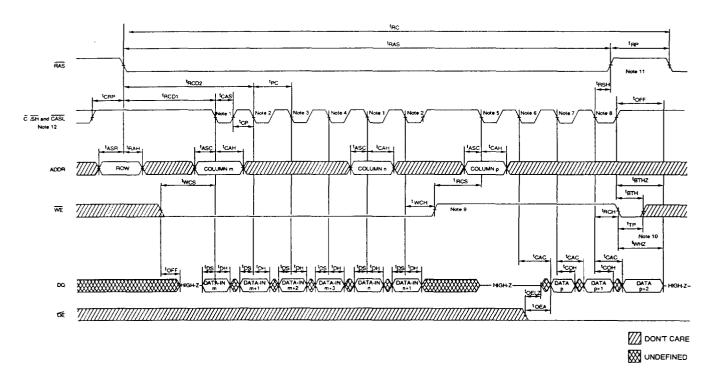

# **BURST EDO** WORD-WRITE/READ CYCLE

- NOTE: 1. Latch column address; start burst WRITE cycle; write data 1.

- 2. Increment burst counter; write data 2.

- 3. Increment burst counter; write data 3.

- 4. Increment burst counter; write data 4.

- 5. Latch column address; start burst READ cycle.

- 6. Output data 1; increment column address.

- 7. Output data 2; increment column address.

- 8. Output data 3; increment column address.

- 9. WE transitioning HIGH will terminate the burst and reset the burst counter. The tBTH time is not required as it is satisfied by <sup>t</sup>RCS; <sup>t</sup>TP is met by the WRITE burst being terminated by a READ burst.

- 10. WE transitioning LOW will terminate the burst and reset the burst counter provided TP and BTH are satisfied. The DQs will continue to drive data out until both tBTHZ (MIN) and tWHZ (MIN) have been satisfied and will reach the High-Z state once both <sup>t</sup>BTHZ (MAX) and <sup>t</sup>WHZ (MAX) have been satisfied.

- 11. The combination of RAS and CAS HIGH close the row and place the DQ pins in the High-Z state. OFF is measured from the last signal (RAS or CAS) that transitions HIGH.

- 12. CASL and CASH are shown as if they are tied together and create a single CAS. If not connected, either or both CASL and CASH may toggle during READs but they must both toggle during WRITEs to perform a WORD WRITE. If only one CAS toggles, the other CAS must be held HIGH.

# BURST EDO READ/WORD-WRITE CYCLE

\*\*NOTE: 1. CASL and CASH are shown as if they are tied together and create a single CAS. If not connected, either or both CASL and CASH may toggle during READs but they must both toggle during WRITEs to perform a WORD WRITE. If only one CAS toggles, the other CAS must be held HIGH.

# **BURST EDO** WORD-WRITE/BYTE-WRITE CYCLE

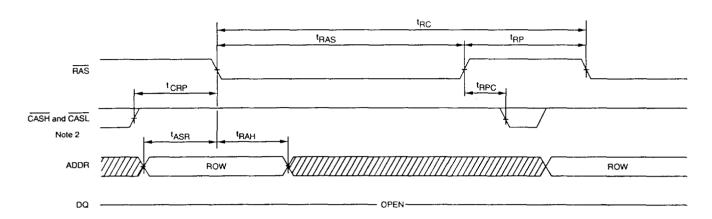

# **RAS-ONLY REFRESH CYCLE**

# **CBR REFRESH CYCLE**

#### MOLE

- CBR REFRESH is recommended for all new designs to insure compatibility with future generation DRAMs.

Micron and JEDEC recommend CBR REFRESH as the preferred method of refresh for the 64 Meg DRAM generation and beyond.

- 2. CASL and CASH are shown as if they are tied together and create a single CAS. If not connected, either or both CASL and CASH may toggle. If only one CAS toggles, the other CAS must be held HIGH.

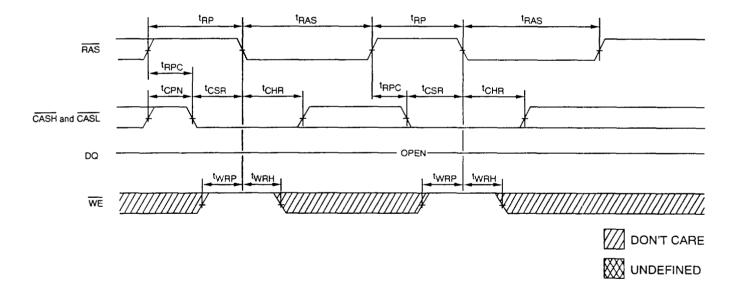

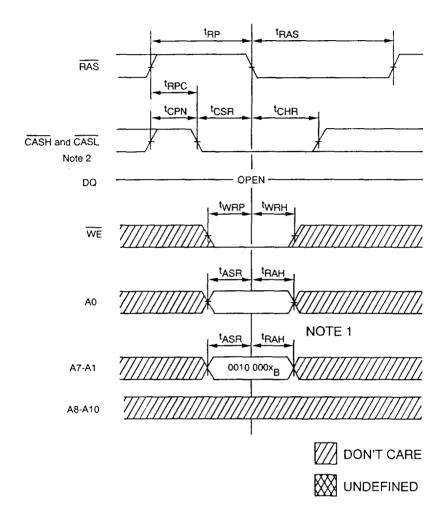

## WCBR PROGRAM CYCLE

#### 10TE:

- 1. A0 LOW sets the burst sequence to linear bursts. A0 HIGH sets the burst sequence to interleave bursts. Addresses A8 through A10 are "don't cares." Addresses A7-A10 should contain the state of (0010 000x<sub>B</sub> where x=A0) to ensure future compatability. The burst sequence will remain set until the device power is interrupted or another WCBR cycle is executed.

- 2. A RAS-ONLY or CBR REFRESH cycle must be executed after the WCBR cycle to exit the programming mode.

- 3. CASL and CASH are shown as if they are tied together and create a single CAS. If not connected, either or both CASL and CASH may toggle. If only one CAS toggles, the other CAS must be held HIGH.