### **FEATURES**

- Small 8 Pin SOIC/DIP package

- Synthesizes 4 programmable frequencies from 2MHz to 120MHz

- Supports 3.3V and 5.0V operation

- Smooth, glitch-free frequency transitions

- Advanced PLL design with low phase jitter

- Reference and synthesized clocks

- High performance, low power CMOS design with on chip loop filter

- TTL or CMOS input level compatible

- Ideal replacement for crystal oscillators

- W42C07A-01 is pin and functional compatible with AV9107-05

### **FUNCTIONAL DESCRIPTION**

The **w**42C07A is a solution for generating two simultaneous clocks while using minimum board space. One clock (REFCLK) is a fixed output frequency which is the same as the input reference crystal (or clock). The other clock (CPUCLK) can vary between 2 and 120MHz with up to 4 selectable programmed frequencies stored in internal ROM.

Included in the **W**42C07A's advanced feature set is an on-chip loop filter, providing jitter free operation with only two decoupling capacitors. The **W**42C07A offers smooth and glitch-free transitions when switching from one frequency to another. This feature can be utilized in power management systems such as "green" PCs, notebooks and palmtop computers where it is frequently necessary to slow down the clock to preserve power. The device is designed to be compatible with the Intel cycle to cycle timing specifications for the 80486 processors.

The **w**42C07A (see Table 1) is an ideal solution for replacing high speed oscillators in computers for CPU clock generation.

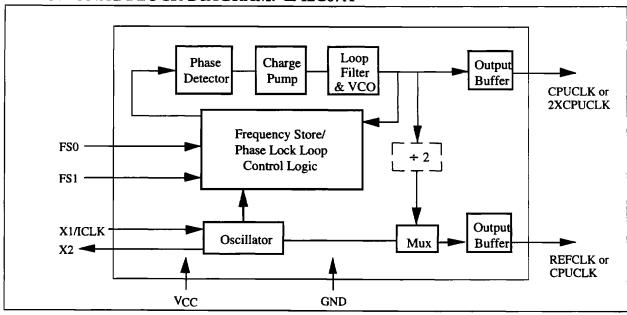

### FUNCTIONAL BLOCK DIAGRAM: W42C07A

### PIN DESCRIPTIONS

|          | Input/ | <del>-</del>                                                     |

|----------|--------|------------------------------------------------------------------|

| Pin Name | Output | Pin Description                                                  |

| 2XCPUCLK | 0      | Clock output (refer to Frequency Selection Table)                |

| CPUCLK   | 0      | Clock output (refer to Frequency Selection Table)                |

| FS0      | I      | Frequency selection input, LSB (Note 1)                          |

| FS1      | I      | Frequency selection input (Note 1)                               |

| GND      | -      | Ground connection                                                |

| REFCLK   | 0      | Reference Clock output, outputs crystal or input clock frequency |

| VCC      | -      | Power Supply connection                                          |

| X1/ICLK  | I      | Crystal connection or external clock frequency input             |

| X2       | 0      | Crystal connection. leave unconnected when using external clock  |

**Note 1:** All inputs, except for X1/ICLK, have an internal pull up resistor. Unconnected inputs will assume a logic high condition.

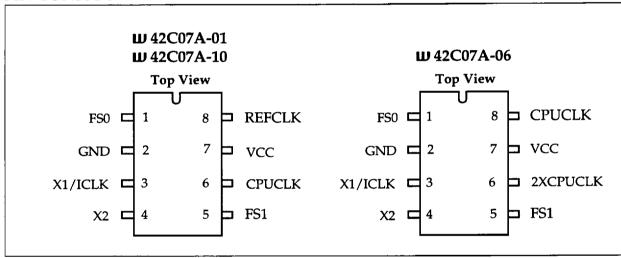

# PIN CONFIGURATIONS

FREQUENCY SELECTION FOR w42C07A (using 14.318MHz input; 3.3V and 5.0V)

| IC WORKS<br>Part Number | <b>W42</b> C07A-01 | Ш42С                     | <b>W</b> 42C07A-10 |                 |  |

|-------------------------|--------------------|--------------------------|--------------------|-----------------|--|

| Cross Reference         | AV9107-05          | N                        | N/A                |                 |  |

| FS1, FS0                | CPUCLK<br>(MHz)    | CPUCLK 2XCPUCLK (MHz)    |                    | CPUCLK<br>(MHz) |  |

| 00                      | 40                 | 25                       | 50                 | 25              |  |

| 01                      | 50                 | 33.3                     | 66.6               | 33.3            |  |

| 10                      | 66.6               | 40                       | 80                 | 40              |  |

| 11                      | 80                 | 50 (Note 2) 100 (Note 2) |                    | 50              |  |

| REFCLK                  | 14.318             | N                        | 14.318             |                 |  |

Note 2: Not guaranteed when Vcc < 4.5V.

**ABSOLUTE MAXIMUM RATINGS** (Note 1)

| Parameter                                 | Symbol           | Rating      | Unit |

|-------------------------------------------|------------------|-------------|------|

| Voltage on Any Pin with Respect to Ground | VCC,VIN          | -0.5 to 7.0 | V    |

| Storage Temperature                       | T <sub>STG</sub> | -65 to +150 | °C   |

| Ambient Temperature Under Bias            | TB               | -55 to +125 | °C   |

| Operating Temperature                     | $T_A$            | 0 to +70    | °C_  |

**Note 1:** Stresses greater than those listed in this table may cause permanent damage to the device. These represent a stress rating only. Operation of the device at these or any other conditions above those specified in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **ELECTRICAL CHARACTERISTICS AT 5V**

DC ELECTRICAL CHARACTERISTICS (0°C  $\leq$  T<sub>A</sub>  $\leq$  70°C, V<sub>CC</sub> = 5V  $\pm$  10 %) (Note 2)

| Parameter              | Symbol          | Test Conditions                  | Min | Тур  | Max | Unit |

|------------------------|-----------------|----------------------------------|-----|------|-----|------|

| Supply Current         | I <sub>CC</sub> | Note 2                           |     | 10   | 20  | mA   |

| Input Low Voltage      | $ V_{IL} $      | $V_{CC} = 5V$                    |     |      | 0.8 | V    |

| Input High Voltage     | $v_{IH}$        | $V_{CC} = 5V$                    | 2.0 |      |     | V    |

| Output Low Voltage     | VOL             | $I_{OL} = 8 \text{ mA}$          |     |      | 0.4 | V    |

| Output High Voltage    | VOH             | $I_{OH} = -4 \text{ mA}$         | 2.4 |      |     | V    |

| Output Freq. Change    | FD              | Over supply and temperature      |     | .002 | .01 | %    |

| Input Capacitance      | CI              | Except X1, X2                    |     |      | 10  | pF   |

| Load Capacitance       | $C_{L}$         | Pins X1, X2                      |     | 20   |     | рF   |

| Input Low Current      | IIL             | VIN = 0V (includes pull-up res.) |     |      | -10 | μА   |

| Input High Current     | I <sub>IH</sub> | $V_{IN} = V_{CC}$                |     |      | 10  | μА   |

| Input Pull-Up Resistor | RP              | V <sub>IN</sub> =0V              |     | 250  |     | kΩ   |

Note 2: With no load, 14.318MHz crystal input, and CLK1 running at 40MHz. Power supply current varies with frequency and output load capacitance.

# AC CHARACTERISTICS (0°C $\leq$ T<sub>A</sub> $\leq$ 70°C, V<sub>CC</sub> = 5V $\pm$ 10 %)

| Parameter                                        | Symbol           | Min | Тур    | Max  | Unit |

|--------------------------------------------------|------------------|-----|--------|------|------|

| Enable Pulse Width                               | Tw               | 20  |        |      | ns   |

| Setup Time Data to Enable                        | Tsu              | 20  |        |      | ns   |

| Output Frequency (CPUCLK & 2XCPUCLK)             | FO               | 2   | i i    | 120  | MHz  |

| Input Frequency                                  | FI               | 2   | 14.318 | 32   | MHz  |

| Hold Time Data to Enable                         | THD              | 10  |        |      | ns   |

| Input Clock Rise Time                            | ICLKR            |     |        | 20   | ns   |

| Input Clock Fall time                            | ICLKF            |     |        | 20   | ns   |

| Output Rise Time, 0.8 to 2.0V, 25pF load         | $T_{R}$          |     | 1      | 2    | ns   |

| Rise Time, 20 to 80% V <sub>CC</sub> , 25pF load | $T_{\mathbf{R}}$ |     | 2      | 4    | ns   |

| Output Fall Time, 2.0 to 0.8V, 25pF load         | $T_{F}$          |     | 1      | 2    | ns   |

| Fall Time, 80 to 20% V <sub>CC</sub> , 25pF load | TF               |     | 2      | 4    | ns   |

| Duty Cycle, 15pF load                            | $D_{T}$          | 40  | 50/50  | 60   | %    |

| Jitter, 1 Sigma, all frequencies                 | T <sub>J1S</sub> |     | ±0.5   | ±2   | %    |

| Jitter, Absolute, all frequencies                | TJABS            |     | ±3     | ±5   | %    |

| Fequency Transition Time, 50 to 4MHz             | T <sub>FT</sub>  |     |        | 20   | ms   |

| Powerup Time, off to 100MHz                      | T <sub>PU</sub>  |     | 15     | 30   | ms   |

| Clock Skew, CPUCLK vs 2xCPUCLK (-06)             | TSK              |     | ±0.5   | ±1.0 | ns   |

# **ELECTRICAL CHARACTERISTICS AT 3.3V**

# DC ELECTRICAL CHARACTERISTICS (0°C $\leq$ T<sub>A</sub> $\leq$ 70°C, V<sub>CC</sub> = 3.3V $\pm$ 10 %) (Note 2)

| Parameter              | Symbol          | Test Conditions                    | Min    | Тур  | Max     | Unit |

|------------------------|-----------------|------------------------------------|--------|------|---------|------|

| Supply Current         | I <sub>CC</sub> | Note 2                             |        | 8    | 16      | mA   |

| Input Low Voltage      | $v_{IL}$        | VCC = 3.3V                         |        |      | 0.15Vcc | V    |

| Input High Voltage     | $v_{IH}$        | VCC = 3.3V                         | 0.7Vcc |      |         | V    |

| Output Low Voltage     | VOL             | I <sub>OL</sub> = 8 mA             |        |      | 0.4     | V    |

| Output High Voltage    | V <sub>OH</sub> | I <sub>OH</sub> = -4 mA            | 2.4    |      |         | V    |

| Output Freq. Change    | $F_{D}$         | Over supply and temperature        |        | .002 | .01     | %    |

| Input Capacitance      | CI              | Except X1, X2                      |        |      | 10      | рF   |

| Load Capacitance       | CL              | Pins X1, X2                        |        | 20   |         | рF   |

| Input Low Current      | IIL             | VIN = 0V (incl. pull-up res.)      |        |      | -10     | μA   |

| Input High Current     | I <sub>IH</sub> | V <sub>IN</sub> = V <sub>C</sub> C |        |      | 10      | μА   |

| Input Pull-Up Resistor | Rp              | VIN = 0V                           |        | 250  |         | kΩ   |

Note 2: With no load, 14.318MHz crystal input, and CLK1 running at 40MHz. Power supply current varies with frequency and output load capacitance.

# AC CHARACTERISTICS (0°C $\leq$ T<sub>A</sub> $\leq$ 70°C, V<sub>CC</sub> = 3.3V $\pm$ 10 %)

| Parameter                                        | Symbol            | Min        | Тур    | Max  | Unit |

|--------------------------------------------------|-------------------|------------|--------|------|------|

| Enable Pulse Width                               | Tw                | 20         |        |      | ns   |

| Setup Time Data to Enable                        | TSU               | 20         |        |      | ns   |

| Output Frequency (CPUCLK & 2XCPUCLK)             | FO                | 2          |        | 80   | MHz  |

| Input Frequency                                  | FI                | 2          | 14.318 | 32   | MHz  |

| Hold Time Data to Enable                         | THD               | 10         |        |      | ns   |

| Input Clock Rise Time                            | ICLKR             |            |        | 20   | ns   |

| Input Clock Fall time                            | ICLKF             |            |        | 20   | ns   |

| Rise Time, 20 to 80% V <sub>CC</sub> , 15pF load | TR                |            | 2      | 4    | ns   |

| Fall Time, 80 to 20% V <sub>CC</sub> , 15pF load | T <sub>F</sub>    |            | 2      | 4    | ns   |

| Duty Cycle, 15pF load                            | $D_{T}$           | <b>4</b> 0 | 50/50  | 60   | %    |

| Jitter, 1 Sigma, all frequencies                 | T <sub>I1S</sub>  |            | ±0.5   | ±2   | %    |

| Jitter, Absolute, all frequencies                | T <sub>IABS</sub> |            | ±3     | ±5   | %    |

| Fequency Transition Time, 50 to 4MHz             | Ť <sub>FT</sub>   |            |        | 20   | ms   |

| Powerup Time, off to 100MHz                      | T <sub>PU</sub>   | 1          | 15     | 30   | ms   |

| Clock Skew, CPUCLK vs 2xCPUCLK (-06)             | TSK               |            | ±0.5   | ±1.0 | ns   |

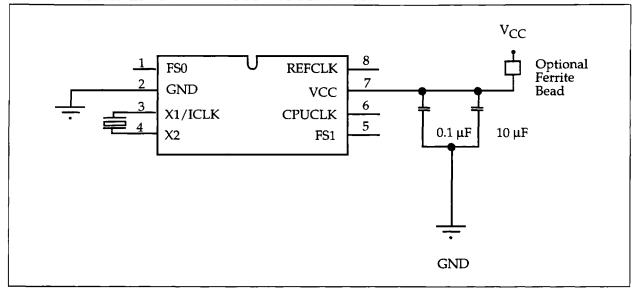

### RECOMMENDED CIRCUIT CONFIGURATION

### **W42C07A RECOMMENDED BOARD LAYOUT**

For optimum performance in system applications the above power supply decoupling scheme should be used. All GND pins are connected directly to the ground plane. All VCC connections are connected directly to the power plane.

VCC decoupling is important to both reduce phase jitter and EMI radiation. The 0.1µf decoupling capacitor should be placed as close to its VCC pin as possible, otherwise the increased trace inductance will negate its decoupling capability. The 10µf decoupling capacitor shown should be a tantalum type. For further EMI protection, the VCC connection can be made via a ferrite bead, as shown above.

An isolated ground plane should not be used, even though this is a common recommendation. An isolated ground plane only works well when the clock source and load share the same isolated ground area. Ground plane isolation will only cause increased EMI, ground bounce, and in many cases increased output clock jitter.

When using the  $\mathbf{W}42\text{C}07\text{A}$ , unused input select pins can be left floating since internal pull-up resistors are incorporated (hence a floating input will assume a logic 1 condition). Output clocks should utilize a series termination resistor (about 33 $\Omega$ ) placed as close to the clock outputs as possible; this will also help to decrease jitter and EMI.

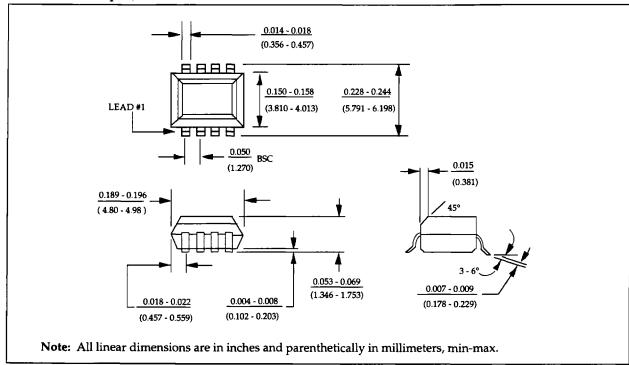

# **PACKAGING INFORMATION**

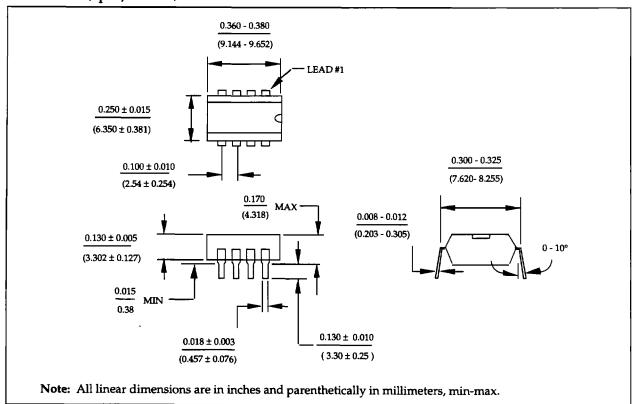

# Plastic SOIC (8pin, 150mil)

# Plastic DIP (8pin, 300mil)

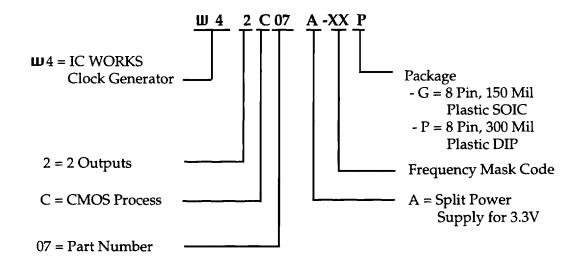

### ORDERING INFORMATION

#### **VALID PART NUMBERS**

**w**42C07A-01G **w**42C07A-01P

**w**42C07A-06G

**W42C07A-06P**

**w**42C07A-10G **w**42C07A-10P

IC WORKS, Inc. 3725 N. First Street San Jose, CA 95134-1700 Tel: (408) 922-0202

Fax: (408) 922-0833

IC WORKS, Inc. reserves the right to amend or discontinue this product without notice. Circuit and timing diagrams used to describe IC WORKS product operations and applications are included as a means of illustrating a typical product application. Complete information for design purposes is not necessarily given. This information has been carefully checked and is believed to be entirely reliable. IC WORKS, however, will not assume any responsibility for inaccuracies.

#### LIFE SUPPORT APPLICATIONS:

IC WORKS products are not designed for use in life support applications, devices, or systems where malfunctions of the IC WORKS product can reasonably be expected to result in personal injury. IC WORKS customers using or selling IC WORKS products for use in such applications do so at their own risk and agree to fully indemnify IC WORKS for any damages resulting in such improper use or sale.

Document No. 42C07A/00/0494