# Am2927/Am2928

Quad Three-State Bus Transceivers With Clock Enable

#### DISTINCTIVE CHARACTERISTICS

- Three-state bus driver outputs can sink 48mA, and Three-state receiver outputs sink 24mA — both at 0.5V max.

- D-type register on drivers

- Latch output on Am2927; Registered output on Am2928

- Output data to input wrap around gating; Input register to output transfer gating with or without driving data bus

- Clock enabled registers

- 3.0V minimum V<sub>OH</sub> for direct interface to MOS microprocessors

#### **GENERAL DESCRIPTION**

The Am2927 and Am2928 are high-performance, low-power Schottky, quad bus transceivers intended for use in bipolar or MOS microprocessor system applications.

Both devices feature register enable lines which function as clock enables without introducing gate delay in the clock inputs. The four transceivers share common enables, clock, select and three-state control lines.

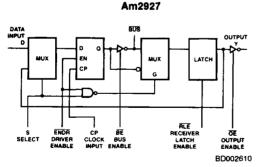

The Am2927 consists of four D-type edge-triggered flip-flops. Each flip-flop output is connected to a three-state data bus driver and separately to the input of a corresponding receiver latch input. The receiver latch can select input from the driver or the data bus. The select line determines the source of input data for the bus driver choosing between input data or data recirculated from the receiver output. The receiver output also has a three-state output buffer.

The combination of the select input, S, the driver input enable, ENDR, and the receiver latch enable, RLE, provide seven different data path operating modes not available in

other transceivers. For example, transmitted data can be stored in the receiver for subsequent retransmission. Also, received data can be output to the system and simultaneously fed back to the driver input.

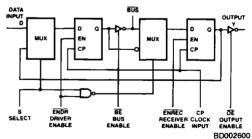

The Am2928 is similar to the Am2927, but with a D-type edge-triggered register in the receiver and a receiver enable, ENREC, which functions as a common clock enable.

Data from each D input is inverted at the bus output. Likewise, data at the bus input is inverted at the receiver output.

All three-state controls and enable lines are active low (the Am2927 receiver latch is transparent when RLE is LOW). The select input, S, determines whether the enabled driver input accepts data from the data input, D, or from the corresponding receiver output, Y. Similarly, the select line determines whether the receiver accepts input data from the data bus, or the driver output.

#### **BLOCK DIAGRAM**

Am2928

01032B

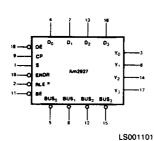

# CONNECTION DIAGRAM Top View

D-20-1

Voc BIRGR OE V<sub>3</sub> D<sub>3</sub> BIRG, V<sub>2</sub> D<sub>4</sub> BIRG, BE

20 19 16 17 16 18 16 12 12 11

1 2 3 4 5 8 7 8 9 10

1 3 4 5 8 7 8 9 10

2 \*\*NEE V<sub>2</sub> D<sub>3</sub> BIRG, V<sub>4</sub> D<sub>4</sub> BIRG, O GNO

CD004831

-RIE 5 5 22 C NC

R<sub>0</sub> 5 24 C R<sub>2</sub>

R<sub>1</sub> 7 22 C NC

R<sub>1</sub> 8 22 C NC

R<sub>2</sub> 8 22 C NC

R<sub>3</sub> 8 22 C NC

R<sub>4</sub> 9 22 C NC

R<sub>5</sub> 8 22 C NC

R<sub></sub>

L-28-1

Note: Pin 1 is marked for orientation \*ENREC for Am2928

# LOGIC SYMBOL

\*ENREC for Am2928

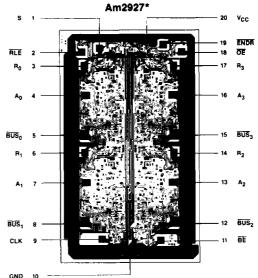

# METALLIZATION AND PAD LAYOUT

DIE SIZE 0.087" x 0.144"

NOTE: The Am2928 is similar to the

Am2927, but with a D-type edge-triggered

register in the receiver and a receiver enable, ENREC, which functions as a common

clock enable.

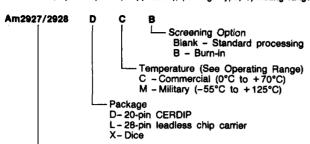

#### ORDERING INFORMATION

AMD products are available in several packages and operating ranges. The order number is formed by a combination of the following: Device number, speed option (if applicable), package type, operating range and screening option (if desired).

Device type Quad 3-state Bus Transceivers

| Valid Combinations |                                         |  |  |  |

|--------------------|-----------------------------------------|--|--|--|

| Am2927<br>Am2928   | DC, DM<br>LC, LCB, LM,<br>LMB<br>XC, XM |  |  |  |

#### **Valid Combinations**

Consult the AMD sales office in your area to determine if a device is currently available in the combination you wish.

# PIN DESCRIPTION

| Pin No.         | Name                                                                               | 1/0 | Description                                                                                                                                                                                   |

|-----------------|------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9               | СР                                                                                 | 1   | Clock Pulse to internal registers enters data on the LOW-to-HIGH transition.                                                                                                                  |

| 11              | BE                                                                                 | 1   | Bus Enable. When Bus Enable is LOW the four drivers drive the BUS outputs.                                                                                                                    |

| 5, 8,<br>12, 15 | BUS <sub>0</sub> .<br>BUS <sub>1</sub> .<br>BUS <sub>2</sub> ,<br>BUS <sub>3</sub> | 1/0 | The four driver outputs and receiver inputs.                                                                                                                                                  |

| 4, 7,<br>13, 16 | D <sub>0</sub> , D <sub>1</sub> ,<br>D <sub>2</sub> , D <sub>3</sub>               | 1   | The four driver data inputs inverting from D to BUS.                                                                                                                                          |

| 3, 6,<br>14, 17 | Y <sub>0</sub> , Y <sub>1</sub> ,<br>Y <sub>2</sub> , Y <sub>3</sub> ,             | 0   | The four receiver data outputs inverting from BUS to Y.                                                                                                                                       |

| 1               | s                                                                                  | 1   | Select input controls data path modes in conjunction with ENDR and RLE (or ENREC).                                                                                                            |

| 18              | ŌĒ                                                                                 | 1   | Output Enable. When Output Enable is LOW the four receiver outputs Y are active.                                                                                                              |

| 19              | ENDR                                                                               | ١   | Driver Enable. Common clock enable for the input register. Allows the data on the D inputs to be loaded into the driver register on the clock LOW-to-High transition.                         |

| 2               | RLE                                                                                | ŀ   | Receiver Latch Enable (Am2927 only). When Receiver Latch Enable is LOW, the four receiver latches are transparent. The latches hold received data when RLE is HIGH.                           |

| 2               | ENREC                                                                              | ŀ   | Receiver Enable (Am2928 only). Common clock enable for the receiver register. Allows the BUS driver or previous receiver data to enter the receiver register on the rising edge of the clock. |

# **Am2927 FUNCTION TABLES**

#### **Driver Register Control**

| ENDR | S | RLE | Driver Register            |

|------|---|-----|----------------------------|

| Н    | × | X   | Hold Previous Data         |

| L    | L | ×   | Load from D Input          |

| L    | Н | L   | Load from BUS              |

| L    | Н | Н   | Load Latched Receiver Data |

# Receiver Latch Control

| ENDR | S | ALE | Receiver Output                                        |  |  |  |  |  |

|------|---|-----|--------------------------------------------------------|--|--|--|--|--|

| х    | х | н   | Data Latched                                           |  |  |  |  |  |

| н    | н | Ļ   | Driver Register Output at Y output (Latch Transparent) |  |  |  |  |  |

| ×    | L | L   | Bus Data at Y Output                                   |  |  |  |  |  |

| L    | х | L   | (Latch Transparent)                                    |  |  |  |  |  |

#### **Am2928 FUNCTION TABLES**

#### **Driver Register Control**

| ENDR | S | Driver Register             |

|------|---|-----------------------------|

| Н    | Х | Hold Previous Data          |

| L    | L | Load from D input           |

| L    | н | Load from Receiver Register |

### Receiver Register Control

| ENDR | S | ENREC | Receiver Output           |  |  |  |  |

|------|---|-------|---------------------------|--|--|--|--|

| х    | Х | Н     | Hold Previous Data        |  |  |  |  |

| н    | Н | L     | Load from Driver Register |  |  |  |  |

| ×    | L | L     | Load from BUS             |  |  |  |  |

| L X  |   | , L   | Load IIOIII BOS           |  |  |  |  |

# Am2927 AND Am2928 FUNCTION TABLE

| Driver Input | Receiver Input | Cont | rol Input Con | dition |               |    |

|--------------|----------------|------|---------------|--------|---------------|----|

| From         | From           | s    | S ENDR +      |        | Signal Flow   | BE |

| D            | BUS            | L    | L             | L      | BUS<br>-D -R- | н  |

| Input        | (No Load)      | L    | L             | н      | -D-A-         | L  |

| _            | BUS            | н    | L             | L      |               | н  |

| Receiver     | (No Load)      | н    | L             | н      |               | L  |

|              | BUS            | L    | н             | L      | D L-R-        | н  |

| (No Load)    | Driver         | н    | н             | Ļ      | D1-R-         | х  |

|              | (No Load)      | х    | н             | н      | O A           | L  |

\*RLE for Am2917 (asynchronous) or ENREC for Am2928 ( 」).

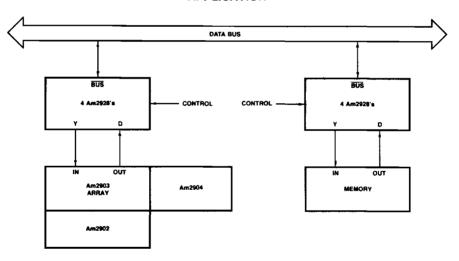

# **APPLICATION**

AF001800

The Am2927 and Am2928 can be used to provide Data Bus, Address Bus and Control Bus Interface in a high-speed bipolar microprocessor system.

#### ABSOLUTE MAXIMUM RATINGS

| Storage Temperature65°C to +150°C                                               |

|---------------------------------------------------------------------------------|

| Ambient Temperature Under Bias55°C to +125°C Supply Voltage to Ground Potential |

| Continuous0.5V to +7.0V                                                         |

| DC Voltage Applied to Outputs For                                               |

| High Output State0.5V to +VCC max                                               |

| DC Output Current, Into Bus100mA                                                |

| DC Output Current, Into Outputs                                                 |

|                                                                                 |

| (Except Bus) 30mA                                                               |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

| Commercial (C) Devices           |                   |

|----------------------------------|-------------------|

| Temperature                      | 0°C to +70°C      |

| Supply Voltage                   | + 4.75V to +5.25V |

| Military (M) Devices             |                   |

| Temperature                      | 55°C to +125°C    |

| Supply Voltage                   | +4.5V to +5.5\    |

| Operating ranges define those li |                   |

# DC CHARACTERISTICS over operating range unless otherwise specified

| Parameters      | Description                     | Test Conditions (Note 1)                                                      |                               |     | Typ<br>(Note 2) | Max  | Units  |

|-----------------|---------------------------------|-------------------------------------------------------------------------------|-------------------------------|-----|-----------------|------|--------|

|                 |                                 | V <sub>CC</sub> = MIN                                                         | MIL, I <sub>OH</sub> = -2.0mA | 2.4 | 3.4             |      |        |

| VOH             | Receiver Output HIGH<br>Voltage | VIN = VIH or VIL                                                              | COM'L, IOH = -6.5mA           | 2.4 | 3.4             |      | Voits  |

|                 |                                 | V <sub>CC</sub> = 5.0V                                                        | $I_{OH} = -100\mu A$          | 3.0 |                 |      |        |

| VOL             | Output LOW Voltage              | V <sub>CC</sub> = MIN<br>V <sub>IN</sub> = V <sub>IL</sub> or V <sub>IH</sub> | I <sub>OL</sub> = 24mA        |     |                 | 0.5  | Voits  |

| V <sub>IH</sub> | Input HIGH Level                | Guaranteed input<br>HIGH voltage for                                          |                               | 2.0 |                 |      | Volts  |

| \/u             | Input LOW Level                 |                                                                               | Guaranteed input logical      |     |                 | 0.8  | Volts  |

| V <sub>IL</sub> | Input LOW Level                 | LOW voltage for all imputs COM'L                                              |                               |     |                 | 0.8  | V 0113 |

| Vi              | Input Clamp Voltage             | VCC *MIN IM                                                                   | - felmA                       |     |                 | -1.2 | Volts  |

| I               | Input LOW Current               | V <sub>CC</sub> = MAX                                                         | S, ENDR                       |     |                 | -2.8 | mA     |

| IIL             |                                 | V <sub>IN</sub> = 0.4V                                                        | All other inputs              |     |                 | -1.4 | 111/4  |

| 1               | Input HIGH Current              | V <sub>CC</sub> = MAX                                                         | S, ENDR                       |     |                 | 100  | μA     |

| <sup>1</sup> ІН | Input HIGH Current              | V <sub>IN</sub> = 2.7V                                                        | All other inputs              |     |                 | 50   | μ      |

| l <sub>l</sub>  | Input HIGH Current              | V <sub>CC</sub> = MAX, V <sub>IN</sub> =                                      | 5.5V                          |     |                 | 1.0  | mA     |

| lozh            | Off-State Output Current        | V <sub>CC</sub> = MAX                                                         | V <sub>O</sub> = 2.4V         |     |                 | 100  | μΑ     |

| lozL            | (Receiver Output)               | ACC - WAX                                                                     | V <sub>O</sub> = 0.5V         |     |                 | -50  | μΛ     |

| lsc             | Output Short Circuit Current    | V <sub>CC</sub> = MAX                                                         | Receiver                      | -40 |                 | -100 | mA     |

|                 | B C                             | V MAY                                                                         | Am2927                        |     | 150             | 185  | mA     |

| loc             | Power Supply Current            | VCC = MAX                                                                     | V <sub>CC</sub> = MAX Am2928  |     | 153             | 190  | 1111/4 |

For conditions shown as MIN or MAX, use the appropriate value specified under Operating Ranges for the applicable device type.

Typical limits are at V<sub>CC</sub> = 5.0V, 25°C amblent and maximum loading.

Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

This parameter is typical of device characterization data and is not tested in production.

# BUS INPUT/OUTPUT CHARACTERISTICS over operating temperature range

|                 |                                |                                             | 368                    |              |               |

|-----------------|--------------------------------|---------------------------------------------|------------------------|--------------|---------------|

| Parameters      | Description                    | Test Conditions (Note                       | 1)                     | Typ<br>ote 2 | ax Units      |

| VOL             | Bus Output LOW Voltage         | V <sub>CC</sub> = MIN                       |                        |              | .5 Volts      |

| V <sub>OH</sub> | Bus Output HIGH Voltage        | Vcc* Mil. 10.                               | 20mA 2.4<br>- 15mA 2.4 |              | Volts         |

| VIH             | Receiver Input HIGH Total Id   | Bus Embler 2.                               | 2.0                    |              | Volts         |

| VIL             | Receiver Inputs SW reshalf     | Bus Entitle = 2.4V                          |                        | 0            | .8 Volts      |

| OFF             | Bus Lea e Cu nt Wer Off)       | 0V. V <sub>O</sub> = 4.5V                   |                        | 11           | 00 дА         |

| lozu            | Sus Bala Conta                 | V <sub>CC</sub> = MAX V <sub>O</sub> = 0.4V |                        |              | 1.4 <u>mA</u> |

| lozh            | ped (ce)                       | BUS Enable = 2.4V V <sub>O</sub> = 2.5V     |                        | 10           | 00 μΑ         |

| lsc .           | s Output Short Circuit Current | V <sub>CC</sub> = MAX, V <sub>C</sub> = 0V  | -50                    | -2           | 255 mA        |

| Cs              | Eas Capacitance (Note 4)       | V <sub>CC</sub> = 0V                        |                        | 8            | ρF            |

Notes: 1. For conditions shown as MIN or MAX, use the appropriate value specified under Operating Ranges for the applicable device type. 2. Typical limits are at V<sub>CC</sub> = 5.0V, 25°C ambient and maximum loading.

3. Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

4. This parameter is typical of device characterization data and is not tested in production.

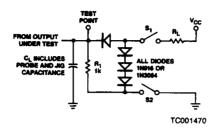

# SWITCHING TEST CIRCUIT

Note: For standard totem-pole outputs, remove R1; S1 and S2 closed.

#### SWITCHING CHARACTERISTICS over operating range unless otherwise specified Am2927

|                  |                                        |                                                                                         | co  | MMERC | IAL  |        | MLITAR | Y     |       |  |

|------------------|----------------------------------------|-----------------------------------------------------------------------------------------|-----|-------|------|--------|--------|-------|-------|--|

|                  |                                        |                                                                                         |     | Am292 | 7    | Am2927 |        |       |       |  |

| Parameters       | Description                            | Test Conditions<br>(Note 2)                                                             | Min | Тур   | Max  | Min    | Тур    | Max   | Units |  |

| t <sub>PLH</sub> | Driver Clock, CP, to BUS               |                                                                                         |     | 18    | 26   |        | 18     | 23    |       |  |

| t <sub>PHL</sub> | Diver Clock, CF, to BOS                | C <sub>L</sub> (BUS) = 50pF<br>R <sub>L</sub> (BUS) = 130Ω                              |     | 18    | 26   |        | 18     | 23    | กร    |  |

| tzh • tzl        | Bus Enable, BE, to BUS                 |                                                                                         |     | 14    | 26   | •      | 1      | 23    |       |  |

| tHZ · tLZ        | Bus Chable, BE, to BUS                 | $R_L = 130\Omega$ , $C_L = 5pF$                                                         |     | 12    | 18/3 | A      | V      | 16/23 | ns    |  |

| t <sub>PW</sub>  | Min Clock Pulse Width (HIGH or LOW)    |                                                                                         | 18  |       |      |        |        |       | ns    |  |

| t <sub>PLH</sub> | BUS to Receiver Output (Latch Enabled) | C <sub>L</sub> = 5<br>C <sub>L</sub> = 27<br>C <sub>L</sub> = 1F; M <sub>L</sub> = 270Ω | 4   |       | 23   |        | 16     | 20    | ns    |  |

| tpHL             |                                        |                                                                                         |     |       | 200  |        | 16     | 20    |       |  |

| tpLH             | Latch Enable, RLE, to Receiver Output  |                                                                                         |     |       | 26   |        | 18     | 23    |       |  |

| tpHL             | Later Enable, ACE, to Receive Output   |                                                                                         | *** |       | 26   |        | 18     | 23    | ns    |  |

| tzh • tzl        | Output Enable, OE, to Receiver But     |                                                                                         |     |       | 23   |        |        | 21    | ns    |  |

| tHZ • tLZ        | Output Eliable, OE, ID Receive Dip     |                                                                                         |     |       | 21   |        | 14     | 18    |       |  |

| t <sub>s</sub>   | Driver Enc., E. R. Clock               |                                                                                         | 10  |       |      | 9      |        |       |       |  |

| th               | Dilver Ellis, E. A., Cit               |                                                                                         | 3   |       |      | 3      |        |       | ns    |  |

| ts               | Section (ALE - HIGH)                   |                                                                                         | 18  |       |      | 15     |        |       |       |  |

| th               | See The City And Principle             |                                                                                         | 3   |       |      | 2      |        |       | ns    |  |

| tpLH             | Select S, to Receiver Output           | C <sub>L</sub> = 50pF                                                                   |     |       | 26   |        |        | 23    |       |  |

| t <sub>PHL</sub> | Select S, to neceiver Output           | R <sub>L</sub> = 270Ω                                                                   |     |       | 35   |        |        | 30    | ns    |  |

| t <sub>s</sub>   | Data inputs D, to Clock                |                                                                                         | 9   |       |      | 7      |        |       | ne    |  |

| th               | Data Inputs D, to Olock                |                                                                                         | 5   |       |      | 4      |        |       | ns    |  |

| ts               | BUS to Latch Enable, RLE               |                                                                                         | 11  |       |      | 10     |        |       |       |  |

| th               | DOG TO LATON ENABLE, FILE              |                                                                                         | 4   |       |      | 3      |        |       | ns    |  |

Notes:

1. Typical limits are at V<sub>CC</sub> = 5.0V, 25°C ambient and maximum loading.

2. For conditions shown as MIN or MAX, use the appropriate value specified under Operating Ranges for the applicable device type.

3. Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

# SWITCHING CHARACTERISTICS over operating range unless otherwise specified Am2928

|                  |                                                                           |                                                                    | COMMERCIAL<br>Am2928 |    |    | MILITARY<br>Am2928 |   |       |      |

|------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------|----|----|--------------------|---|-------|------|

|                  |                                                                           |                                                                    |                      |    |    |                    |   |       |      |

| t <sub>PLH</sub> | Driver Clock, CP, to BUS                                                  | C <sub>L</sub> (BUS) = 50pF                                        |                      | 18 | 23 |                    |   | 26    | ns   |

| t <sub>PHL</sub> |                                                                           | R <sub>L</sub> (BUS) = 130Ω                                        |                      | 18 | 23 |                    |   | 26    |      |

| tzH • tzL        | Bus Enable, BE, to BUS                                                    |                                                                    |                      | 14 | 23 | Ń                  | - | 26    | ns   |

| tHZ • tLZ        |                                                                           | R <sub>L</sub> = 130Ω, C <sub>L</sub> = 5pF                        | 1                    | 12 | 23 |                    |   | 18/30 |      |

| <sup>t</sup> PLH | Clock, CP, to Receiver Output                                             | C <sub>L</sub> = 50pp<br>R <sub>L</sub> = 50 R <sub>L</sub> = 270Ω | f                    |    | 28 |                    |   | 26    | ns   |

| t <sub>PHL</sub> |                                                                           |                                                                    | 7.4                  |    | 23 |                    |   | 26    |      |

| tpw              | Min Clock Pulse Width (HIGH or LOW)                                       |                                                                    | 5                    |    |    | 18                 | I |       | ns   |

| tzh • tzL        | Output Enable, OE, to Receive Duty                                        |                                                                    | -                    | 14 | 21 |                    |   | 23    | ns   |

| tHZ • tLZ        |                                                                           |                                                                    |                      | 21 | 18 |                    |   | 26    |      |

| ts               | Driver End 7, Et IR, Classification of the BUL Selbck (Receiver Register) |                                                                    | 9                    |    |    | 10                 |   |       | - ns |

| th               |                                                                           |                                                                    | 3                    |    |    | 3                  |   |       |      |

| ts               |                                                                           |                                                                    | 7                    |    |    | 8                  |   |       |      |

| th               |                                                                           |                                                                    | 4                    |    |    | 5                  |   |       |      |

| t <sub>s</sub>   | - Receiver Enable, ENMREC, to Clock                                       |                                                                    | 8 10                 | 10 |    |                    | J |       |      |

| th               |                                                                           |                                                                    | 4                    |    |    | 5                  |   |       | ns   |

| ts               | S to Clock                                                                | ]                                                                  | 10                   |    |    | 12                 |   |       | ns   |

| th               |                                                                           | 1 5                                                                | 4                    |    |    | 5                  |   |       |      |

| ts               | Data Inputs, D, to Clock<br>(Driver Register)                             |                                                                    | 7                    |    |    | 9                  |   |       | ns   |

| th               |                                                                           |                                                                    | 4                    |    |    | 5                  |   |       |      |

Notes: 1. Typical limits are at V<sub>CC</sub> = 5.0V, 25°C ambient and maximum loading.

2. For conditions shown as MIN or MAX, use the appropriate value specified under Operating Ranges for the applicable device type.

3. Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.