#### **ADVANCE INFORMATION**

# 74LVT543 3.3V ABT Octal Registered Transceiver with TRI-STATE® Outputs

#### **General Description**

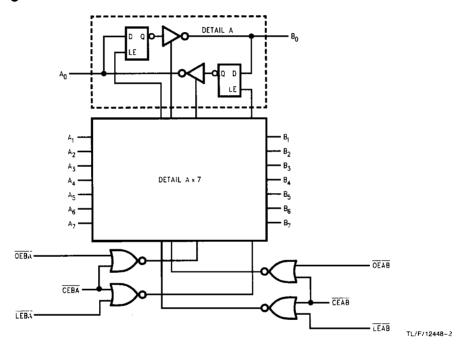

The 'LVT543 octal transceiver contains two sets of D-type latches for temporary storage of data flowing in either direction. Separate Latch Enable and Output Enable inputs are provided for each register to permit independent control of inputting and outputting in either direction of data flow.

These octal registered transceivers is/are designed for low-voltage (3.3V)  $V_{CC}$  applications, but with the capability to provide a TTL interface to a 5V environment. The LVT543 is fabricated with an advanced BiCMOS technology to achieve high speed operation similar to 5V ABT while maintaining a low power dissipation.

#### **Features**

- Input and output interface capability to systems at 5V VCC

- Bus-Hold data inputs eliminate the need for external pull-up resistors to hold unused inputs

Live insertion/extraction permitted

- Power Up/Down high impedance provides glitch-free bus loading

- Outputs source/sink -32 mA/+64 mA

- Available in SOIC JEDEC and TSSOP

- Functionally compatible with the 74 series 543

- Latch-up performance exceeds 500 mA

#### **Pin Descriptions**

| Pin Names                      | Description          |  |

|--------------------------------|----------------------|--|

| OEAB, OEBA                     | Output Enable Inputs |  |

| LEAB, LEBA                     | Latch Enable Inputs  |  |

| CEAB, CEBA                     | Chip Enable Inputs   |  |

| $A_0-A_7$                      | Side A Inputs or     |  |

| •                              | TRI-STATE Outputs    |  |

| B <sub>0</sub> -B <sub>7</sub> | Side B Inputs or     |  |

| • .                            | TRI-STATE Outputs    |  |

|                                |                      |  |

## **Connection Diagram**

## Pin Assignment for SOIC, SSOP II and TSSOP

| LEBA -           | 1        | 24    | - ',cc                     |

|------------------|----------|-------|----------------------------|

| OEB4 -           | ž        | 23    | — JEBA                     |

| 4 <sub>0</sub> — | 3        | 22    | — 3 <sub>0</sub>           |

| A <sub>1</sub> — | 4        | 21    | <del>-</del> 3.            |

| A2               | 5        | 20    | - 32                       |

| A3               | 6        | 19    | <b></b> 3₃                 |

| A4               | 7        | 18    | 3₄                         |

| A <sub>5</sub>   | 8        | 17    | <del></del> ∃ <sub>5</sub> |

| A <sub>6</sub>   | 9        | 16    | ŝ <sub>6</sub>             |

| 4, -             | 10       | 15    | <b>—</b> ∋,                |

| CEAB             | 1.1      | 1.4   | - LEAB                     |

| GND -            | 12       | 13    | - OEAB                     |

|                  | <u> </u> | <br>_ |                            |

TL/F/12448-1

|                          | SOIC JEDEC                | TSSOP                       | SSOP II                     |

|--------------------------|---------------------------|-----------------------------|-----------------------------|

| Order Number             | 74LVT543WM<br>74LVT543WMX | 74LVT543MTC<br>74LVT543MTCX | 74LTV543MSA<br>74LTV543MSAX |

| See NS Package<br>Number | M24B                      | MTC24                       | MSA24                       |

#### **Functional Description**

The 'LVT543 contains two sets of D-type latches, with separate input and output controls for each. For data flow from A to B, for example, the A to B Enable (ČEĀB) input must be low in order to enter data from the A port or take data from the B port as indicated in the Data I/O Control Table. With ČEĀB low, a low signal on (LĒĀB) input makes the A to B latches transparent; a subsequent low to high transition of the LĒĀB line puts the A latches in the storage mode and their outputs no longer change with the A inputs. With ČĒĀB and ŌĒĀB both low, the B output buffers are active and reflect the data present on the output of the A latches. Control of data flow from B to A is similar, but using the ČĒBĀ, LĒBĀ and ŌĒBĀ.

#### Data I/O Control Table

|      | Inputs | nputs Lateb Status Output Buffer |              | Output Buffers |

|------|--------|----------------------------------|--------------|----------------|

| CEAB | LEAB   | OEAB                             | Latch Status | Output Buffers |

| Н    | X      | X                                | Latched      | High Z         |

| х    | Н      | Х                                | Latched      | _              |

| L    | L      | X                                | Transparent  | _              |

| X    | X      | H                                |              | High Z         |

| L    | X      | L                                |              | Driving        |

- H = High Voltage Level

- L = Low Voltage Level

- X = Immaterial

## **Logic Diagram**