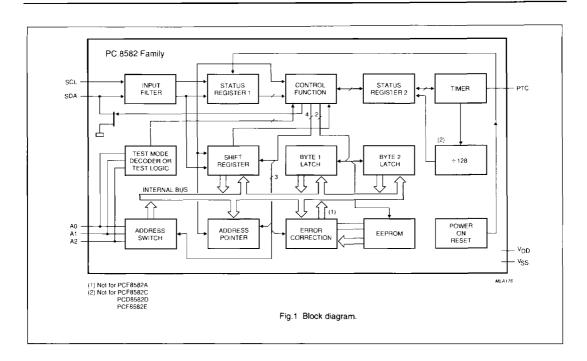

### PC.8582 Family

### **GENERAL DESCRIPTION**

The 2 Kbit (256 x 8-bit) CMOS EEPROMS are floating gate electrically erasable programmable read only memories.

Power consumption is low due to the full CMOS technology used. The programming voltage is generated on-chip using a voltage multiplier.

As data bytes are received and transmitted via the serial I<sup>2</sup>C-bus, a package using eight pins is sufficient.

Chip select is accomplished by the three address inputs, which also allows up to eight devices to be connected to the I<sup>2</sup>C-bus.

### Features

- Non-volatile storage of 2 Kbits organized as 256 x 8-bits

- · Only one power supply required

- On chip voltage multiplier

- Serial input/output bus (I<sup>2</sup>C)

- Automatic word address incrementing

- . Low power consumption

- · Power-on reset

- 10 years non-volatile data retention time

- Pin and address compatible to PCF8570, PCF8571, and PCF8581

- Mini-pack package for SMD technology.

### QUICK SELECTION GUIDE

| TYPE                                                                  | PCF8582A | PCA8582B | PCF8582C | PCD8582D | PCF8582E |

|-----------------------------------------------------------------------|----------|----------|----------|----------|----------|

| extended temperature range                                            | •        | •        | •        | _        | •        |

| extended voltage supply range                                         | -        | -        | •        | •        | -        |

| no external RC required                                               | -        | -        | •        | •        | •        |

| single bit error correction for extended number of erase/write cycles | -        | •        | •        | •        | •        |

### ORDERING INFORMATION

|                      | PACKAGE |              |          |         |  |

|----------------------|---------|--------------|----------|---------|--|

| EXTENDED TYPE NUMBER | PINS    | PIN POSITION | MATERIAL | CODE    |  |

| PCA8582BP            | 8       | DIL          | plastic  | SOT97   |  |

| PCA8582BT            | 16      | SO16L        | plastic  | SOT162A |  |

| PCD8582DP            | 8       | DIL          | plastic  | SOT97   |  |

| PCD8582DT            | 8       | SO8          | plastic  | SOT96A  |  |

| PCF8582AP            | 8       | DIL          | plastic  | SOT97   |  |

| PCF8582AT            | 16      | SO16L        | plastic  | SOT162A |  |

| PCF8582CP            | 8       | DIL          | plastic  | SOT97   |  |

| PCF8582CT            | 16      | SO16L        | plastic  | SOT162A |  |

| PCF8582EP            | 8       | DIL          | plastic  | SOT97   |  |

| PCF8582ET            | 8       | SO8          | plastic  | SOT96A  |  |

## FUNCTIONAL DESCRIPTION Characteristics of the I<sup>2</sup>C-bus

The I<sup>2</sup>C-bus is a bidirectional, 2-line communication between different ICs or modules. The two lines are for serial data (SDA) and serial clock (SCL). Both the SDA and the SCL lines must be connected to a positive supply voltage via a pull-up resistor.

The following protocol has been defined:

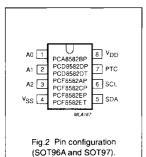

### PINNING

| SYMBOL          | PIN | DESCRIPTION                                              |  |  |

|-----------------|-----|----------------------------------------------------------|--|--|

| A0              | 1   | address input                                            |  |  |

| A1              | 2   | address input                                            |  |  |

| A2              | 3   | address input                                            |  |  |

| V <sub>ss</sub> | 4   | ground                                                   |  |  |

| SDA             | 5   | serial data                                              |  |  |

| SCL             | 6   | serial clock                                             |  |  |

| PTC             | 7   | can be connected to V <sub>DD</sub> or left open-circuit |  |  |

| V <sub>DD</sub> | 8   | positive supply voltage                                  |  |  |

- data transfer may be initiated only when the bus is not busy.

- during data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as control signals.

The following bus conditions have been defined:

Bus not busy: both data and clock lines remain HIGH.

Start data transfer: a change in the state of the data line, from HIGH-to-LOW, while the clock is HIGH defines the start condition.

Stop data transfer: a change in the state of the data line, from

LOW-to-HIGH, while the clock is HIGH, defines the stop condition.

Data valid: the state of the data line represents valid data when, after a start condition, the data line is stable for the duration of the HIGH period of the clock signal. There is one clock pulse per bit of data.

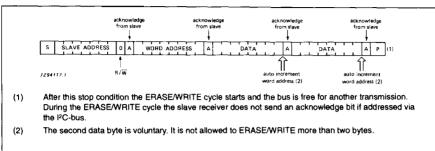

Each data transfer is initiated with a start condition and terminated with a stop condition; the number of the data bytes, transferred between the start and stop conditions is limited to two bytes in the ERASE/WRITE mode and unlimited in the READ mode. The information is transmitted in bytes and each receiver acknowledges with a ninth bit.

### PC.8582 Family

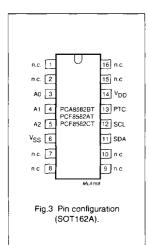

### PINNING

| SYMBOL          | PIN | DESCRIPTION                                              |

|-----------------|-----|----------------------------------------------------------|

| n.c.            | 1   | not connected                                            |

| n.c.            | 2   | not connected                                            |

| <b>A</b> 0      | 3   | address input                                            |

| A1              | 4   | address input                                            |

| A2              | 5   | address input                                            |

| V <sub>ss</sub> | 6   | ground                                                   |

| n.c.            | 7   | not connected                                            |

| n.c.            | 8   | not connected                                            |

| n.c.            | 9   | not connected                                            |

| n.c.            | 10  | not connected                                            |

| SDA             | 11  | serial data                                              |

| SCL             | 12  | serial clock                                             |

| PTC             | 13  | can be connected to V <sub>DD</sub> or left open-circuit |

| V <sub>DD</sub> | 14  | positive supply voltage                                  |

| n.c.            | 15  | not connected                                            |

| n.c.            | 16  | not connected                                            |

By definition a device that sends a signal is called a "transmitter" and the device which receives the signal is called a "receiver". The device which controls the signals is called the "master". The devices that are controlled by the master are called "slaves".

Each byte of eight bits is followed by one acknowledge bit. This acknowledge bit is a HIGH level put on the bus by the transmitter. The master generates an extra acknowledge related clock pulse.

The slave receiver which is addressed is obliged to generate an acknowledge after the reception of each byte.

The master receiver must generate an acknowledge after the reception

of each byte that has been clocked out of the slave transmitter.

The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse.

Set up and hold times must be taken into account. A master receiver must signal an end of data to the slave transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this event the transmitter must leave the data line HIGH to enable the master generation of the stop condition.

(1)

<sup>(1)</sup> Detailed specifications of the I2C-bus are available on request.

## $256 \times 8$ -bit CMOS EEPROMs with $|^2$ C-bus interface

PC.8582 Family

### PC-bus protocol

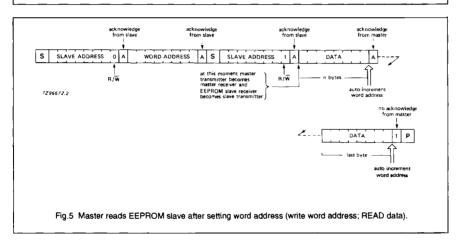

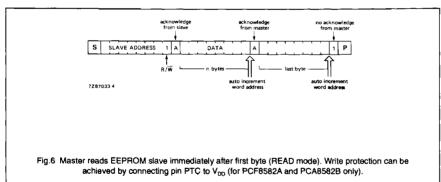

The I<sup>2</sup>C-bus configuration for different READ and WRITE cycles of the EEPROM are shown in Figures 4, 5 and 6.

Fig.4 Master transmitter transmits to EEPROM slave receiver (ERASE/WRITE mode).

| The slave add | ress is defined | in accordance | with the I2C-bu | s specification | as: |    |     |

|---------------|-----------------|---------------|-----------------|-----------------|-----|----|-----|

| 1             | 0               | 1             | 0               | A2              | A1  | A0 | R/W |

### PC.8582 Family

PC.8582 Family

### LIMITING VALUES

In accordance with the Absolute Maximum System (IEC 134)

| SYMBOL           | PARAMETER                                                                   | CONDITIONS               | MIN.                 | MAX.                  | UNIT |

|------------------|-----------------------------------------------------------------------------|--------------------------|----------------------|-----------------------|------|

| V <sub>DD</sub>  | supply voltage                                                              |                          | -0.3                 | +7.0                  | V    |

| V <sub>i</sub>   | voltage on any input                                                        | Z <sub>1</sub>   > 500 Ω | V <sub>ss</sub> -0.8 | V <sub>DD</sub> + 0.8 | ٧    |

| 1,               | current on any input pin                                                    |                          | •                    | 1                     | mA   |

| lo               | output current                                                              |                          | 1-                   | 10                    | mA   |

| T <sub>stp</sub> | storage temperature range                                                   |                          | -65                  | +150                  | °C   |

| T <sub>emb</sub> | operating ambient temperature range<br>PCF8582A/C/E<br>PCA8582B<br>PCD8582D |                          | -40<br>-40<br>-25    | +85<br>+125<br>+70    | င့   |

PC.8582 Family

### CHARACTERISTICS

PCF8582A;  $V_{\rm DD} = 4.5$  to 5.5 V;  $V_{\rm SS} = 0$  V;  $T_{\rm amb} = -40$  to +85 °C PCA8582B;  $V_{\rm DD} = 4.5$  to 5.5 V;  $V_{\rm SS} = 0$  V;  $T_{\rm amb} = -40$  to +125 °C PCF8582C;  $V_{\rm DD} = 2.5$  to 6 V;  $V_{\rm SS} = 0$  V;  $T_{\rm amb} = -40$  to +85 °C PCD8582D;  $V_{\rm DD} = 3$  to 6 V;  $V_{\rm SS} = 0$  V;  $T_{\rm amb} = -25$  to +70 °C PCF8582E;  $V_{\rm DD} = 4.5$  to 5.5 V;  $V_{\rm SS} = 0$  V;  $T_{\rm amb} = -40$  to +85 °C

| SYMBOL           | PARAMETER                   | CONDITIONS                        | MIN.                 | TYP.         | MAX.                  | UNIT |

|------------------|-----------------------------|-----------------------------------|----------------------|--------------|-----------------------|------|

| V <sub>DD</sub>  | supply voltage              |                                   |                      |              |                       |      |

|                  | PCF8582A/E, PCA8582B        |                                   | 4.5                  | -            | 5.5                   | \ V  |

|                  | PCF8582C                    |                                   | 2.5                  | -            | 6.0                   | V    |

|                  | PCD8582D                    |                                   | 3                    | -            | 6                     | V    |

| l <sub>obe</sub> | supply current READ         | f <sub>SCL</sub> = 100 kHz        |                      |              |                       |      |

|                  | PCF8582A                    | V <sub>DD(max)</sub>              | <b> </b> –           | -            | 0.4                   | mA   |

|                  | PCA8582B                    | V <sub>DD(max)</sub>              | _                    | _            | 0.8                   | mA   |

|                  | PCF8582C/PCD8582D           | $V_{DD} = 3 \text{ V}$            | -                    | -            | 0.25                  | mA   |

|                  |                             | $V_{DD} = 6 \text{ V}$            | -                    | -            | 1.6                   | mA   |

|                  | PCF8582E                    | V <sub>DD(max)</sub>              | _                    | L            | 1.6                   | mA   |

| IDDEW            | supply current ERASE/WRITE  | $f_{SCL} = 100 \text{ kHz}$       |                      |              |                       |      |

|                  | PCF8582A/PCA8582B           | V <sub>DD(max)</sub>              | -                    | -            | 2                     | mA   |

|                  | PCF8582C/PCD8582D           | $V_{DD} = 3 V$                    | _                    | -            | 0.35                  | mA   |

|                  |                             | $V_{DD} = 6 \text{ V}$            | -                    | _            | 2.5                   | mA   |

|                  | PCF8582E                    | V <sub>DD(max)</sub>              | -                    | _            | 2.5                   | mA   |

| stb              | supply current STANDBY      |                                   |                      |              |                       |      |

|                  | PCF8582A                    | V <sub>DD(max)</sub>              | _                    | -            | 10                    | μA   |

|                  | PCA8582B                    | V <sub>DD(max)</sub>              | -                    | -            | 20                    | μА   |

|                  | PCF8582C/PCD8582D           | $V_{DD} = 3 V$                    | -                    | -            | 3.5                   | μA   |

|                  |                             | $V_{DD} = 6 V$                    | -                    | 1-           | 10                    | μA   |

|                  | PCF8582E                    | V <sub>DD(max)</sub>              | _                    | -            | 10                    | μΑ   |

| PTC input        | PCF8582A/PCA8582B)          |                                   |                      |              |                       |      |

| V <sub>IH</sub>  | input voltage HIGH          |                                   | V <sub>DD</sub> -0.3 | -            | V <sub>00</sub> + 0.8 | ٧    |

| V <sub>IL</sub>  | input voltage LOW           |                                   | -0.8                 | -            | V <sub>ss</sub> + 0.3 | ٧    |

| PTC input        | PCF8582C/PCD8582D/PCF8582E) |                                   |                      |              |                       |      |

| V <sub>IH</sub>  | input voltage HIGH          |                                   | 0.9 V <sub>DD</sub>  | -            | $V_{DD} + 0.8$        | ν    |

| V <sub>IL</sub>  | input voltage LOW           |                                   | -0.8                 | -            | 0.1 V <sub>DD</sub>   | V    |

| SCL input        |                             |                                   |                      |              |                       |      |

| V <sub>IH</sub>  | input voltage HIGH          |                                   |                      |              |                       |      |

|                  | PCF8582A/PCA8582B           | ł                                 | 3                    | l _          | $V_{00} + 0.8$        | l v  |

|                  | PCF8582C/PCD8582D/PCF8582E  |                                   | 0.7 V <sub>00</sub>  | -            | V <sub>DD</sub> + 0.8 | v    |

| SDA input/       | output                      | <u> </u>                          |                      |              |                       |      |

| V <sub>R</sub>   | input voltage LOW           | I .                               | · · · · ·            |              | T                     |      |

| * R              | PCF8582A/PCA8582B           |                                   | -0.3                 | _            | 1.5                   | v    |

|                  | PCF8582C/PCD8582D/PCF8582E  |                                   | -0.8 V <sub>DD</sub> | _            | 0.3 V <sub>DD</sub>   | ĺv   |

| Vol              | output voltage LOW          | $I_{cr} = 3 \text{ mA}$           | 0.0 v <sub>DD</sub>  | <del> </del> | 0.0 100               | +    |

| * OL             | PCF8582A/PCA8582B           | V <sub>DD</sub> = 4.5 V           | _                    | _            | 0.4                   | v    |

|                  | PCF8582C                    | $V_{DD} = 2.5 \text{ V}$          | _                    | _            | 0.4                   | ĺv   |

|                  | PCD8582D                    | V <sub>DD</sub> = 3 V             | _                    | _            | 0.4                   | Ιν   |

|                  | PCF8582E                    | V <sub>DD(min)</sub>              | _                    | _            | 0.4                   | ľ    |

| I <sub>LO</sub>  | output leakage current      | V <sub>OH</sub> = V <sub>DD</sub> | -                    | 1            | 1                     | μА   |

| <u>'LO</u>       | input leakage current       | $V_1 = V_{00}$ or $V_{ss}$        |                      | <del> </del> | 1                     | μА   |

| u<br>Data retent |                             | 1 -1 - 100 or 1ss                 | l                    |              | 1'                    | Ιμ., |

|                  | , w                         |                                   |                      |              |                       |      |

# $256 \times 8$ -bit CMOS EEPROMs with $1^2$ C-bus interface

PC.8582 Family

### WRITE CYCLE LIMITS

| SYMBOL          | PARAMETER                   | CONDITIONS                                        | MIN.       | MAX.   | UNIT |

|-----------------|-----------------------------|---------------------------------------------------|------------|--------|------|

| t <sub>ew</sub> | ERASE/WRITE cycle time      |                                                   |            |        |      |

|                 | PCF8582A/PCA8582B           |                                                   | 5          | 40     | ms   |

|                 | PCF8582C/PCD8582D/PCF8582E  |                                                   | 5          | 25     | ms   |

| Enduranc        | e                           |                                                   |            |        |      |

| New             | ERASE/WRITE cycles per byte |                                                   |            |        |      |

| 4               | PCF8582A                    |                                                   | -          | 10000  |      |

|                 | PCA8582B                    | T <sub>amb</sub> = 125 °C;                        | ļ          |        | 1    |

|                 |                             | t <sub>ew</sub> = 5 to 40 ms                      | _          | 50000  |      |

|                 |                             | T <sub>emb</sub> = 85 °C;                         | 1          |        | 1    |

|                 |                             | t <sub>EW</sub> = 5 to 40 ms                      | l –        | 100000 |      |

|                 |                             | T <sub>emb</sub> = 33 °C;                         |            |        |      |

|                 |                             | t <sub>ew</sub> = 10 ms                           | <b>]</b> - | 500000 |      |

|                 | PCF8582C                    | T <sub>amb</sub> = 85 °C;                         |            |        |      |

|                 |                             | t <sub>EW</sub> = 5 to 25 ms                      | l          | 100000 | ľ    |

|                 |                             | T <sub>amb</sub> = 33 °C;                         | -          |        |      |

|                 |                             | t <sub>ew</sub> = 10 ms                           | 1-         | 500000 |      |

|                 | PCD8582D                    | $T_{amb} = -25 \text{ to } +70 ^{\circ}\text{C};$ |            |        |      |

|                 |                             | t <sub>ew</sub> = 5 to 25 ms                      | -          | 10000  |      |

|                 |                             | $T_{amb} = 0 \text{ to } +40 ^{\circ}\text{C};$   | 1          | 1      | ì    |

|                 |                             | t <sub>EW</sub> = 10 ms                           | -          | 100000 |      |

|                 | PCF8582E                    | $T_{amb} = -40 \text{ to } +85 \text{ °C};$       |            | 1      | 1    |

|                 | <u> </u>                    | t <sub>EW</sub> = 5 to 25 ms                      | <u> </u>   | 100000 |      |

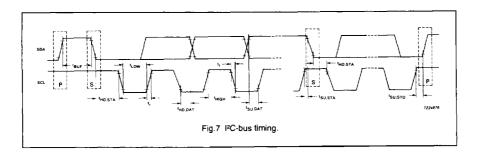

#### PC-BUS CHARACTERISTICS

| SYMBOL              | PARAMETER                                                            | CONDITIONS                       | MIN. | TYP. | MAX. | UNIT |

|---------------------|----------------------------------------------------------------------|----------------------------------|------|------|------|------|

| f <sub>SCL</sub>    | clock frequency                                                      |                                  | 0    | -    | 100  | kHz  |

| C <sub>1</sub>      | input capacitance (SDA; SCL)                                         | V <sub>I</sub> = V <sub>SS</sub> | -    | -    | 7    | pF   |

| t <sub>BUF</sub>    | time the bus must be free before new transmission can start          |                                  | 4.7  | -    | -    | μs   |

| HO:STA              | start condition hold time after which first clock pulse is generated |                                  | 4    | -    | •    | μs   |

| t <sub>LOW</sub>    | clock period LOW                                                     |                                  | 4.7  | -    | -    | μs   |

| t <sub>HIGH</sub>   | clock period HIGH                                                    |                                  | 4    | -    | -    | μs   |

| t <sub>su;sta</sub> | set up time for start condition                                      | repeated start                   | 4.7  | -    | -    | μs   |

| t <sub>hd:dat</sub> | data hold time for bus compatible masters                            |                                  | 5    | -    | -    | μs   |

| t <sub>HD:DAT</sub> | data hold time for bus devices                                       | note 1                           | 0    | -    | -    | ns   |

| t <sub>SU:DAT</sub> | data set up time                                                     |                                  | 250  | -    |      | ns   |

| ţ,                  | SDA and SCL rise time                                                |                                  |      | -    | 1    | μs   |

| ţ,                  | SDA and SCL fall time                                                |                                  | -    | -    | 300  | ns   |

| t <sub>su:sto</sub> | set up time for stop condition                                       |                                  | 4.7  | -    | -    | μs   |

#### Note

The hold time required to bridge the undefined region of the falling edge of SCL must be internally provided by a transmitter. It is not greater than 300 ns.

Purchase of Phillips'  $^{12}$ C components conveys a license under the Phillips'  $^{12}$ C patent to use the components in the  $^{12}$ C-system provided the system conforms to the  $^{12}$ C specification defined by Phillips.

# $256 \times 8$ -bit CMOS EEPROMs with $1^2$ C-bus interface

PC.8582 Family

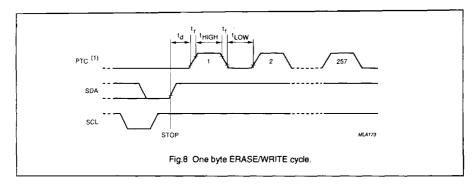

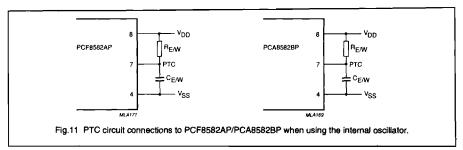

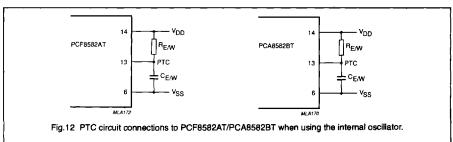

### E/W programming time control

Using external resistor  $R_{\text{EW}}$  and capacitor  $C_{\text{EW}}$  (see Table 1).

Table 1 Recommended  $\rm R_{EW}$  and  $\rm C_{EW}$  combinations (PCF8582A/PCA8582B only).

| R <sub>EW</sub> | C <sub>EW</sub> | T <sub>EW</sub> (typ.) |

|-----------------|-----------------|------------------------|

| (kΩ)            | (nF)            | (ms)                   |

| 56              | 3.3             | 34                     |

| 56              | 2.2             | 21                     |

| 22<br>22        | 3.3             | 13                     |

| 22              | 2.2             | 7.5                    |

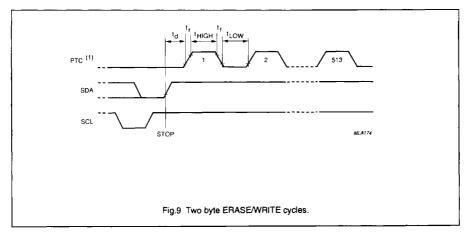

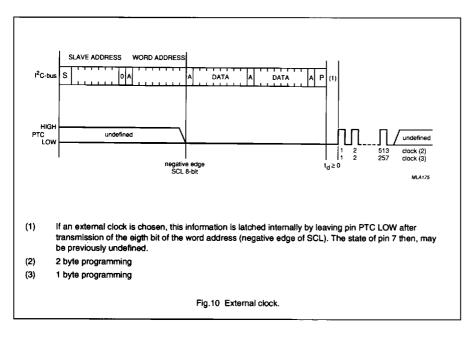

Using external clock (see Table 2 and Figs 8, 9 and 10).

Table 2 E/W programming time control using an external clock.

| SYMBOL | PARAMETER         | MIN. | MAX. | UNIT |

|--------|-------------------|------|------|------|

| CLK    | frequency         | 10   | 50   | kHz  |

| LOW    | clock period LOW  | 10   | -    | μѕ   |

| HIGH   | clock period HIGH | 10   |      | μs   |

|        | rise time         | -    | 300  | ns   |

|        | fall time         | -    | 300  | ns   |

|        | delay time        | 0    | tow  | μs   |

Using an internal oscillator

When using an internal oscillator  $t_{\rm EW}$  has a minimum value of 5 ms and a maximum value of 25 ms; a typical value is 10 ms.