Data Sheet January 1999 File Number 4625

### Radiation Hardened Dual-D Flip-Flop with Set and Reset

Harris' Satellite Applications Flow<sup>TM</sup> (SAF) devices are fully tested and guaranteed to 100kRAD total dose. These QML Class T devices are processed to a standard flow intended to meet the cost and shorter lead-time needs of large volume satellite manufacturers, while maintaining a high level of reliability.

The Harris HCTS74T is a Radiation Hardened positive edge triggered flip-flop with set and reset.

# **Specifications**

Specifications for Rad Hard QML devices are controlled by the Defense Supply Center in Columbus (DSCC). The SMD numbers listed below must be used when ordering.

**Detailed Electrical Specifications for the HCTS74T are contained in SMD 5962-95763.** A "hot-link" is provided from our website for downloading.

http://www.semi.harris.com/families/smdrh.htm

Harris' Quality Management Plan (QM Plan), listing all Class T screening operations, is also available on our website. http://www.semi.harris.com/quality/manuals.htm

# Ordering Information

| ORDERING<br>NUMBER | PART<br>NUMBER | TEMP.<br>RANGE<br>(°C) |

|--------------------|----------------|------------------------|

| 5962R9576301TCC    | HCTS74DTR      | -55 to 125             |

| HCTS74D/Sample     | HCTS74D/Sample | 25                     |

| 5962R9576301TXC    | HCTS74KTR      | -55 to 125             |

| HCTS74K/Sample     | HCTS74K/Sample | 25                     |

NOTE: *Minimum order quantity for -T is 1000 units*Orders must be placed through Harris Sales or Rep Offices.

#### Features

- QML Class T. Per MIL-PRF-38535

- · Radiation Performance

- Gamma Dose (y) 1 x 10<sup>5</sup> RAD(Si)

- Latch-Up Free Under Any Conditions

- SEP Effective LET No Upsets: >100 MEV-cm<sup>2</sup>/mg

- Single Event Upset (SEU) Immunity < 2 x 10<sup>-9</sup> Errors/Bit-Day (Typ)

- · 3 Micron Radiation Hardened SOS CMOS

- · Significant Power Reduction Compared to LSTTL ICs

- DC Operating Voltage Range: 4.5V to 5.5V

- · LSTTL Input Compatibility

- $V_{II} = 0.8V Max$

- $V_{IH} = V_{CC/2} Min$

- Input Current Levels Ii ≤ 5mA at V<sub>OI</sub>, V<sub>OH</sub>

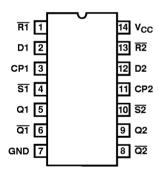

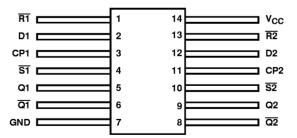

#### **Pinouts**

#### HCTS74T (SBDIP), CDIP2-T14 TOP VIEW

# HCTS74T (FLATPACK), CDFP3-F14 TOP VIEW

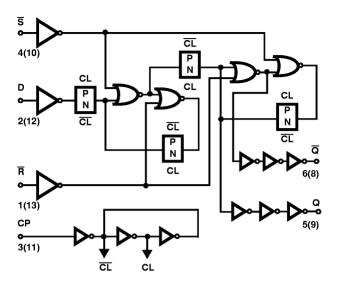

# Functional Diagram

**TRUTH TABLE**

| INPUTS |       |    | OUTPUTS |    |           |

|--------|-------|----|---------|----|-----------|

| SET    | RESET | СР | D       | q  | Q         |

| L      | Н     | Х  | Х       | Н  | L         |

| Н      | L     | Х  | Х       | L  | н         |

| L      | L     | Х  | Х       | H† | Н†        |

| Н      | Н     |    | Н       | Н  | L         |

| Н      | Н     |    | L       | L  | Н         |

| Н      | Н     | L  | Х       | Q0 | <u>Q0</u> |

NOTE: L = Logic Level Low, H = Logic Level High, X = Don't Care \_/ = Transition from Low to High Level.

Q0 = The level of Q before the indicated input conditions were established.

$<sup>\</sup>dagger$  This configuration is non-stable, that is, it will not persist when set and reset inputs return to their inactive (High) level.

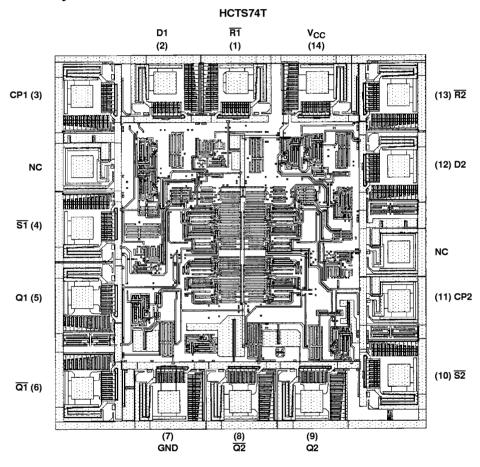

#### Die Characteristics

**DIE DIMENSIONS:**

$(2261\mu m \times 2235\mu m \times 533\mu m \pm 51\mu m)$

89 x 88 x 21mils ±2mil

**METALLIZATION:**

Type: Al Si

Thickness: 11kÅ ±1kÅ

**SUBSTRATE POTENTIAL:**

Unbiased (Silicon on Sapphire)

**BACKSIDE FINISH:**

Sapphire

PASSIVATION:

Type: Silox (S<sub>i</sub>O<sub>2</sub>)

Thickness: 13kÅ ±2.6kÅ

**WORST CASE CURRENT DENSITY:**

< 2.0e5 A/cm<sup>2</sup>

TRANSISTOR COUNT:

200

PROCESS:

CMOS SOS

# Metallization Mask Layout

NOTE: The die diagram is a generic plot from a similar HCS device. It is intended to indicate approximate die size and bond pad location. The mask series for the HCTS74 is TA14438A.

All Harris Semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Harris Semiconductor products are sold by description only. Harris Semiconductor reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Harris is believed to be accurate and reliable. However, no responsibility is assumed by Harris or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Harris or its subsidiaries.

For information regarding Harris Semiconductor and its products, call 1-800-4-HARRIS or see web site http://www.semi.harris.com