AN95 • AN103 • AN107

## 128K

# X84129

## MPS<sup>™</sup> EEPROM

## **µPort Saver EEPROM**

## **FEATURES**

- Up to 10MHz data transfer rate at 5V operator

- 25ns Read Access Time

- · Direct interface to microprocessors and microcontrollers

- -Eliminates I/O port requirements

- -No interface glue logic required

- -Eliminates need for parallel to serial converters

- Low power CMOS

- -2.5V-5.5V version

- -Standby current less than 1µA

- -Active current less than 1mA

- Byte or page write capable -32-byte page write mode

- Typical nonvolatile write cycle time: 2ms

- High reliability

- -100,000 endurance cycles

- -Guaranteed data retention: 100 years

- Small packages options

- -8-lead XBGA package

- -14-lead SOIC package

- -28-lead TSSOP package

## DESCRIPTION

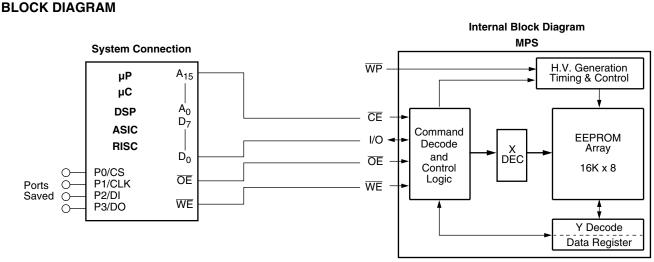

The µPort Saver memories need no serial ports or special hardware and connect to the processor memory bus. Replacing bytewide data memory, the µPort Saver uses bytewide memory control functions, takes a fraction of the board space and consumes much less power. Replacing serial memories, the µPort Saver provides all the serial benefits, such as low cost, low power, low voltage, and small package size, while releasing I/Os for more important uses.

The µPort Saver memory outputs data within 25ns of an active read signal. This is less than the read access time of most hosts and provides "no-wait-state" operation. This prevents bottlenecks on the bus. With rates to 10MHz, the µPort Saver supplies data faster than required by most host read cycle specifications. This eliminates the need for software NOPs.

The µPort Saver memories communicate over one line of the data bus using a sequence of standard bus read and write operations. This "bit serial" interface allows the µPort Saver to work well in 8-bit, 16-bit, 32-bit, and 64-bit systems.

A Write Protect ( $\overline{WP}$ ) pin prevents inadvertent writes to the memory.

Xicor EEPROMs are designed and tested for applications requiring extended endurance. Inherent data retention is greater than 100 years.

## REV 1.1.2 9/8/00

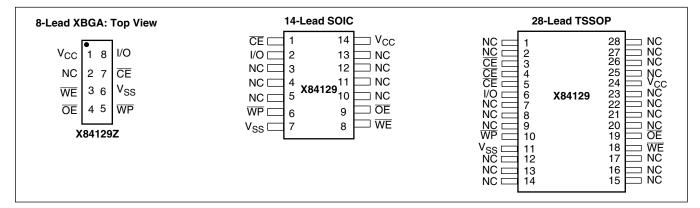

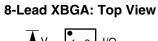

## **PIN CONFIGURATIONS**

#### **PIN NAMES**

| Pin             | Description         |

|-----------------|---------------------|

| I/O             | Data Input/Output   |

| CE              | Chip Enable Input   |

| ŌĒ              | Output Enable Input |

| WE              | Write Enable Input  |

| WP              | Write Protect Input |

| V <sub>CC</sub> | Supply Voltage      |

| V <sub>SS</sub> | Ground              |

| NC              | No Connect          |

## PACKAGE SELECTION GUIDE

| 84129 | 8-Lead XBGA   |  |

|-------|---------------|--|

|       | 14-Lead SOIC  |  |

|       | 28-Lead TSSOP |  |

## **PIN DESCRIPTIONS**

## Chip Enable (CE)

The Chip Enable input must be LOW to enable all read/ write operations. When  $\overline{CE}$  is HIGH, the chip is deselected, the I/O pin is in the high impedance state, and unless a nonvolatile write operation is underway, the device is in the standby power mode.

## Output Enable (OE)

The Output Enable input must be LOW to enable the output buffer and to read data from the device on the  $\mbox{I}/\ O$  line.

## Write Enable (WE)

The Write Enable input must be LOW to write either data or command sequences to the device.

## Data In/Data Out (I/O)

Data and command sequences are serially written to or serially read from the device through the I/O pin.

## Write Protect (WP)

When the Write Protect input is LOW, nonvolatile writes to the device are disabled. When  $\overline{WP}$  is HIGH, all functions, including nonvolatile writes, operate normally. If a nonvolatile write cycle is in progress,  $\overline{WP}$  going LOW will have no effect on the cycle already underway, but will inhibit any additional nonvolatile write cycles.

## **DEVICE OPERATION**

The X84129 are serial EEPROMs designed to interface directly with most microprocessor buses. Standard  $\overline{CE}$ ,  $\overline{OE}$ , and  $\overline{WE}$  signals control the read and write operations, and a single I/O line is used to send and receive data and commands serially.

## **Data Timing**

Data input on the I/O line is latched on the rising edge of either  $\overline{WE}$  or  $\overline{CE}$ , whichever occurs first. Data output on the I/O line is active whenever both  $\overline{OE}$  and  $\overline{CE}$  are LOW. Care should be taken to ensure that  $\overline{WE}$  and  $\overline{OE}$  are never both LOW while  $\overline{CE}$  is LOW.

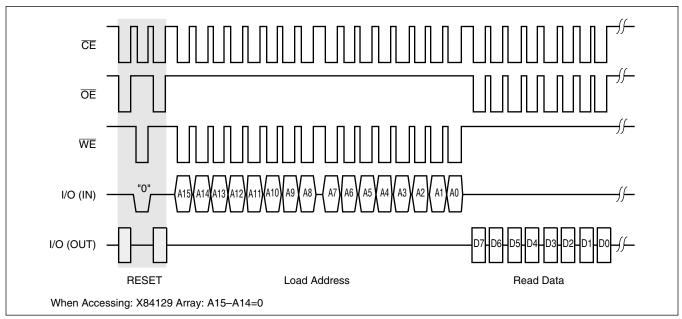

## **Read Sequence**

A read sequence consists of sending a 16-bit address followed by the reading of data serially. The address is written by issuing 16 separate write cycles ( $\overline{WE}$  and  $\overline{CE}$  LOW,  $\overline{OE}$  HIGH) to the part without a read cycle between the write cycles. The address is sent serially, most significant bit first, over the I/O line. Note that this sequence is fully static, with no special timing restrictions, and the processor is free to perform other tasks on the bus whenever the device  $\overline{CE}$  pin is HIGH. Once the 16 address bits are sent, a byte of data can be read on the I/O line by issuing 8 separate read cycles ( $\overline{OE}$ and  $\overline{CE}$  LOW,  $\overline{WE}$  HIGH). At this point, writing a '1' will terminate the read sequence and enter the low power standby state, otherwise the device will await further reads in the sequential read mode.

## **Sequential Read**

The byte address is automatically incremented to the next higher address after each byte of data is read. The data stored in the memory at the next address can be read sequentially by continuing to issue read cycles. When the highest address in the array is reached, the address counter rolls over to address \$0000 and reading may be continued indefinitely.

## **Reset Sequence**

The reset sequence resets the device and sets an internal write enable latch. A reset sequence can be sent at any time by performing a read/write "0"/read operation (see Figs. 1 and 2). This breaks the multiple read or write cycle sequences that are normally used to read from or write to the part. The reset sequence can be used at any time to interrupt or end a sequential read or page load. As soon as the write "0" cycle is complete, the part is reset (unless a nonvolatile write cycle is in progress). The second read cycle in this sequence, and any further read cycles, will read a HIGH on the I/O pin until a valid read sequence (which includes the address) is issued. The reset sequence must be issued at the beginning of both read and write sequences to be sure the device initiates these operations properly.

## Figure 1. Read Sequence

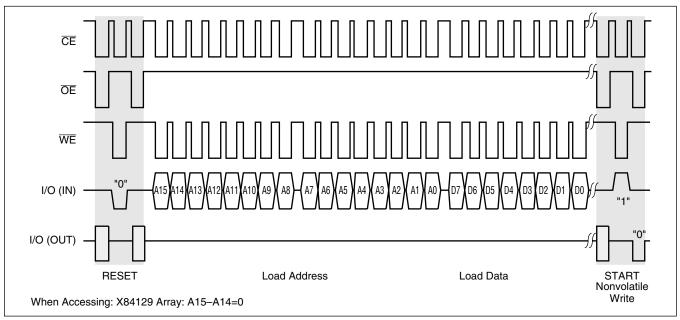

## Figure 2. Write Sequence

## Write Sequence

A nonvolatile write sequence consists of sending a reset sequence, a 16-bit address, up to 32 bytes of data, and then a special "start nonvolatile write cycle" command sequence.

The reset sequence is issued first (as described in the Reset Sequence section) to set an internal write enable latch. The address is written serially by issuing 16 separate write cycles ( $\overline{WE}$  and  $\overline{CE}$  LOW,  $\overline{OE}$  HIGH) to the part without any read cycles between the writes. The address is sent serially, most significant bit first, on the I/O pin. Up to 32 bytes of data are written by issuing a multiple of 8 write cycles. Again, no read cycles are allowed between writes.

The nonvolatile write cycle is initiated by issuing a special read/write "1"/read sequence. The first read cycle ends the page load, then the write "1" followed by a read starts the nonvolatile write cycle. The device recognizes 32-byte pages.

When sending data to the part, attempts to exceed the upper address of the page will result in the address counter "wrapping-around" to the first address on the page, where data loading can continue. For this reason, sending more than 256 consecutive data bits will result in overwriting previous data. A nonvolatile write cycle will not start if a partial or incomplete write sequence is issued. The internal write enable latch is reset when the nonvolatile write cycle is completed and after an invalid write to prevent inadvertent writes. Note that this sequence is fully static, with no special timing restrictions. The processor is free to perform other tasks on the bus whenever the chip enable pin ( $\overline{CE}$ ) is HIGH.

## Nonvolatile Write Status

The status of a nonvolatile write cycle can be determined at any time by simply reading the state of the I/O pin on the device. This pin is read when  $\overline{OE}$  and  $\overline{CE}$  are LOW and  $\overline{WE}$  is HIGH. During a nonvolatile write cycle the I/O pin is LOW. When the nonvolatile write cycle is complete, the I/O pin goes HIGH. A reset sequence can also be issued during a nonvolatile write cycle with the same result: I/O is LOW as long as a nonvolatile write cycle is in progress, and I/O is HIGH when the nonvolatile write cycle is done.

## **Low Power Operation**

The device enters an idle state, which draws minimal current when:

- an illegal sequence is entered. The following are the more common illegal sequences:

- Read/Write/Write—any time

- Read/Write '1'—When writing the address or writing data.

- Write '1'-when reading data

- Read/Read/Write '1'—after data is written to device, but before entering the NV write sequence.

- the device powers-up;

- a nonvolatile write operation completes.

While a sequential read is in progress, the device remains in an active state. This state draws more current than the idle state, but not as much as during a read itself. To go back to the lowest power condition, an invalid condition is created by writing a '1' after the last bit of a read operation.

## Write Protection

The following circuitry has been included to prevent inadvertent nonvolatile writes:

- The internal Write Enable latch is reset upon power-up.

- A reset sequence must be issued to set the internal write enable latch before starting a write sequence.

- A special "start nonvolatile write" command sequence is required to start a nonvolatile write cycle.

- The internal Write Enable latch is reset automatically at the end of a nonvolatile write cycle.

- The internal Write Enable latch is reset and remains reset as long as the WP pin is LOW, which blocks all nonvolatile write cycles.

- The internal Write Enable latch resets on an invalid write operation.

## **ABSOLUTE MAXIMUM RATINGS**

| Temperature under bias6                | 5°C to +135°C |

|----------------------------------------|---------------|

| Storage temperature6                   | 5°C to +150°C |

| Terminal voltage with respect to VSS   | –1V to +7V    |

| DC output current                      | 5mA           |

| Lead temperature (soldering, 10 second | ds)300°C      |

## COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions (above those indicated in the operational sections of this specification) is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **RECOMMENDED OPERATING CONDITIONS**

| Temperature | Min.  | Max.  |

|-------------|-------|-------|

| Commercial  | 0°C   | +70°C |

| Industrial  | -40°C | +85°C |

| Supply Voltage | Limits       |

|----------------|--------------|

| X84129-2.5     | 2.5V to 5.5V |

## D.C. OPERATING CHARACTERISTICS (V<sub>CC</sub> = 5V $\pm 10\%$ )

(Over the recommended operating conditions, unless otherwise specified.)

|                                | Limits                                 |                       | Limits                |      |                                                                                                 |

|--------------------------------|----------------------------------------|-----------------------|-----------------------|------|-------------------------------------------------------------------------------------------------|

| Symbol                         | Parameter                              | Min.                  | Max.                  | Unit | Test Conditions                                                                                 |

| I <sub>CC1</sub>               | V <sub>CC</sub> supply current (read)  |                       | 1                     | mA   | $\overline{OE} = V_{IL}, \overline{WE} = V_{IH}, I/O = Open, \overline{CE} clocking$<br>@ 10MHz |

| I <sub>CC2</sub>               | V <sub>CC</sub> supply current (write) |                       | 2                     | mA   | I <sub>CC</sub> during nonvolatile write cycle all inputs at CMOS levels                        |

| I <sub>SB1</sub>               | V <sub>CC</sub> standby current        |                       | 1                     | μA   | $\overline{CE} = V_{CC}$ , Other Inputs = $V_{CC}$ or $V_{SS}$                                  |

| ILI                            | Input leakage current                  |                       | 10                    | μA   | $V_{IN} = V_{SS}$ to $V_{CC}$                                                                   |

| I <sub>LO</sub>                | Output leakage current                 | 10                    |                       | μA   | $V_{OUT} = V_{SS}$ to $V_{CC}$                                                                  |

| V <sub>IL</sub> <sup>(1)</sup> | Input LOW voltage                      | -0.5                  | V <sub>CC</sub> x 0.3 | V    |                                                                                                 |

| V <sub>IH</sub> <sup>(1)</sup> | Input HIGH voltage                     | V <sub>CC</sub> x 0.7 | V <sub>CC</sub> + 0.5 | V    |                                                                                                 |

| V <sub>OL</sub>                | Output LOW voltage                     |                       | 0.4                   | V    | I <sub>OL</sub> = 2.1mA                                                                         |

| V <sub>OH</sub>                | Output HIGH voltage                    | V <sub>CC</sub> – 0.8 |                       | V    | I <sub>OH</sub> = -1mA                                                                          |

Note: (1)  $V_{IL}$  Min. and  $V_{IH}$  Max. are for reference only and are not tested.

D.C. OPERATING CHARACTERISTICS ( $V_{CC}$  = 2.5V to 5.5V) (Over the recommended operating conditions, unless otherwise specified.)

|                                |                                           | Limits                |                       |      |                                                                                                      |

|--------------------------------|-------------------------------------------|-----------------------|-----------------------|------|------------------------------------------------------------------------------------------------------|

| Symbol                         | Parameter                                 | Min.                  | Max.                  | Unit | Test Conditions                                                                                      |

| I <sub>CC1</sub>               | V <sub>CC</sub> supply current (Read)     |                       | 500                   | μA   | $\overline{OE} = V_{IL}$ , $\overline{WE} = V_{IH}$ , I/O = Open, $\overline{CE}$ clocking<br>@ 5MHz |

| I <sub>CC2</sub>               | V <sub>CC</sub> supply current<br>(Write) |                       | 2                     | mA   | I <sub>CC</sub> during nonvolatile write cycle all inputs at CMOS levels                             |

| I <sub>SB1</sub>               | V <sub>CC</sub> standby current           | by current 1          |                       | μA   | $\overline{CE} = V_{CC}$ , Other inputs = $V_{CC}$ or $V_{SS}$                                       |

| ۱ <sub>LI</sub>                | Input leakage current                     |                       | 10                    | μA   | $V_{IN} = V_{SS}$ to $V_{CC}$                                                                        |

| I <sub>LO</sub>                | Output leakage current                    | 10                    |                       | μA   | $V_{OUT} = V_{SS}$ to $V_{CC}$                                                                       |

| V <sub>IL</sub> <sup>(1)</sup> | Input LOW voltage                         | -0.5                  | V <sub>CC</sub> x 0.3 | V    |                                                                                                      |

| V <sub>IH</sub> <sup>(1)</sup> | Input HIGH voltage                        | V <sub>CC</sub> x 0.7 | V <sub>CC</sub> + 0.5 | V    |                                                                                                      |

| V <sub>OL</sub>                | Output LOW voltage                        |                       | 0.4                   | V    | $I_{OL} = 1$ mA, $V_{CC} = 3V$                                                                       |

| V <sub>OH</sub>                | Output HIGH voltage                       | V <sub>CC</sub> – 0.4 |                       | V    | $I_{OH} = -400 \mu A$ , $V_{CC} = 3V$                                                                |

## **CAPACITANCE** $T_A = +25^{\circ}C$ , F = 1MHZ, $V_{CC} = 5V$

| Symbol                          | Parameter                | Max. | Unit | Test Conditions |

|---------------------------------|--------------------------|------|------|-----------------|

| C <sub>I/O</sub> <sup>(2)</sup> | Input/Output capacitance | 8    | pF   | $V_{I/O} = 0V$  |

| C <sub>IN</sub> <sup>(2)</sup>  | Input capacitance        | 6    | pF   | $V_{IN} = 0V$   |

Note: (2) Periodically sampled, but not 100% tested.

## **POWER-UP TIMING**

| Symbol Parameter                |                             | Max. | Unit |

|---------------------------------|-----------------------------|------|------|

| t <sub>PUR</sub> <sup>(3)</sup> | Power-up to read operation  | 2    | ms   |

| t <sub>PUW</sub> <sup>(3)</sup> | Power-up to write operation | 5    | ms   |

Note: (3) Time delays required from the time the  $V_{CC}$  is stable until the specific operation can be initiated. Periodically sampled, but not 100% tested.

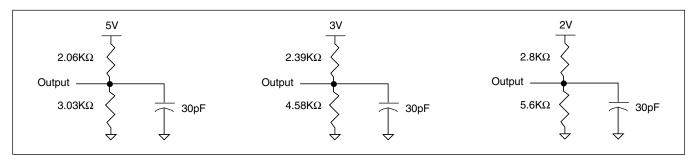

## A.C. CONDITIONS OF TEST

| Input pulse levels             | $V_{CC}$ x 0.1 to $V_{CC}$ x 0.9 |

|--------------------------------|----------------------------------|

| Input rise and fall times      | 5ns                              |

| Input and output timing levels | V <sub>CC</sub> x 0.5            |

## EQUIVALENT A.C. LOAD CIRCUITS

## SYMBOL TABLE

| WAVEFORM | INPUTS                            | OUTPUTS                             |

|----------|-----------------------------------|-------------------------------------|

|          | Must be steady                    | Will be<br>steady                   |

|          | May change<br>from LOW to<br>HIGH | Will change<br>from LOW to<br>HIGH  |

|          | May change<br>from HIGH to<br>LOW | Will change<br>from HIGH to<br>LOW  |

|          | Don't Care:<br>Changes<br>Allowed | Changing:<br>State Not<br>Known     |

|          | N/A                               | Center Line<br>is High<br>Impedance |

## X84129

A.C. CHARACTERISTICS (Over the recommended operating conditions, unless otherwise specified.)

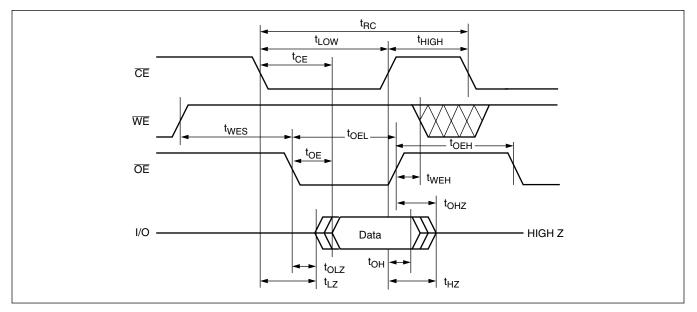

## Read Cycle Limits-X84129<sup>†</sup>

|                                 | V <sub>CC</sub> = 2.5V – 5.5V                            |      | 5V – 5.5V |      |

|---------------------------------|----------------------------------------------------------|------|-----------|------|

| Symbol                          | Parameter                                                | Min. | Max.      | Unit |

| t <sub>RC</sub>                 | Read cycle time                                          | 200  |           | ns   |

| t <sub>CE</sub>                 | CE access time                                           |      | 50        | ns   |

| t <sub>OE</sub>                 | OE access time                                           |      | 50        | ns   |

| tOEL                            | OE pulse width                                           | 60   |           | ns   |

| t <sub>OEH</sub>                | OE High recovery time                                    | 60   |           | ns   |

| t <sub>LOW</sub>                | CE LOW time                                              | 70   |           | ns   |

| thigh                           | CE HIGH time                                             | 120  |           | ns   |

| t <sub>LZ</sub> <sup>(4)</sup>  | CE LOW to output in low Z                                | 0    |           | ns   |

| t <sub>HZ</sub> <sup>(4)</sup>  | CE HIGH to output in high Z                              | 0    | 30        | ns   |

| t <sub>OLZ</sub> <sup>(4)</sup> | OE LOW to output in low Z                                | 0    |           | ns   |

| t <sub>OHZ</sub> <sup>(4)</sup> | OE HIGH to output in high Z                              | 0    | 30        | ns   |

| t <sub>OH</sub>                 | Output hold from $\overline{CE}$ or $\overline{OE}$ HIGH | 0    |           | ns   |

| t <sub>WES</sub>                | WE HIGH setup time                                       | 25   |           | ns   |

| t <sub>WEH</sub>                | WE HIGH hold time                                        | 25   |           | ns   |

Note: (4) Periodically sampled, but not 100% tested. t<sub>HZ</sub> and t<sub>OHZ</sub> are measured from the point where  $\overline{CE}$  or  $\overline{OE}$  goes HIGH (whichever occurs first) to the time when I/O is no longer being driven into a 5pF load.

<sup>†</sup> Contact factory for 10MHz X84129 availability

## **Read Cycle**

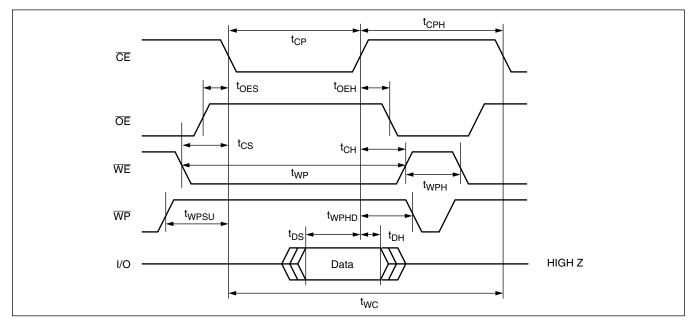

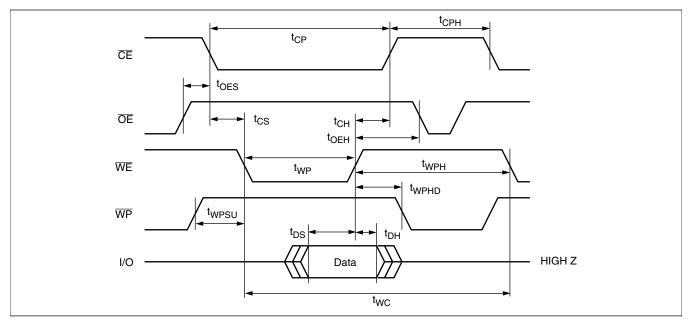

## Write Cycle Limits-X84129

|                                  | Parameter                    | $V_{CC} = 2.5V - 5.5V$ |      |      |

|----------------------------------|------------------------------|------------------------|------|------|

| Symbol                           |                              | Min.                   | Max. | Unit |

| t <sub>NVWC</sub> <sup>(5)</sup> | Nonvolatile write cycle time |                        | 5    | ms   |

| t <sub>WC</sub>                  | Write cycle time             | 200                    |      | ns   |

| t <sub>WP</sub>                  | WE pulse width               | 40                     |      | ns   |

| t <sub>WPH</sub>                 | WE HIGH recovery time        | 150                    |      | ns   |

| t <sub>CS</sub>                  | Write setup time             | 0                      |      | ns   |

| tсн                              | Write hold time              | 0                      |      | ns   |

| t <sub>CP</sub>                  | CE pulse width               | 40                     |      | ns   |

| t <sub>CPH</sub>                 | CE HIGH recovery time        | 150                    |      | ns   |

| tOES                             | OE HIGH setup time           | 25                     |      | ns   |

| t <sub>OEH</sub>                 | OE HIGH hold time            | 25                     |      | ns   |

| t <sub>DS</sub> <sup>(6)</sup>   | Data setup time              | 20                     |      | ns   |

| t <sub>DH</sub> <sup>(6)</sup>   | Data hold time               | 5                      |      | ns   |

| twpsu <sup>(7)</sup>             | WP HIGH setup                | 100                    |      | ns   |

| twPHD <sup>(7)</sup>             | WP HIGH hold                 | 100                    |      | ns   |

Notes: (5) t<sub>NVWC</sub> is the time from the falling edge of OE or CE (whichever occurs last) of the second read cycle in the "start nonvolatile write (c) NWW is a non-neuronal and name of the self-timed, internal nonvolatile write cycle is completed.

(6) Data is latched into the X84129 on the rising edge of CE or WE, whichever occurs first.

(7) Periodically sampled, but not 100% tested.

## **CE** Controlled Write Cycle

## WE Controlled Write Cycle

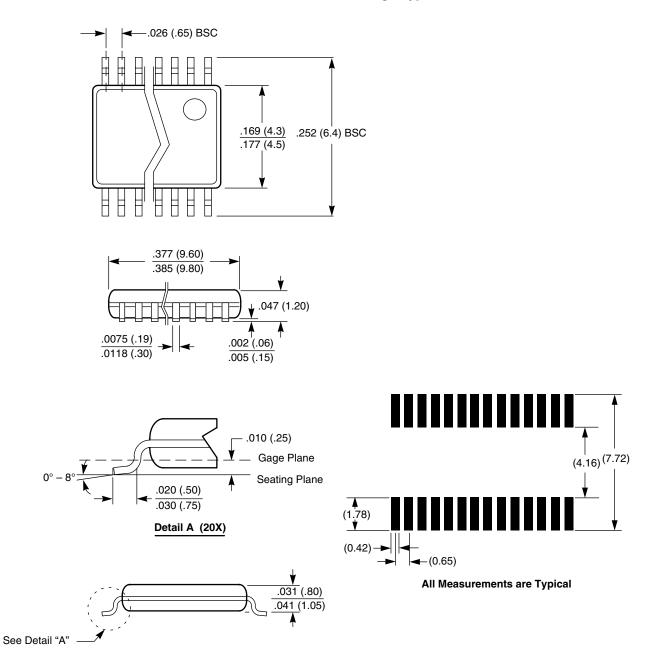

## **PACKAGING INFORMATION**

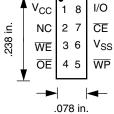

## 8-Lead XBGA

## 8-Lead XBGA Package

| Complete Part Number | <u>Top Mark</u> |

|----------------------|-----------------|

| X84129Z - 2.5        | XAAG            |

| X84129ZI - 2.5       | XADF            |

#### NOTE: ALL DIMENSIONS IN µM (to convert into inches, 1µm = 3.94 x 10<sup>-5</sup> inch) ALL DIMENSIONS ARE TYPICAL VALUES

X84129: Bottom View

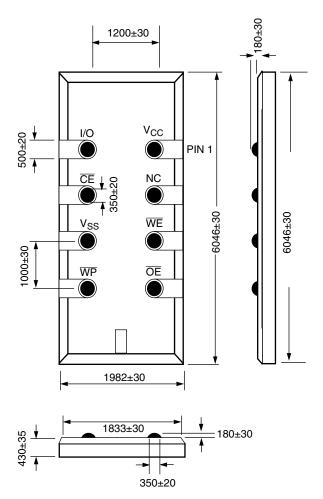

## PACKAGING INFORMATION

14-Lead Plastic Small Outline Gullwing Package Type S

#### NOTE: ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)

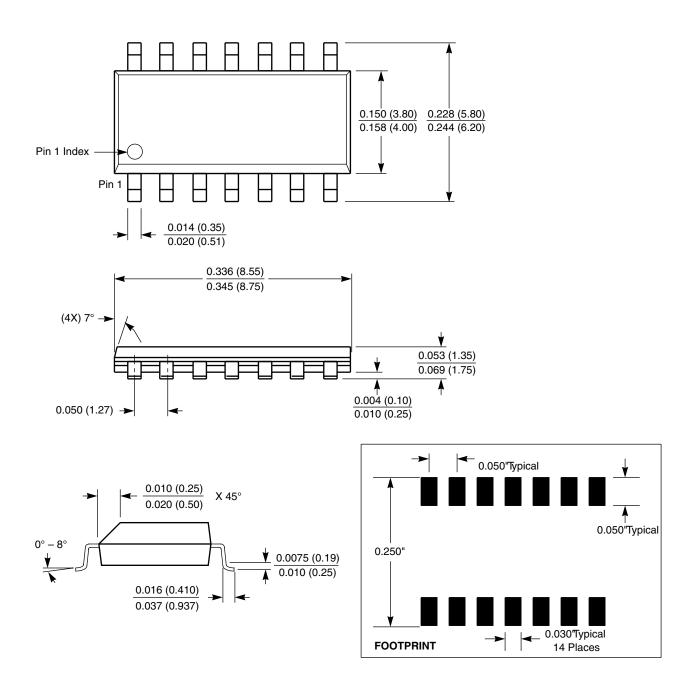

## PACKAGING INFORMATION

28-Lead Plastic, TSSOP Package Type V

NOTE: ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)

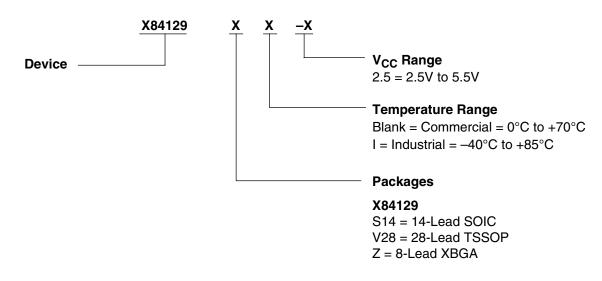

#### **Ordering Information**

#### Part Mark Convention

#### 8-Lead XBGA Package

| Complete Part Number | <u>Top Mark</u> |  |  |

|----------------------|-----------------|--|--|

| X84129Z-2.5          | XAAG            |  |  |

| X84129ZI-2.5         | XADF            |  |  |

#### LIMITED WARRANTY

©Xicor, Inc. 2000 Patents Pending

Devices sold by Xicor, Inc. are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. Xicor, Inc. makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. Xicor, Inc. makes no warranty of merchantability or fitness for any purpose. Xicor, Inc. reserves the right to discontinue production and change specifications and prices at any time and without notice.

Xicor, Inc. assumes no responsibility for the use of any circuitry other than circuitry embodied in a Xicor, Inc. product. No other circuits, patents, or licenses are implied.

#### TRADEMARK DISCLAIMER:

Xicor and the Xicor logo are registered trademarks of Xicor, Inc. AutoStore, Direct Write, Block Lock, SerialFlash, MPS, and XDCP are also trademarks of Xicor, Inc. All others belong to their respective owners.

#### U.S. PATENTS

Xicor products are covered by one or more of the following U.S. Patents: 4,326,134; 4,393,481; 4,404,475; 4,450,402; 4,486,769; 4,488,060; 4,520,461; 4,533,846; 4,599,706; 4,617,652; 4,668,932; 4,752,912; 4,829,482; 4,874,967; 4,883,976; 4,980,859; 5,012,132; 5,003,197; 5,023,694; 5,084,667; 5,153,880; 5,153,691; 5,161,137; 5,219,774; 5,270,927; 5,324,676; 5,434,396; 5,544,103; 5,587,573; 5,835,409; 5,977,585. Foreign patents and additional patents pending.

#### LIFE RELATED POLICY

In situations where semiconductor component failure may endanger life, system designers using this product should design the system with appropriate error detection and correction, redundancy and back-up features to prevent such an occurrence.

Xicor's products are not authorized for use in critical components in life support devices or systems.

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.