# LM3880-Q1 Three-Rail Simple Power Supply Sequencer

### **1** Features

- · Qualified for automotive applications

- · AEC-Q100 qualified with the following results:

- Device temperature grade: –40°C to 125°C junction uemperature range

- Simple solution for sequencing three voltage rails from a single input signal

- Easily cascade up to three devices to sequence as many as nine voltage rails

- Powerup and powerdown control

- Tiny 2.9-mm x 1.6-mm footprint

- Low quiescent current: 25 µA

- Input voltage range: 2.7 V to 5.5 V

- Standard timing options available

## 2 Applications

- Advanced driver assistance systems (ADAS)

- · Automotive camera modules

- Security cameras

- Servers

- Networking elements

- FPGA power supply sequencing

- Microprocessor and microcontroller sequencing

- Multiple supply sequencing

## **3 Description**

The LM3880-Q1 simple power supply sequencer offers the easiest method to control powerup sequencing and powerdown sequencing of multiple Independent voltage rails. By staggering the startup sequence, it is possible to avoid latch conditions or large in-rush currents that can affect the reliability of the system.

Available in a 6-pin SOT-23 package, the simple sequencer contains a precision enable pin and three open-drain output flags. The open-drain output flags permit that they can be pulled up to distinct voltage supplies separate from the sequencer  $V_{DD}$  (only if they do not exceed the recommended maximum voltage of 0.3 V greater than  $V_{DD}$ ), so as to interface with ICs requiring a range of different enable signals. When the LM3880-Q1 is enabled, the three output flags sequentially release, after individual time delays, thus permitting the connected power supplies to start up. The output flags follow a reverse sequence during power down to avoid latch conditions.

EPROM capability allows every delay and sequence to be fully adjustable. Contact Texas Instruments to request a non-standard configuration.

#### Device Information (1)

| PART NUMBER | PACKAGE     | BODY SIZE (NOM)   |

|-------------|-------------|-------------------|

| LM3880-Q1   | DBV SOT (6) | 2.90 mm × 1.60 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

#### **Simple Power Supply Sequencing**

# **Table of Contents**

| 1 Features                           |     |

|--------------------------------------|-----|

| 2 Applications                       |     |

| 3 Description                        | 1   |

| 4 Revision History                   | 2   |

| 5 Pin Configuration and Functions    |     |

| Pin Functions                        | 3   |

| 6 Specifications                     | 4   |

| 6.1 Absolute Maximum Ratings         | 4   |

| 6.2 ESD Ratings                      | . 4 |

| 6.3 Recommended Operating Conditions | 4   |

| 6.4 Thermal Information              | 4   |

| 6.5 Electrical Characteristics       | 5   |

| 6.6 Typical Characteristics          | 7   |

| 7 Detailed Description               | 9   |

| 7.1 Overview                         | . 9 |

| 7.2 Functional Block Diagram        | 9  |

|-------------------------------------|----|

| 7.3 Feature Description             |    |

| 7.4 Device Functional Modes         |    |

| 8 Application and Implementation    | 13 |

| 8.1 Application Information         | 13 |

| 8.2 Typical Application             |    |

| 8.3 Dos and Don'ts                  |    |

| 9 Layout                            |    |

| 9.1 Layout Guidelines               |    |

| 9.2 Layout Example                  |    |

| 10 Device and Documentation Support |    |

| 10.1 Device Support                 |    |

| 10.2 Community Resources            |    |

| 10.3 Trademarks                     |    |

| · • • •                             |    |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | Changes from Revision * (November 2018) to Revision A (March 2021) |    |

|----|--------------------------------------------------------------------|----|

| •  | Specified device dimensions in Features section                    | 1  |

| •  | Updated application curve titles                                   | 14 |

# **5** Pin Configuration and Functions

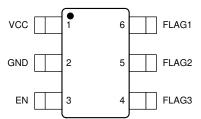

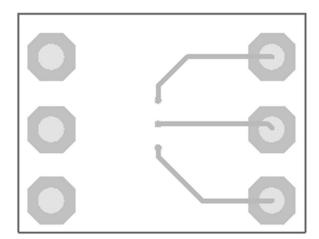

## Figure 5-1. DBV Package 6-Pin SOT-23 Top View

### **Pin Functions**

| PI    | N   | I/O <sup>(1)</sup> | DESCRIPTION          |  |  |  |

|-------|-----|--------------------|----------------------|--|--|--|

| NAME  | NO. | 1/0( /             | DESCRIPTION          |  |  |  |

| EN    | 3   | I                  | Precision enable pin |  |  |  |

| FLAG1 | 6   | 0                  | Open-drain output 1  |  |  |  |

| FLAG2 | 5   | 0                  | Open-drain output 2  |  |  |  |

| FLAG3 | 4   | 0                  | Open-drain output 3  |  |  |  |

| GND   | 2   | G                  | Ground               |  |  |  |

| VCC   | 1   | I                  | Input supply         |  |  |  |

(1) I = input, O = output, G = ground

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature (unless otherwise noted) (1) (2)

|                                      | MIN  | MAX | UNIT |

|--------------------------------------|------|-----|------|

| VCC                                  | -0.3 | 6   | V    |

| EN, FLAG1, FLAG2, FLAG3              | -0.3 | 6   | V    |

| Maximum Flag ON current              |      | 50  | mA   |

| Maximum Junction temperature         |      | 150 | °C   |

| Lead temperature (Soldering, 5 s)    |      | 260 | °C   |

| Storage temperature T <sub>stg</sub> | -65  | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Section 6.3. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

### 6.2 ESD Ratings

|                    |                         |                                                         | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±2    | kV   |

(1) AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                         | MIN  | MAX                   | UNIT |

|-------------------------|------|-----------------------|------|

| VCC to GND              | 2.7  | 5.5                   | V    |

| EN, FLAG1, FLAG2, FLAG3 | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| Junction temperature    | -40  | 125                   | °C   |

#### 6.4 Thermal Information

|                       |                                              | LM3880-Q1    |      |

|-----------------------|----------------------------------------------|--------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DBV (SOT-23) | UNIT |

|                       |                                              | 6 PINS       |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 187.6        | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 127.4        | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 31.5         | °C/W |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 23.3         | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 31.0         | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## **6.5 Electrical Characteristics**

Limits apply to all timing options and  $V_{CC}$  = 3.3 V, unless otherwise specified. Minimum and Maximum limits apply over the full Operating Temperature Range (T<sub>J</sub> = -40°C to +125°C) and are specified through test, design or statistical correlation. Typical values represent the most likely parametric norm at T<sub>J</sub> = 25°C and are provided for reference purposes only.

|                           | PARAMETER                   | TEST CONDITIONS             | MIN <sup>(1)</sup> | TYP <sup>(2)</sup> | MAX <sup>(1)</sup> | UNIT |

|---------------------------|-----------------------------|-----------------------------|--------------------|--------------------|--------------------|------|

| l <sub>Q</sub>            | Operating Quiescent current |                             |                    | 25                 | 80                 | μA   |

| OPEN-DR/                  | AIN FLAGS                   | 1                           | L                  |                    | 1                  |      |

| I <sub>FLAG</sub>         | FLAGx Leakage Current       | V <sub>FLAGx</sub> = 3.3 V  |                    | 1                  | 20                 | nA   |

| V <sub>OL</sub>           | FLAGx Output Voltage Low    | I <sub>FLAGx</sub> = 1.2 mA |                    |                    | 0.4                | V    |

| POWER-U                   | P SEQUENCE                  |                             |                    |                    |                    |      |

| t <sub>d1</sub>           | Timer delay 1 accuracy      | All Other Timing Options    | -15%               |                    | 15%                |      |

|                           |                             | 2 ms Timing Option          | -20%               |                    | 20%                |      |

| t <sub>d2</sub>           | Timer delay 2 accuracy      | All Other Timing Options    | -15%               |                    | 15%                |      |

|                           |                             | 2 ms Timing Option          | -20%               |                    | 20%                |      |

| t <sub>d3</sub>           | Timer delay 3 accuracy      | All Other Timing Options    | -15%               |                    | 15%                |      |

|                           |                             | 2 ms Timing Option          | -20%               |                    | 20%                |      |

| POWER-D                   | OWN SEQUENCE                |                             |                    |                    | 1                  |      |

| t <sub>d4</sub>           | Timer delay 4 accuracy      | All Other Timing Options    | -15%               |                    | 15%                |      |

|                           |                             | 2 ms Timing Option          | -20%               |                    | 20%                |      |

| t <sub>d5</sub>           | Timer delay 5 accuracy      | All Other Timing Options    | -15%               |                    | 15%                |      |

|                           |                             | 2 ms Timing Option          | -20%               |                    | 20%                |      |

| t <sub>d6</sub>           | Timer delay 6 accuracy      | All Other Timing Options    | -15%               |                    | 15%                |      |

|                           |                             | 2 ms Timing Option          | -20%               |                    | 20%                |      |

| TIMING DE                 | LAY ERROR                   |                             |                    |                    | I                  |      |

| $(t_{d(x)} - 400)$        | Ratio of timing delays      | For x = 1 or 4              | 95%                |                    | 105%               |      |

| µs) / t <sub>d(x+1)</sub> |                             | For x = 1 or 4, 2 ms option | 90%                |                    | 110%               |      |

| $t_{d(x)} / t_{d(x+1)}$   | Ratio of timing delays      | For x = 2 or 5              | 95%                |                    | 105%               |      |

|                           |                             | For x = 2 or 5, 2 ms option | 90%                |                    | 110%               |      |

| ENABLE F                  | PIN                         |                             |                    |                    |                    |      |

| V <sub>EN</sub>           | EN pin threshold            |                             | 1.0                | 1.25               | 1.4                | V    |

| I <sub>EN</sub>           | EN pin pullup current       | V <sub>EN</sub> = 0 V       |                    | 7                  |                    | μA   |

(1) Limits are 100% production tested at 25°C. Limits over the operating temperature range are ensured through correlation using Statistical Quality Control (SQC) methods. The limits are used to calculate the TI average outgoing quality level (AOQL).

(2) Typical numbers are at 25°C and represent the most likely parametric norm.

All standard options use Sequence 1 for output flags rise and fall order. Refer to section 11.1.2 for details of other possible sequences.

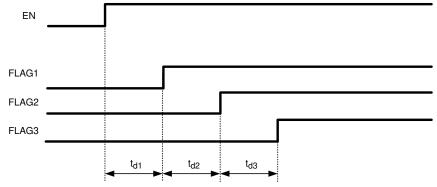

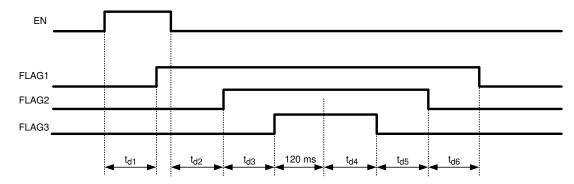

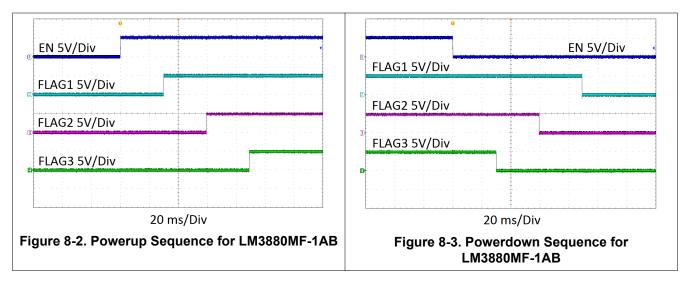

#### Figure 6-1. Timing Requirements

All standard options use Sequence 1 for output flags rise and fall order. Refer to section 11.1.2 for details of other possible sequences.

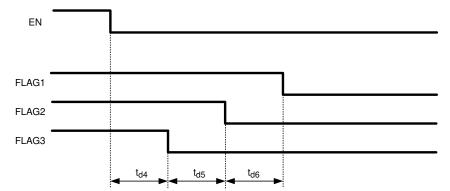

Figure 6-2. Power-Down Sequence

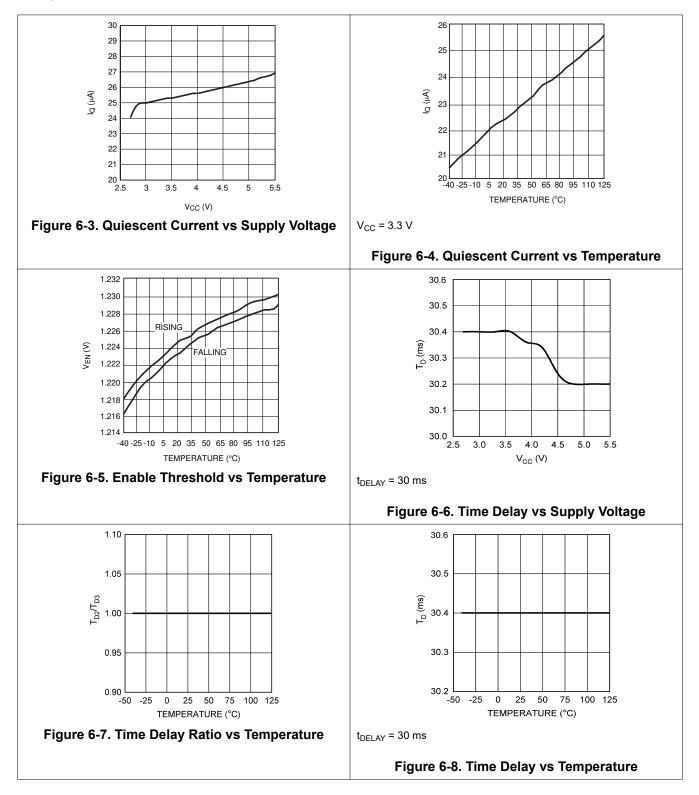

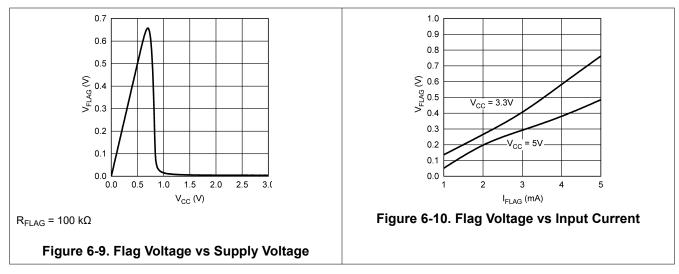

## **6.6 Typical Characteristics**

LM3880-Q1 SNVSB87A – NOVEMBER 2018 – REVISED MARCH 2021

# 7 Detailed Description

### 7.1 Overview

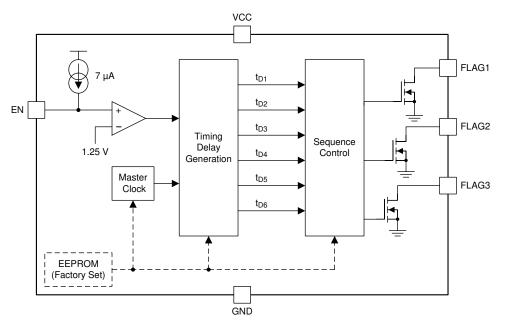

The LM3880-Q1 simple power supply sequencer provides a simple solution for sequencing multiple rails in a controlled manner. Six independent timers are integrated to control the timing sequence (power up and power down) of three open-drain output flags. These flags permit connection to either a shutdown or enable pin of linear regulators and switchers to control the operation of the power supplies. This allows design of a complete power system without concern for large inrush currents or latch-up conditions that can occur.

The timing sequence of the device is controlled entirely by the enable (EN) pin. Upon power up, all the flags are held low until this precision enable is pulled high. When the EN pin is asserted, the power-up sequence starts. An internal counter delays the first flag (FLAG1) from rising until a fixed time period has expired. When the first flag is released, another timer will begin to delay the release of the second flag (FLAG2). This process repeats until all three flags have sequentially been released.

The power-down sequence is the same as power-up sequence, but in reverse. When the EN pin is deasserted a timer will begin that delays the third flag (FLAG3) from pulling low. The second and first flag will then follow in a sequential manner after their appropriate delays. The three timers that are used to control the power-down scheme can also be individually programmed and are completely independent of the power-up timers.

#### 7.2 Functional Block Diagram

### 7.3 Feature Description

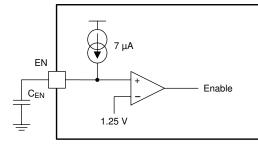

#### 7.3.1 Enable Pin Operation

The timing sequence of the LM3880-Q1 is controlled by the assertion of the enable signal. The enable pin is designed with an internal comparator, referenced to a bandgap voltage (1.25 V), to provide a precision threshold. This allows a delayed timing to be externally set using a capacitor or to start the sequencing based on a certain event, such as a line voltage reaching 90% of nominal. For an additional delayed sequence from the rail powering VCC, simply attach a capacitor to the EN pin as shown in Figure 7-1.

#### Figure 7-1. Capacitor Timing

Using the internal pullup current source to charge the external capacitor ( $C_{EN}$ ) the enable pin delay can be calculated by Equation 1:

$$t_{enable\_delay} = \frac{1.25V \times C_{EN}}{7 \,\mu A}$$

(1)

A resistor divider can also be used to enable the device based on a certain voltage threshold. Take care when sizing the resistor divider to include the effects of the internal current source.

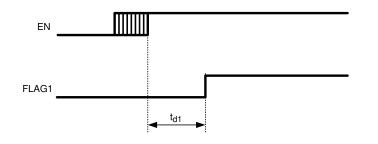

One of the features of the EN pin is that it provides glitch free operation. The first timer will start counting at a rising threshold, but will always reset if the EN pin is deasserted before the first output flag is released. This can be shown in Figure 7-2:

#### Figure 7-2. EN Glitch

#### 7.3.2 Incomplete Sequence Operation

If the enable signal remains high for the entire power-up sequence, then the part will operate as shown in the standard timing diagrams. However, if the enable signal is de-asserted before the power-up sequence is completed the part will enter a controlled shutdown. This allows the system to walk through a controlled power cycling, preventing any latch conditions from occurring. This state only occurs if the enable pin is deasserted after the completion of timer 1, but before the entire power-up sequence is completed.

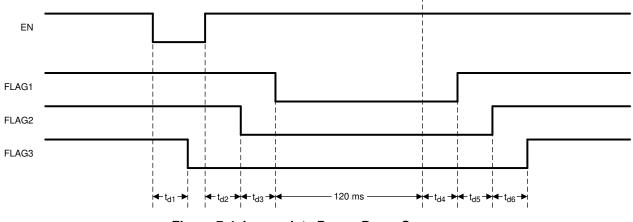

When this event occurs, the falling edge of EN pin resets the current timer and will allow the remaining power-up cycle to complete before beginning the power-down sequence. The power down sequence starts approximately 120 ms after the final power-up flag. This allows output voltages in the system to stabilize before everything is shut down. Figure 7-3 shows this operation.

When the enable signal is deasserted, the part will commence its power-down sequence. If the enable signal is pulled high before the power-down sequence is completed, the part will ensure completion of the power-down sequence before starting power-up. This ensures that the system does not partially power down and power up and helps prevent latch-up events, such as in FPGAs and microprocessors. This state only occurs if the enable pin is pulled high after the completion of timer 1, but before the entire power-down sequence is completed.

When this event occurs, the rising edge of enable pin resets the current timer and will allow the remaining power-down cycle to complete before beginning the power-up sequence. The power-up sequence starts approximately 120 ms after the final power-down flag. This allows the system to fully shut down before it is powered up. Figure 7-4 shows this operation.

Figure 7-4. Incomplete Power-Down Sequence

All the internal timers are generated by a master clock that has an extremely low tempco. This allows for tight accuracy across temperature and a consistent ratio between the individual timers. There is a slight additional delay of approximately 400 µs to timers 1 and 4, which is a result of the EPROM refresh. This refresh time is in addition to the programmed delay time and will be almost insignificant to all but the shortest of timer delays.

### 7.4 Device Functional Modes

#### 7.4.1 Power Up With EN Pin

The timing sequence of the Simple Power Supply Sequencer is controlled entirely by the enable (EN) pin. Upon power up, all the flags are held low until this precision enable is pulled high. After the EN pin is asserted, the power-up sequence will commence.

#### 7.4.2 Power Down With EN Pin

When EN pin is deasserted, the power down sequence will commence. A timer will begin that delays the third flag (FLAG3) from pulling low. The second and first flag will then follow in a sequential manner after their appropriate delays.

## 8 Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

#### 8.1 Application Information

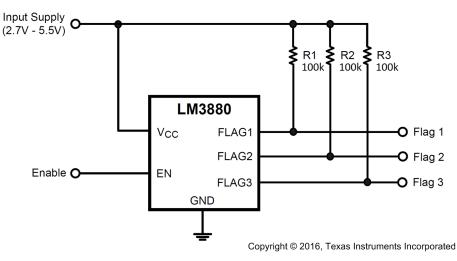

#### 8.1.1 Open Drain Flags Pullup

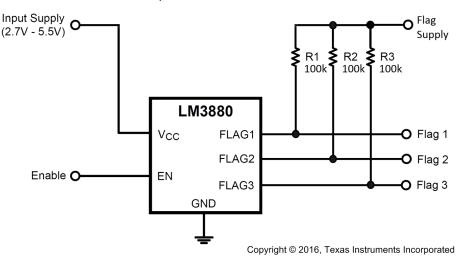

The Simple Power Supply Sequencer contains three open-drain output flags which need to be pulled up for proper operation.  $100-k\Omega$  resistors can be used as pullup resistors.

#### 8.1.2 Enable the Device

See Section 7.3.1.

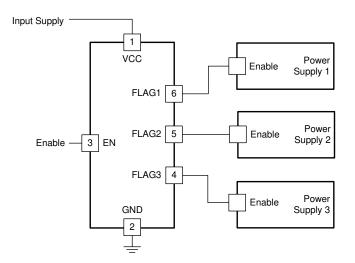

#### 8.2 Typical Application

#### 8.2.1 Simple Sequencing of Three Power Supplies

The Simple Power Supply Sequencer is used to implement a power-up and power-down sequence of three power supplies.

Sequence 1 for the LM3880-Q1, e.g. orderable part number LM3880-Q1MF-1AA has a power-up sequence (1 - 2 - 3) and power-down sequence (3 - 2 - 1). See Table 10-1 and Table 10-2 for other sequence options or contact TI if other sequence options are desired.

Figure 8-1. Typical Application Circuit

#### 8.2.1.1 Design Requirements

For this design example, use the parameters listed in Table 8-1 as the input parameters. The circuit shown in Figure 8-1 can have various power-down sequences depending on the sequence the part is programmed for. See Table 10-1 for power-down sequence options.

| Table 8-1. Design Parameters   |                |  |  |  |

|--------------------------------|----------------|--|--|--|

| DESIGN PARAMETER EXAMPLE VALUE |                |  |  |  |

| Input Supply voltage range     | 2.7 V to 5.5 V |  |  |  |

| Flag Output voltage, EN high   | Input Supply   |  |  |  |

| Flag Output voltage, EN low    | 0 V            |  |  |  |

| Flag Timing Delay              | 30 ms          |  |  |  |

| Power-Up Sequence              | 1 - 2 - 3      |  |  |  |

| Power-Down Sequence            | 3 - 2 - 1      |  |  |  |

#### 8.2.1.2 Detailed Design Procedure

#### Table 8-2. List of Materials

| DESIGNATOR | DESCRIPTION                         | DEVICE           | QUANTITY | MANUFACTURER      |

|------------|-------------------------------------|------------------|----------|-------------------|

| U1         | LM3880-Q1, Sequence 1, 30 ms timing | LM3880-Q1        | 1        | Texas Instruments |

| R1         | 100-kΩ Resistor, 0603               | CRCW0603100KFKEA | 1        | Vishay            |

| R2         | 100-kΩ Resistor, 0603               | CRCW0603100KFKEA | 1        | Vishay            |

| R3         | 100-kΩ Resistor, 0603               | CRCW0603100KFKEA | 1        | Vishay            |

This application uses the Sequence 1 and 30-ms timing options of the simple power supply sequencer. See *Section 8.2.1.3* for details on the sequence and timing option.

#### 8.2.1.3 Application Curves

#### 8.2.2 Sequencing Using Independent Flag Supply

For applications requiring a flag output voltage that is different from the VCC, a separate Flag Supply may be used to pullup the open-drain outputs of the simple power supply sequencer. This is useful when interfacing the flag outputs with inputs that require a different voltage than VCC. The designer must ensure the flag supply voltage is not taken above VCC + 0.3 V as specified in the *Section 6.3*.

Figure 8-4. Sequencing Using Independent Flag Supply

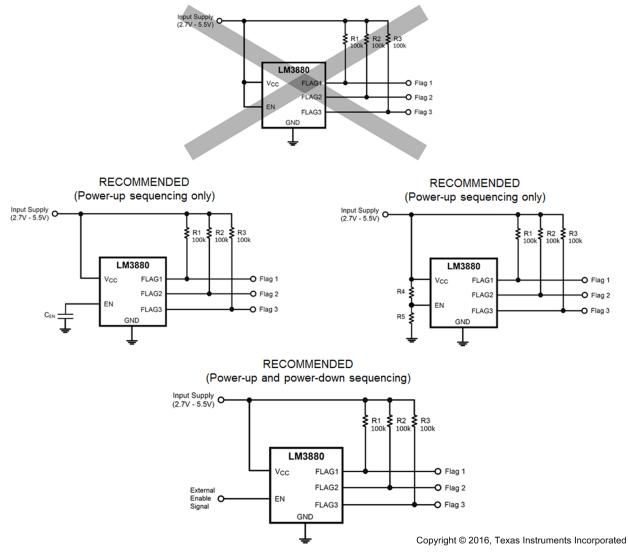

### 8.3 Dos and Don'ts

Connecting the EN pin to VCC is not recommended. During powerup sequencing, maintain the EN voltage to a level below the EN voltage threshold until VCC rises above the minimum operating voltage. If EN is connected to VCC, undefined operation at the flag outputs can occur, especially during slow VCC rising slew rates. For systems requiring only powerup sequencing, a capacitor at the EN pin can be used to create a delay or a resistor divider can be used to enable the device based on a certain voltage threshold. While these solutions work for powerup sequencing, it does not powerdown the flag outputs in sequential fashion because the flag outputs simply follow the input supply. For systems requiring both powerup and powerdown sequencing, use an external enable signal, such as a GPIO signal from a microcontroller, to properly control powerup and powerdown of the flag outputs.

NOT RECOMMENDED

Figure 8-5. Recommended EN Connection

# **Power Supply Recommendations**

The VCC pin should be located as close as possible to the input supply (2.7–5.5 V). An input capacitor is not required but is recommended when noise might be present on the VCC pin. A  $0.1-\mu$ F ceramic capacitor may be used to bypass this noise.

# 9 Layout

## 9.1 Layout Guidelines

- Pullup resistors should be connected between the flag output pins and a positive input supply, usually VCC. An independent flag supply may also be used. These resistors should be placed as close as possible to the Simple Power Supply Sequencer and the flag supply. Minimal trace length is recommended to make the connections. A typical value for the pullup resistors is 100 kΩ.

- For very tight sequencing requirements, minimal and equal trace lengths should be used to connect the flag outputs to the desired inputs. This will reduce any propagation delay and timing errors between the flag outputs along the line.

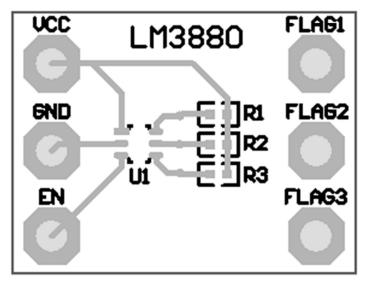

## 9.2 Layout Example

Figure 9-1 and Figure 9-2 are layout examples for the LM3880-Q1. These examples are taken from the LM3880-Q1EVAL.

Figure 9-1. LM3880-Q1 Top

Figure 9-2. LM3880-Q1 Bottom

## **10 Device and Documentation Support**

#### **10.1 Device Support**

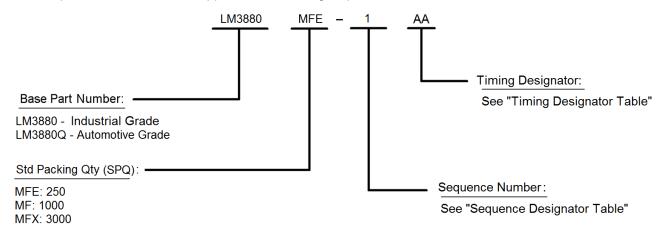

#### 10.1.1 Device Nomenclature

The list of parts available to order appear in the Package Option Addendum.

#### Figure 10-1. Device Nomenclature

#### Table 10-1. Sequence Designator Table (1)

| SEQUENCE NUMBER | FLAG ORDER |            |  |  |  |  |  |  |

|-----------------|------------|------------|--|--|--|--|--|--|

| SEQUENCE NUMBER | POWER UP   | POWER DOWN |  |  |  |  |  |  |

| 1               | 1 - 2 - 3  | 3 - 2 - 1  |  |  |  |  |  |  |

| 2               | 1 - 2 - 3  | 3 - 1 - 2  |  |  |  |  |  |  |

| 3               | 1 - 2 - 3  | 2 - 3 - 1  |  |  |  |  |  |  |

| 4               | 1 - 2 - 3  | 2 - 1 - 3  |  |  |  |  |  |  |

| 5               | 1 - 2 - 3  | 1 - 3 - 2  |  |  |  |  |  |  |

| 6               | 1 - 2 - 3  | 1 - 2 - 3  |  |  |  |  |  |  |

|                 |            |            |  |  |  |  |  |  |

(1) See and Figure 6-2.

### Table 10-2. Timing Designator Table (1)

| TIMING     | DELAYS (ms)     |                 |                 |                 |                 |                 |  |  |  |  |  |

|------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|--|--|--|--|--|

| DESIGNATOR | t <sub>d1</sub> | t <sub>d2</sub> | t <sub>d3</sub> | t <sub>d4</sub> | t <sub>d5</sub> | t <sub>d6</sub> |  |  |  |  |  |

| AA         | 10              | 10              | 10              | 10              | 10              | 10              |  |  |  |  |  |

| AB         | 30              | 30              | 30              | 30              | 30              | 30              |  |  |  |  |  |

| AC         | 60              | 60              | 60              | 60              | 60              | 60              |  |  |  |  |  |

| AD         | 120             | 120             | 120             | 120             | 120             | 120             |  |  |  |  |  |

| AE         | 2               | 2               | 2               | 2               | 2               | 2               |  |  |  |  |  |

| AF         | 16              | 16              | 16              | 16              | 16              | 16              |  |  |  |  |  |

(1) See and Figure 6-2.

#### **10.2 Community Resources**

#### **10.3 Trademarks**

All trademarks are the property of their respective owners.

# Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

## **PACKAGING INFORMATION**

| Orderable Device    | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|---------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| LM3880QMF-1AA/NOPB  | ACTIVE        | SOT-23       | DBV                | 6    | 1000           | RoHS & Green    | SN                                   | Level-1-260C-UNLIM   | -40 to 125   | F27A                    | Samples |

| LM3880QMF-1AB/NOPB  | ACTIVE        | SOT-23       | DBV                | 6    | 1000           | RoHS & Green    | SN                                   | Level-1-260C-UNLIM   | -40 to 125   | F28A                    | Samples |

| LM3880QMF-1AC/NOPB  | ACTIVE        | SOT-23       | DBV                | 6    | 1000           | RoHS & Green    | SN                                   | Level-1-260C-UNLIM   | -40 to 125   | F29A                    | Samples |

| LM3880QMF-1AD/NOPB  | ACTIVE        | SOT-23       | DBV                | 6    | 1000           | RoHS & Green    | SN                                   | Level-1-260C-UNLIM   | -40 to 125   | F30A                    | Samples |

| LM3880QMF-1AE/NOPB  | ACTIVE        | SOT-23       | DBV                | 6    | 1000           | RoHS & Green    | SN                                   | Level-1-260C-UNLIM   | -40 to 125   | F24A                    | Samples |

| LM3880QMF-1AF/NOPB  | ACTIVE        | SOT-23       | DBV                | 6    | 1000           | RoHS & Green    | SN                                   | Level-1-260C-UNLIM   | -40 to 125   | F32A                    | Samples |

| LM3880QMFE-1AA/NOPB | ACTIVE        | SOT-23       | DBV                | 6    | 250            | RoHS & Green    | SN                                   | Level-1-260C-UNLIM   | -40 to 125   | F27A                    | Samples |

| LM3880QMFE-1AB/NOPB | ACTIVE        | SOT-23       | DBV                | 6    | 250            | RoHS & Green    | SN                                   | Level-1-260C-UNLIM   | -40 to 125   | F28A                    | Samples |

| LM3880QMFE-1AC/NOPB | ACTIVE        | SOT-23       | DBV                | 6    | 250            | RoHS & Green    | SN                                   | Level-1-260C-UNLIM   | -40 to 125   | F29A                    | Samples |

| LM3880QMFE-1AD/NOPB | ACTIVE        | SOT-23       | DBV                | 6    | 250            | RoHS & Green    | SN                                   | Level-1-260C-UNLIM   | -40 to 125   | F30A                    | Samples |

| LM3880QMFE-1AE/NOPB | ACTIVE        | SOT-23       | DBV                | 6    | 250            | RoHS & Green    | SN                                   | Level-1-260C-UNLIM   | -40 to 125   | F24A                    | Samples |

| LM3880QMFE-1AF/NOPB | ACTIVE        | SOT-23       | DBV                | 6    | 250            | RoHS & Green    | SN                                   | Level-1-260C-UNLIM   | -40 to 125   | F32A                    | Samples |

| LM3880QMFX-1AA/NOPB | ACTIVE        | SOT-23       | DBV                | 6    | 3000           | RoHS & Green    | SN                                   | Level-1-260C-UNLIM   | -40 to 125   | F27A                    | Samples |

| LM3880QMFX-1AB/NOPB | ACTIVE        | SOT-23       | DBV                | 6    | 3000           | RoHS & Green    | SN                                   | Level-1-260C-UNLIM   | -40 to 125   | F28A                    | Samples |

| LM3880QMFX-1AC/NOPB | ACTIVE        | SOT-23       | DBV                | 6    | 3000           | RoHS & Green    | SN                                   | Level-1-260C-UNLIM   | -40 to 125   | F29A                    | Samples |

| LM3880QMFX-1AD/NOPB | ACTIVE        | SOT-23       | DBV                | 6    | 3000           | RoHS & Green    | SN                                   | Level-1-260C-UNLIM   | -40 to 125   | F30A                    | Samples |

| LM3880QMFX-1AE/NOPB | ACTIVE        | SOT-23       | DBV                | 6    | 3000           | RoHS & Green    | SN                                   | Level-1-260C-UNLIM   | -40 to 125   | F24A                    | Samples |

| LM3880QMFX-1AF/NOPB | ACTIVE        | SOT-23       | DBV                | 6    | 3000           | RoHS & Green    | SN                                   | Level-1-260C-UNLIM   | -40 to 125   | F32A                    | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

# PACKAGE OPTION ADDENDUM

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design. **PREVIEW:** Device has been announced but is not in production. Samples may or may not be available. **OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(<sup>5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF LM3880-Q1 :

• Catalog : LM3880

NOTE: Qualified Version Definitions:

• Catalog - TI's standard catalog product

Texas

STRUMENTS

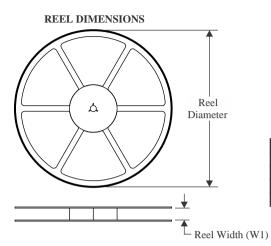

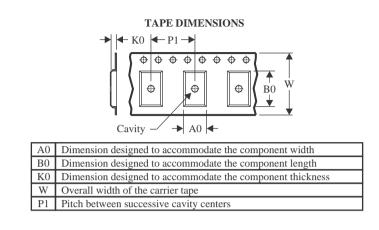

### TAPE AND REEL INFORMATION

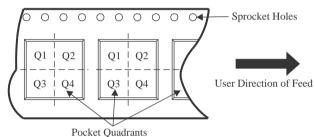

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| Device              | Package<br>Type                         | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter | Reel<br>Width | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------------|-----------------------------------------|--------------------|------|------|------------------|---------------|------------|------------|------------|------------|-----------|------------------|

|                     | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | g                  |      |      | (mm)             | W1 (mm)       | ` '        | ()         | ()         | ()         | ()        |                  |

| LM3880QMF-1AA/NOPB  | SOT-23                                  | DBV                | 6    | 1000 | 178.0            | 8.4           | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LM3880QMF-1AB/NOPB  | SOT-23                                  | DBV                | 6    | 1000 | 178.0            | 8.4           | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LM3880QMF-1AC/NOPB  | SOT-23                                  | DBV                | 6    | 1000 | 178.0            | 8.4           | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LM3880QMF-1AD/NOPB  | SOT-23                                  | DBV                | 6    | 1000 | 178.0            | 8.4           | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LM3880QMF-1AE/NOPB  | SOT-23                                  | DBV                | 6    | 1000 | 178.0            | 8.4           | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LM3880QMF-1AF/NOPB  | SOT-23                                  | DBV                | 6    | 1000 | 178.0            | 8.4           | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LM3880QMFE-1AA/NOPB | SOT-23                                  | DBV                | 6    | 250  | 178.0            | 8.4           | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LM3880QMFE-1AB/NOPB | SOT-23                                  | DBV                | 6    | 250  | 178.0            | 8.4           | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LM3880QMFE-1AC/NOPB | SOT-23                                  | DBV                | 6    | 250  | 178.0            | 8.4           | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LM3880QMFE-1AD/NOPB | SOT-23                                  | DBV                | 6    | 250  | 178.0            | 8.4           | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LM3880QMFE-1AE/NOPB | SOT-23                                  | DBV                | 6    | 250  | 178.0            | 8.4           | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LM3880QMFE-1AF/NOPB | SOT-23                                  | DBV                | 6    | 250  | 178.0            | 8.4           | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LM3880QMFX-1AA/NOPB | SOT-23                                  | DBV                | 6    | 3000 | 178.0            | 8.4           | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LM3880QMFX-1AB/NOPB | SOT-23                                  | DBV                | 6    | 3000 | 178.0            | 8.4           | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LM3880QMFX-1AC/NOPB | SOT-23                                  | DBV                | 6    | 3000 | 178.0            | 8.4           | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LM3880QMFX-1AD/NOPB | SOT-23                                  | DBV                | 6    | 3000 | 178.0            | 8.4           | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

17-Oct-2022

| Device              | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM3880QMFX-1AE/NOPB | SOT-23          | DBV                | 6 | 3000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LM3880QMFX-1AF/NOPB | SOT-23          | DBV                | 6 | 3000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

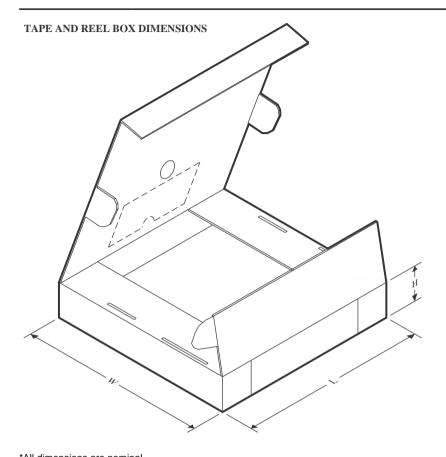

# PACKAGE MATERIALS INFORMATION

17-Oct-2022

| Device              | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM3880QMF-1AA/NOPB  | SOT-23       | DBV             | 6    | 1000 | 208.0       | 191.0      | 35.0        |

| LM3880QMF-1AB/NOPB  | SOT-23       | DBV             | 6    | 1000 | 208.0       | 191.0      | 35.0        |

| LM3880QMF-1AC/NOPB  | SOT-23       | DBV             | 6    | 1000 | 208.0       | 191.0      | 35.0        |

| LM3880QMF-1AD/NOPB  | SOT-23       | DBV             | 6    | 1000 | 208.0       | 191.0      | 35.0        |

| LM3880QMF-1AE/NOPB  | SOT-23       | DBV             | 6    | 1000 | 208.0       | 191.0      | 35.0        |

| LM3880QMF-1AF/NOPB  | SOT-23       | DBV             | 6    | 1000 | 208.0       | 191.0      | 35.0        |

| LM3880QMFE-1AA/NOPB | SOT-23       | DBV             | 6    | 250  | 208.0       | 191.0      | 35.0        |

| LM3880QMFE-1AB/NOPB | SOT-23       | DBV             | 6    | 250  | 208.0       | 191.0      | 35.0        |

| LM3880QMFE-1AC/NOPB | SOT-23       | DBV             | 6    | 250  | 208.0       | 191.0      | 35.0        |

| LM3880QMFE-1AD/NOPB | SOT-23       | DBV             | 6    | 250  | 208.0       | 191.0      | 35.0        |

| LM3880QMFE-1AE/NOPB | SOT-23       | DBV             | 6    | 250  | 208.0       | 191.0      | 35.0        |

| LM3880QMFE-1AF/NOPB | SOT-23       | DBV             | 6    | 250  | 208.0       | 191.0      | 35.0        |

| LM3880QMFX-1AA/NOPB | SOT-23       | DBV             | 6    | 3000 | 208.0       | 191.0      | 35.0        |

| LM3880QMFX-1AB/NOPB | SOT-23       | DBV             | 6    | 3000 | 208.0       | 191.0      | 35.0        |

| LM3880QMFX-1AC/NOPB | SOT-23       | DBV             | 6    | 3000 | 208.0       | 191.0      | 35.0        |

| LM3880QMFX-1AD/NOPB | SOT-23       | DBV             | 6    | 3000 | 208.0       | 191.0      | 35.0        |

| LM3880QMFX-1AE/NOPB | SOT-23       | DBV             | 6    | 3000 | 208.0       | 191.0      | 35.0        |

| LM3880QMFX-1AF/NOPB | SOT-23       | DBV             | 6    | 3000 | 208.0       | 191.0      | 35.0        |

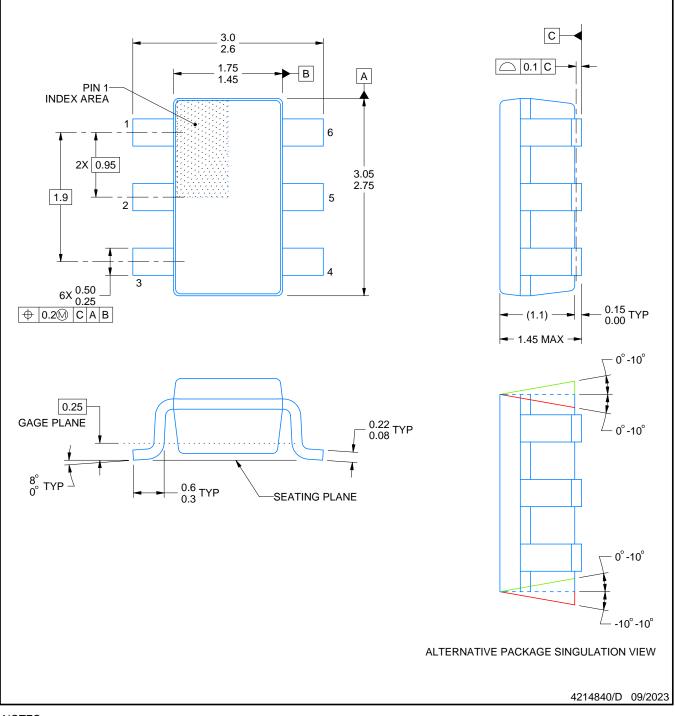

# **DBV0006A**

# **PACKAGE OUTLINE**

# SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.25 per side.

- 4. Leads 1,2,3 may be wider than leads 4,5,6 for package orientation.

- 5. Refernce JEDEC MO-178.

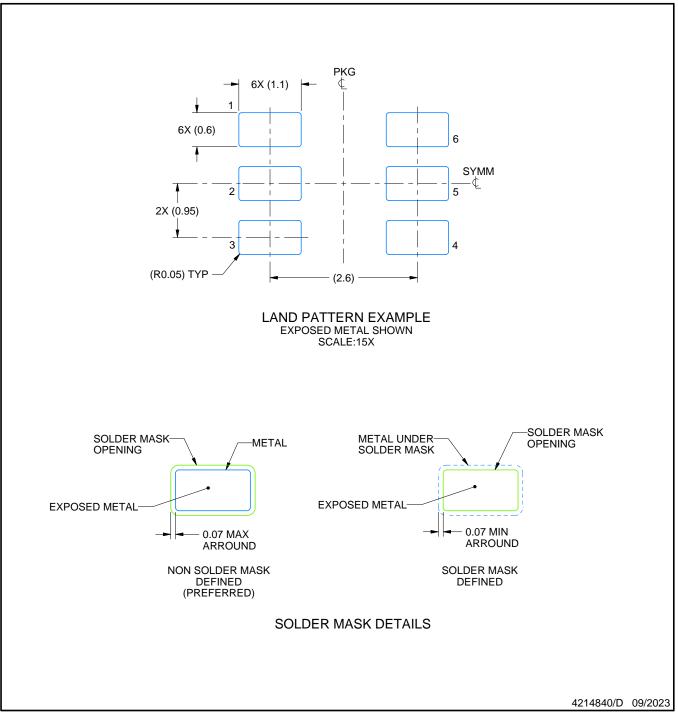

# **DBV0006A**

# **EXAMPLE BOARD LAYOUT**

# SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

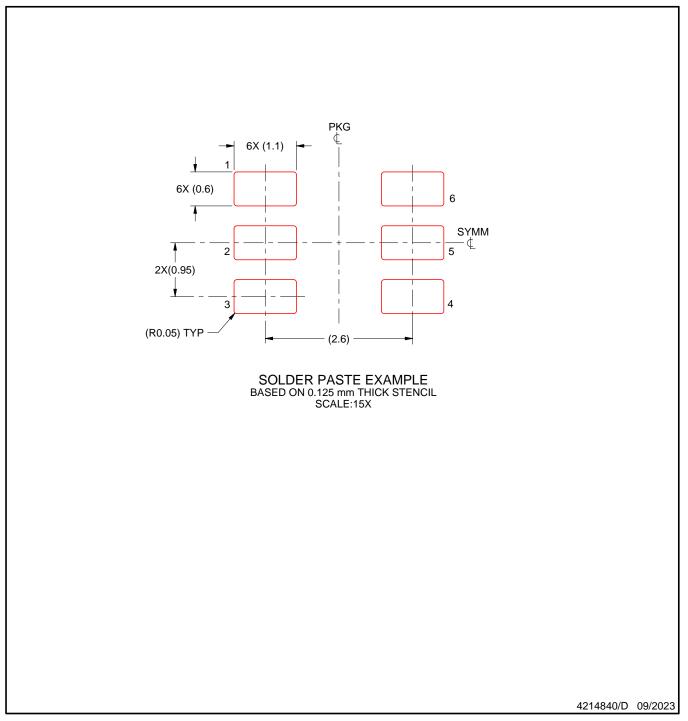

# **DBV0006A**

# **EXAMPLE STENCIL DESIGN**

# SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated