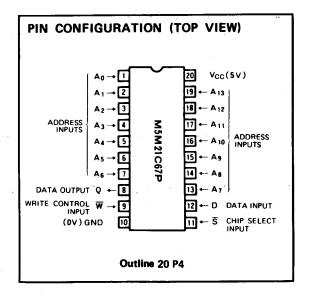

# M5M21C67P-45, -55

16384-BIT (16384-WORD BY 1-BIT) CMOS STATIC RAM

### DESCRIPTION

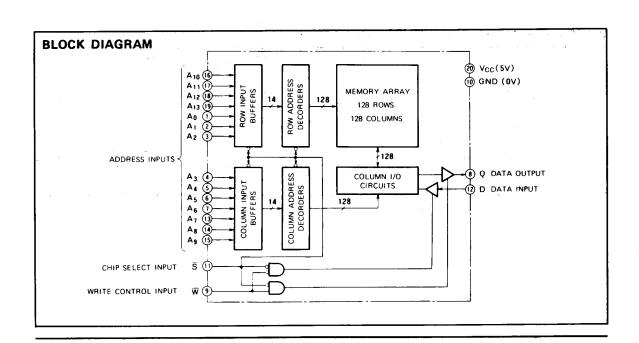

This is a family of 16384-word by 1-bit static RAMs, fabricated with the high-performance CMOS silicon-gate MOS process and designed for high-speed application. These devices operate on a single 5V supply, and are directly TTL compatible. They include a power-down feature as well.

### **FEATURES**

- Fast access time

M5M21C67P-45 ..... 45 ns (max)

M5M21C67P-55 ..... 55 ns (max)

- Low power dissipation Active ................200 mW (typ)

Stand by ............................... μW (typ)

- Power down by S

- Single 5V power supply

- Fully static operation

Requires neither external clock nor refreshing

- All inputs and output are directly TTL compatible

- Easy memory expansion by chip-select (S) input

#### **APPLICATION**

High-speed memory systems

### **FUNCTION**

A write operation is executed during the  $\overline{S}$  low and  $\overline{W}$  low overlap time. In this period, address signals must be stable. When  $\overline{W}$  is low, the Q terminal is maintained in the high impedance state, so it is possible to connect D and Q terminals directly.

In a read operation, after setting  $\overline{W}$  to high, and  $\overline{S}$  to low if the address signals are stable, the data is available at the Q terminal.

When  $\overline{S}$  is high, the chip is in the non-selectable state, disabling both reading and writing. In this case the output is in the floating (high-impedance) state, useful for ORties with other devices.

Signal  $\overline{S}$  controls the power-down feature. When  $\overline{S}$  goes high, power dissipation is reduced extremely. The access time from  $\overline{S}$  is equivalent to the address access time.

### 16384-BIT (16384-WORD BY 1-BIT) CMOS STATIC RAM

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol         | Parameter                 | Conditions          | Ratings              | Unit |  |

|----------------|---------------------------|---------------------|----------------------|------|--|

| Vcc            | Supply voltage            |                     | -3.5*~7              | ٧    |  |

| Vi             | Input voltage             | With respect to GND | -3.5*-7              | V    |  |

| V <sub>0</sub> | Output voltage            |                     | -3.5 <sup>*</sup> ~7 | V    |  |

| Pd             | Maximum power dissipation |                     | 1                    | w    |  |

| Topr           | Operating temperature     |                     | -10~85               | ·c   |  |

| Tstg           | Storage temperature       |                     | -65~150              | •c   |  |

<sup>\*</sup> Pulse width = 20 ns, DC: -0.5V

### DC ELECTRICAL CHARACTERISTICS ( $T_a = 0 \sim 70^{\circ}\text{C}$ , $V_{CC} = 5V \pm 10\%$ , unless otherwise noted)

| C              | Parameter                           |                                                                   |                                                    |       |                      |     |      |

|----------------|-------------------------------------|-------------------------------------------------------------------|----------------------------------------------------|-------|----------------------|-----|------|

| Symbol         |                                     | lest condit                                                       | Test conditions                                    |       |                      | Max | Unit |

| VIH            | High-level input voltage            |                                                                   | 2.2                                                |       | V <sub>CC</sub> +0.3 | V   |      |

| VIL            | Low-level input voltage             |                                                                   |                                                    | 3*    |                      | 0.8 | V    |

| Vон            | High-level output voltage           | I <sub>OH</sub> = 4 mA                                            | 2.4                                                |       |                      | V   |      |

| VoL            | Low-level output voltage            | I <sub>OL</sub> = 8 mA                                            |                                                    |       | 0.4                  | V   |      |

| I <sub>1</sub> | Input current                       | V <sub>1</sub> =0~5.5V                                            |                                                    | -     | 10                   | μΑ  |      |

| loz (          | Off-state output current            | V <sub>I(\$)</sub> =2.2V, V <sub>O</sub> =0                       |                                                    |       | 50                   | μА  |      |

|                | Supply current from V <sub>CC</sub> | V <sub>I</sub> (S)=0.8V                                           | DC                                                 |       | 25                   | 50  | mA   |

| ICC1           |                                     | Output open                                                       | AC                                                 |       |                      | 80  | шА   |

| I CC2          | Stand by current                    | V <sub>i(S)</sub> =2.2V Other V                                   | V <sub>I</sub> (S)=2.2V Other V <sub>I</sub> =2.2V |       |                      | 20  | mA   |

| 1003           | Stand by current                    | $V_{i}(\bar{s}) \ge V_{CC} - 0.2V$ ,<br>Other $V_{i} \le 0.2V$ or |                                                    | 0.001 | 2                    | mA  |      |

| C <sub>1</sub> | Input capacitance                   | V <sub>I</sub> =GND, V <sub>I</sub> =25mVr                        |                                                    |       | 5                    | pF  |      |

| Co             | Output capacitance                  | V <sub>O</sub> =GND, V <sub>O</sub> =25 mV                        |                                                    |       | 6                    | ρF  |      |

Note 1. Current flow into an IC is positive, out is negative.

## SWITCHING CHARACTERISTICS (FOR READ CYCLE) ( $T_a = 0 \sim 70^{\circ}C$ , $V_{CC} = 5V \pm 10\%$ , unless otherwise noted)

| Symbol              | Parameter                                  | M5I | M5M21C67P-45 |     |     | M5M21C67P-55 |     |      |

|---------------------|--------------------------------------------|-----|--------------|-----|-----|--------------|-----|------|

|                     |                                            | Min | Тур          | Max | Min | Тур          | Max | Unit |

| tor                 | Read cycle time                            | 45  |              |     | 55  |              |     | ns   |

| ta(A)               | Address access time                        |     |              | 45  |     |              | 55  | ns   |

| ta(S)               | Chip select access time                    |     |              | 45  |     |              | 55  | ns   |

| t <sub>V(A)</sub>   | Data valid time after address              | 5   |              |     | 5   |              |     | ns   |

| t <sub>en(S)</sub>  | Output enable time after chip selection    | 10  |              |     | 10  |              |     | ns   |

| t <sub>dis(s)</sub> | Output disable time after chip deselection | 0   |              | 20  | -0  |              | 25  | ns   |

| t <sub>PU</sub>     | Power-up time after chip selection         | 0   |              |     | . 0 |              |     | ns   |

| t <sub>PD</sub>     | Power down time after chip deselection     | -   |              | 45  | T - |              | 55  | ns   |

<sup>\*</sup> Pulse width = 20 ns, DC: -0.5V

# M5M21C67P-45, -55

16384-BIT (16384-WORD BY 1-BIT) CMOS STATIC RAM

# TIMING REQUIREMENTS (FOR WRITE CYCLE) ( $T_a = 0 \sim 70^{\circ}\text{C}$ , $V_{CC} = 5 \text{V} \pm 10\%$ , unless otherwise noted)

| Symbol              | Parameter                                       | M51 | M5M21C67P-45 |     |     | M5M21C67P-55 |                                              |      |

|---------------------|-------------------------------------------------|-----|--------------|-----|-----|--------------|----------------------------------------------|------|

|                     |                                                 | Min | Тур          | Max | Min | Тур          | Max                                          | Unit |

| t <sub>cw</sub>     | Write cycle time                                | 45  |              | Ī   | 55  |              |                                              | ns   |

| t <sub>su(s)</sub>  | Chip select setup time                          | 35  |              |     | 40  | <u></u>      |                                              | ns   |

| tsu(A)              | Address setup time 1 (W CONTROL)                | 0   |              |     | 0_  | Ĺ            | <u></u> .                                    | ns   |

| t su (A)2           | Address setup time 2 (\$\overline{S}\$ CONTROL) | 0   |              |     | 0   |              | <u>.                                    </u> | ns   |

| t <sub>w(w)</sub>   | Write pulse width                               | 25  |              |     | 30  |              |                                              | ns   |

| t <sub>rec(w)</sub> | Write recovery time                             | 0   |              |     | 0   |              |                                              | ns   |

| t <sub>su(D)</sub>  | Data setup time                                 | 25  |              |     | 25  | L            | <u> </u>                                     | ns   |

| th (D)              | Data hold time                                  | 0   |              |     | 0   | 1            |                                              | ns   |

| tdis(w)             | Output disable time after W low                 | 0   |              | 15  | 0   |              | 20                                           | ns   |

| ten(w)              | Output enable time after W high                 | 0   |              |     | 0   |              |                                              | ns   |

| tsu (A.WIA)         | Address to W high                               | 35  |              |     | 40  |              |                                              | ns   |

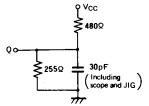

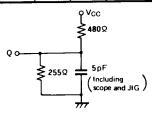

### CONDITIONS

Input pulse levels . . . . . . . . . . . . 0 to 3V Input rise and fall time ......... 5ns Input timing reference level ......... 1.5V Output timing reference level . . . . . .  $0.8V \sim 2V$ Output loads . . . . . . . . . . . . Fig. 1, Fig. 2

Fig. 1 Output load

Fig. 2 Output load for ten, tdis

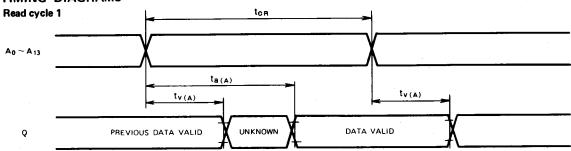

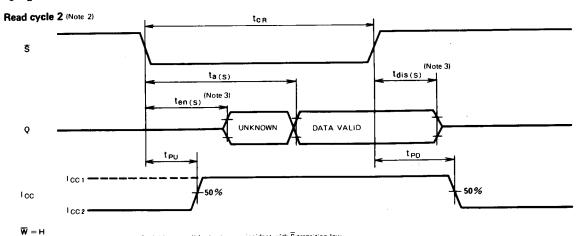

# TIMING DIAGRAMS

$\overline{\mathbf{w}} = \mathbf{H}$

Note 2. Addresses valid prior to or coincident with  $\overline{\mathbb{S}}$  transition low.

Transition is measured ±500mV from steady state voltage with specified loading in Figure 2.

### 16384-BIT (16384-WORD BY 1-BIT) CMOS STATIC RAM

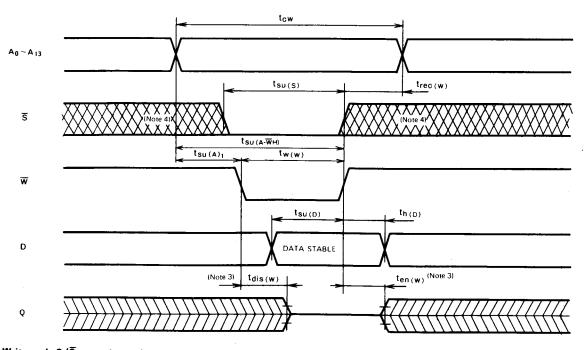

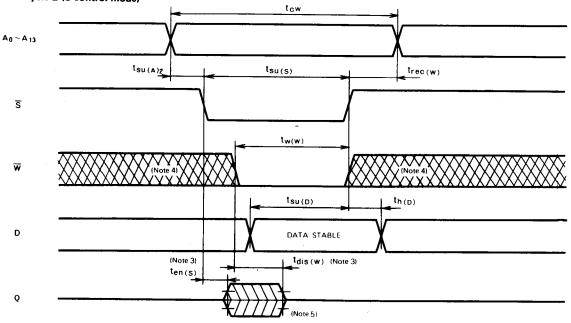

### **TIMING DIAGRAMS**

### Write cycle 1 (W control mode)

### Write cycle 2 (\$\overline{S}\$ control mode)

Note 4. Hatching indicates the state is don't care.

<sup>5.</sup> When the falling edge of  $\overline{W}$  is simultaneous or prior to the falling edge of  $\overline{S}$ , the output is maintained in the high impedance,